3151

Изобретение относится к вычислительной технике и может быть использовано в качестве входного преобразователя информации, задаваемого . потоком импульсов низкой или инфра- низкой частоты, а также составной части частотно-импульсных вычислительных устройств для информационно- измерительных систем, работающих с частотными датчиками.

Цель изобретения - повышение быстродействия преобразования.

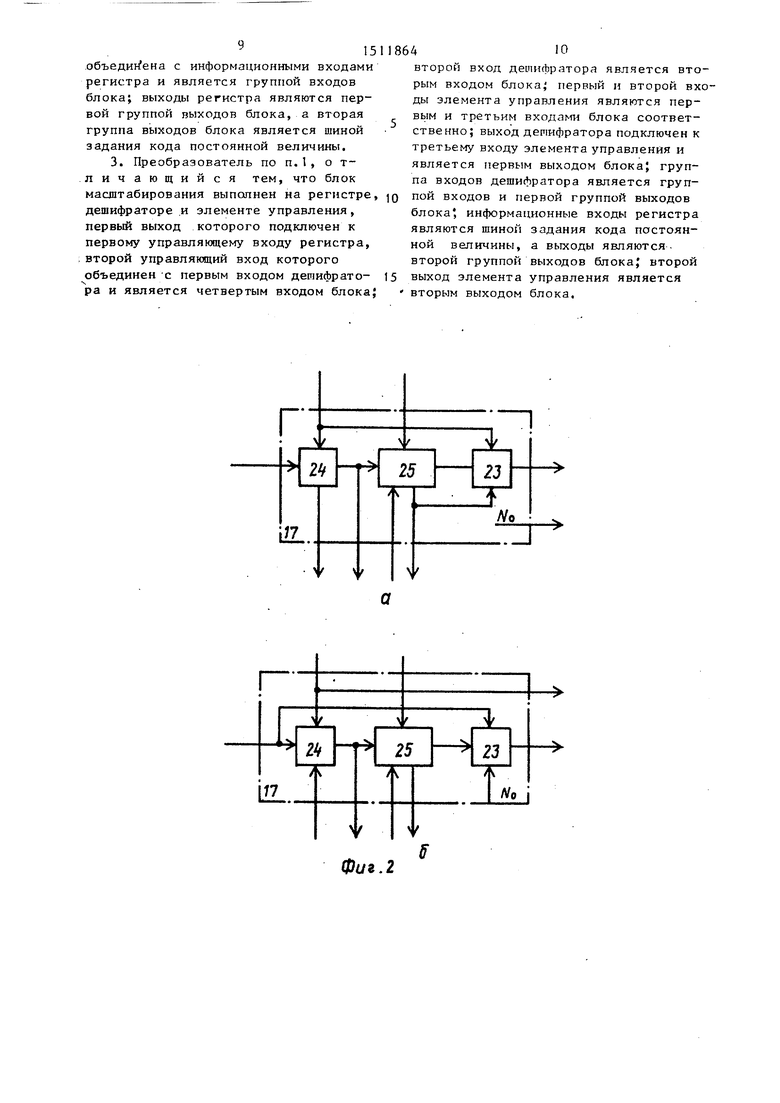

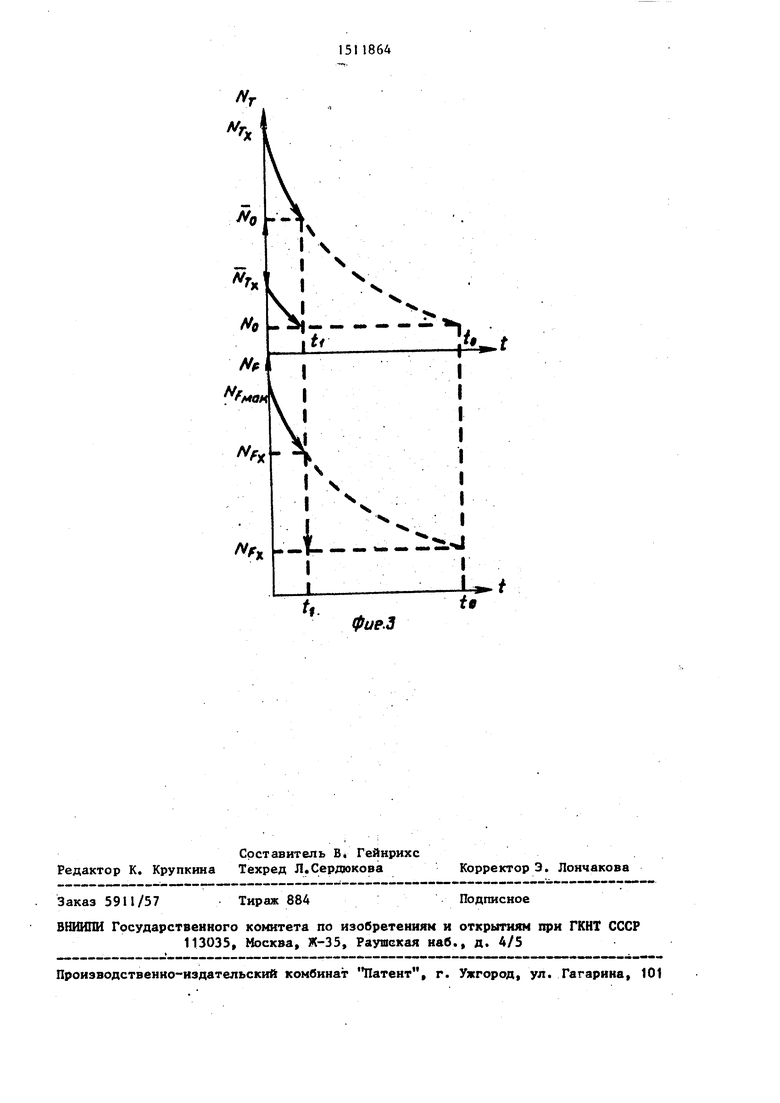

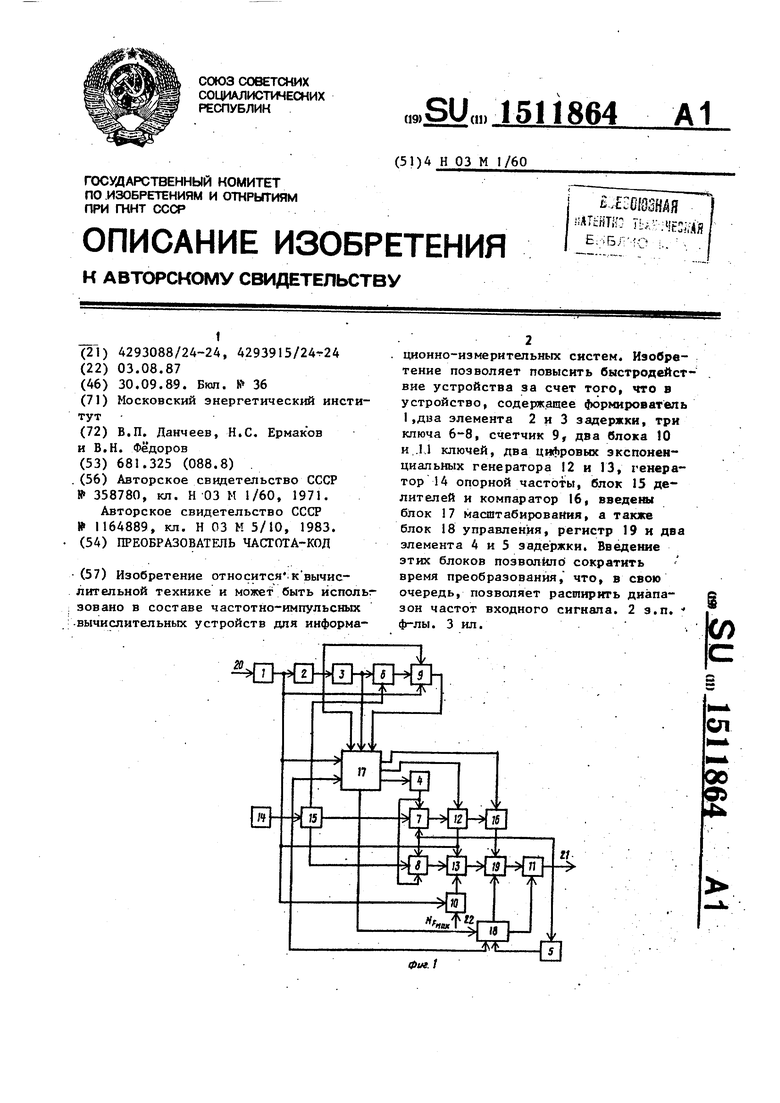

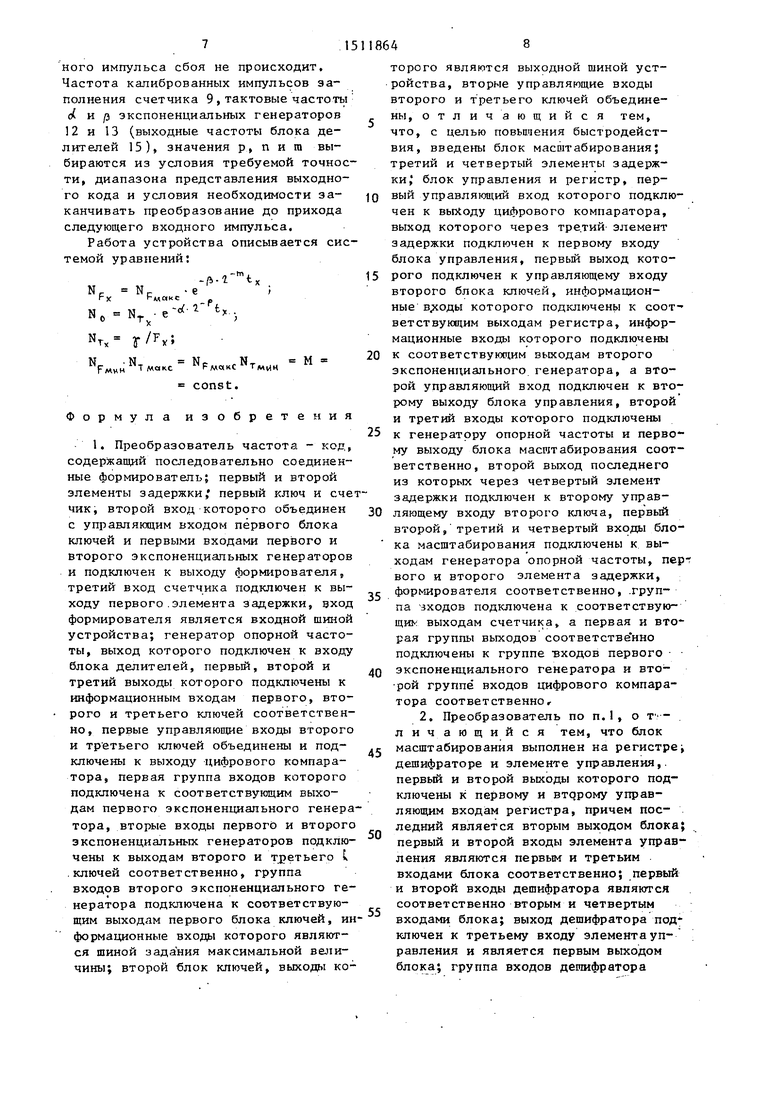

На фиг.1 представлена структурная схема устройства; на фиг.2 - ва- рианты схемы блока масштабирования; на фиг.З - временная диаграмма, ип- люстрирующая работу второго такта преобразователя.

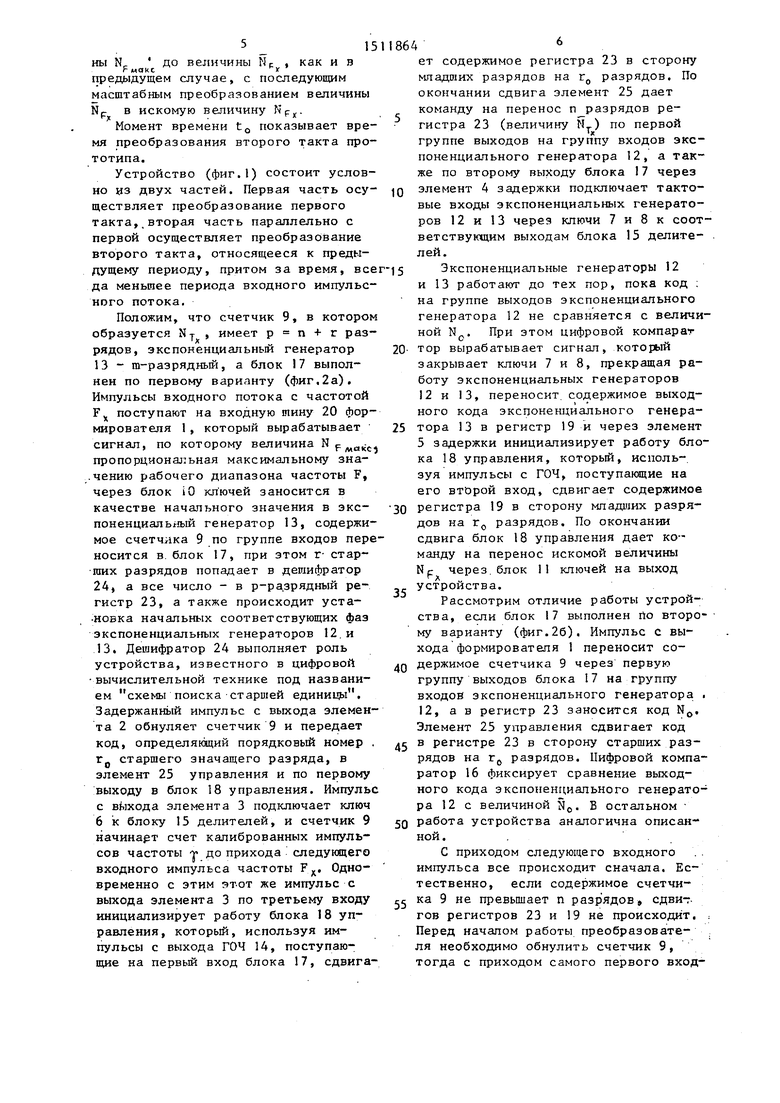

Устройство содержит формирователь 1, элементы 2-5 задержки, ключи 6-8, счетчик 9, блоки 10 и 11 ключей, цифровые экспоненциальные генераторы 12 и 13, генератор 14 опорной частоты (ГОЧ), блок 15 делителей, цифровой компаратор 16, блок 17 масштабирования, блок 18 управления и регистр 19, а также входную и выхоную шины 20 и 21 соответственно и шину 22 задания кода максимальной величины N р л дксБлок 17 масштабирования (фиг.2) выполнен на регистре 23, дешифраторе 24 и элементе 25 управления.

По варианту, представленному на фиг.2а, первый и второй выходы элемента 25 управления подключены к первому и второму входам регистра 23, причем последний является вторым выходом блока, первый и второй входы элемента 25 управления являются первым и третьим входами блока соответственно, первый и второй входы дешифратора являются соответственно вторым и четвертым входами блока, выход дешифратора 24 подключен к . третьему входу элемента 25 управления и является первым выходом блока, группа входов дешифратора 24 объединена с группой входов регистра 23 и является группой входов блока, выходы регистра 23 являются первой группой выходов блока, а вторая группа выходов блока является шиной задания кода постоянной величины N.

По варианту,представленному на фиг.2б, в блоке 17 масштабирования первый выход элемента управления 25 подключен к первому входу регистра

23, второй вход объединен с первым входом дешифратора 24 и является четвертым входом блока, второй вход , дешифратора 24 является вторым входом блока, первый и-второй входы элемента 25 управления являются первым и третьим входами блока соответственно, выход дешифратора 24 подключен к третьему входу элемента 25 управления и является первым выходом блока, группа входов дешифратора 24 является группой входов и первой группой выходов блока, группа входов регистра 23 является шиной задания кода постоянной величины Ng, а выходы являются второй группой выходов блока, второй выход -элемента 25 управления является вторым выходом блока.

Устройство представляет собой двухтактный преобразователь калиброванного периода определяемой частоты и функционирует следукщим образом.

В первом такте определяется величина NY, пропорциональная периоду Ту входного импульсного потока путем подсчета импульсов калиброванной частоты, заполняющих период между двумя соседними входными импульсами. Вр втором такте происходит гиперболическое преобразование величины N-p в искомую величину Nр, пропорциональную входной частоте (фиг.З). В зависимости от варианта выполнения блока масштабирования указанное преобразование может выполняться двумя альтернативными способами. При этом полагается, что величина NT представляется числом разрядов р, превышающим некоторое значение п (р п г) .

Тогда в соответствии с фиг.2а, во втором такте происходит сначала масштабное преобразование величины N в величину N-r N 7., затем экспоненциальное интерполирование величины N-p до величины NO и одно- временнре экспоненциальное интерполирование ; величины N р до величины УГр (момент времени t на фиг.З) с последующим обратным масштабным преобразованием величины N р в иско- мую величину N р, 2 С

В соответствии с фиг.2б во втором такте происходит сначала масштабное преобразование величины N до величины NO N - 2, потом экспоненциальное интерполирование величины N- до величины N и одновременно экспоненциальное интерполирование величи5 15

ны N.. до величины Nr , как и в

F мокс if

предыдущем случае, с последующим масштабным преобразованием величины NP в искомую величину Np.

Момент времени t показывает время преобразования второго такта прототипа.

Устройство (фиг.1) состоит условно из двух частей. Первая часть осуществляет преобразование первого такта,,вторая часть параллельно с первой осуществляет преобразование второго такта, относящееся к предыдущему периоду, притом за время, все да меньшее периода входного импульсного потока.

Положим, что счетчик 9, в котором образуется Nj , имеет р п + г разрядов, экспоненциальный генератор 13 - т-разрядный, а блок 17 выполнен по первому варианту (фиг,2а), Импульсы входного потока с частотой F поступают на входную тину 20 формирователя 1 , который вырабатывает сигнал, по которому величина Np., пропорционал ьная максимальному зна.чению рабочего диапазона частоты F, через блок iO кп ючей заносится в качестве начального значения в экспоненциальный генератор 13, содержимое счетчика 9 по группе входов переносится в. блок 17, при этом г- старгаих разрядов попадает в дешифратор 24, а все число - в р-разрядный регистр 23, а также происходит установка начальных соответствующих фаз экспоненциальных генераторов 12. и 13. Дешифратор 24 выполняет роль устройства, известного в цифровой

вычислительной технике под названием схемы поиска старшей едини19 1. Задержанной импульс с выхода элемента 2 обнуляет счетчик 9 и передает код, определяющий порядковый номер . старшего значащего разряда, в элемент 25 управления и по первому выходу в блок 18 управления. Импульс с выхода элемента 3 подключает ключ 6 к блоку 15 делителей, и счетчик 9 начинает счет калиброванных импуль сов частоты -v до прихода следующего входного импульса частоты F. Одновременно с этим этот же импульс с выхода элемента 3 по третьему входу инициализирует работу блока 18 управления, который, используя импульсы с выхода ГОЧ 14, поступающие на первый вход блока 17, сдвига864

ет содержимое регистра 23 в сторону младших разрядов на г разрядов. По окончании сдвига элемент 25 дает команду на перенос п разрядов регистра 23 (величину М) по первой группе выходов на группу входов экспоненциального генератора 12, а также по второму выходу блока 17 через

Q элемент 4 задержки подключает тактовые входы экспоненциальных генераторов 12 и 13 через ключи 7 и 8 к соответствующим выходам блока 15 делителей.

5Экспоненциальные генераторы 12

и 13 работают до тех пор, пока код : на группе выходов экспоненциального генератора 12 не сравняется с величиной Np. При этом цифровой компарат

0- тор вырабатывает сигнал, который

закрывает ключи 7 и 8, прекращая работу экспоненциальных генераторов 12 и 13, переносит, содержимое выходного кода экспоненциального генера5 тора 13 в регистр 19 и через элемент 5 задержки инициализирует работу блока 18 управления, который, исполь-. зуя импульсы с ГОЧ, поступающие на его второй вход, сдвигает содержимое

0 регистра 19 в сторону млади1их разрядов на Гд разрядов. По окончании сдвига блок 18 управления дает команду на перенос искомой величины Np через, блок 11 ключей на выход устройства.

Рассмотрим отличие работы устройства, если блок 17 выполнен По второ- му варианту (фиг.26), Импульс с выхода формирователя 1 переносит со0 держимое счетчика 9 через первую группу выходов блока 17 на группу входов экспоненциального генератора 12, а в регистр 23 заносится код N, Элемент 25 управления сдвигает код

д5 в регистре 23 в сторону старших разрядов на т разрядов. Пифровой компаратор 16 фиксирует сравнение выходного кода экспоненциального генератора 12 с величиной NO- Б остальном

Q работа устройства аналогична описанной.

С приходом следующего входного импульса все происходит сначала. Естественно, если содержимое счетчи5 ка 9 не превышает п разр ядов, сдви-. гов регистров 23 и 19 не происходит, , Перед начапом работы преобразователя необходимо обнулить счетчик 9, тогда с приходом самого первого вход5

ного импульса сбоя не происходит. Частота калиброванных импульсов заполнения счетчика 9 , тактовые частоть d к ft экспоненциальных генераторов 12 и 13 (выходные частоты блока делителей 15), значения р, п и га выбираются из условия требуемой точности, диапазона представления выходного кода и условия необходимости за- канчивать преобразование до прихода следующего входного импульса.

Работа устройства описывается системой уравнений:

N, N,

NC е

Ьмакс

-/i. -Р.

N,

N,..

FMWH fмакс

РмакС TMV(H

const.

м

Формула изобретения

1. Преобразователь частота - код, содержащий последовательно соединенные формирователь; первый и второй элементы задержки, первый ключ и счечик, второй вход которого объединен с ущ анляющим входом первого блока ключей и первыми входами первого и второго экспоненциальных генераторов и подключен к выходу формирователя, третий вход счетчика подключен к выходу первого.элемента задержки, дход формирователя является входной шиной устройства; генератор опорной частоты, выход которого подключен к входу блока делителей, первый, второй и третий выходы которого подключены к информационным входам первого, второго и третьего ключей соответственно, первые управляюпще входы второго и тр етьего ключей объединены и подключены к выходу цифрового компаратора, первая группа входов которого подключена к соответствующим выходам первого экспоненциального генератора, вторые входы первого и второго экспоненциальных генераторов подключены к выходам второго и третьего 1 .ключей соответственно, группа входов второго экспоненциального генератора подключена к соответствующим выходам первого блока ключей, ин формационные входы которого являются шиной задания максимальной величины; второй блок ключей, выходы ко

,

JQ

15

20

25

35

зо. 45

50

55

торого являются выходной шиной устройства, вторые управляющие входы второго и третьего ключей объединены, отличающийся тем, что, с целью повьйчения быстродействия, введены блок масштабирования; третий и четвертый элементы задержки, блок управления и регистр, первый управляющий вход которого подключен к выходу цифрового компаратора, выход которого через тре.тий- элемент задержки подключен к первому входу блока управления, первьй выход которого подключен к управляющему входу второго блока ключей, информационные врсоды которого подключены к соответствующим выходам регистра, информационные входы которого подклю1чены к соответствуюрщм выходам второго экспоненциального генератора, а второй управляющий вход подключен к второму выходу блока управления, второй и третий входы которого подключены к генератору опорной частоты и первому выходу блока масштабирования соответственно, второй выход последнего из которых через четвертый элемент задержки подключе1 к второму управляющему входу второго ключа, первьй второй, третий и четвертый входы блока масштабирования подключены к выходам генератора опорной частоты, пер-г вого и второго элемента задержки, формирователя соответственно, .группа зходов подключена к соответствующие выходам счетчика, а первая и вторая группы выходов соответстве нно подключены к группе входов первого экспоненциального генератора и вто- рой группе входов цифрового компаратора соответственно г

2. Преобразователь по п. 1 , о личающийся тем, что блок масштабирования выполнен на регистреj дешифраторе и элементе управления,, первый и второй выходы которого подключены к первому и BTQpOMy управляющим входам регистра, причем последний является вторым выходом блока; первый и второй входы элемента управления являются первым и третьим входами блока соответственно; первый и второй входы дешифратора являются соответственно вторым и четвертым входами блока; выход дешифратора под ключей к третьему входу элемента управления и является первым вьпсодом блока; группа входов дешифратора

9,5

объединена с информационными входами регистра и является группой входов блока; выходы регистра являются пер вой группой выходов блока, а вторая группа выходов блока является шиной задания кода постоянной величины.

3. Преобразователь по п.I, о т- л ич а ющи и с я тем, что блок масштабирования выполнен на регистре, дешифраторе .и элементе управления, первый выход которого подключен к первому управляющему входу регистра, :второй управляющий вход которого объединен с первым входом дешифратора и является четвертым входом блока;

10

второй вход дешифратора является вторым входом блока, гтервый и второй входы элемента управления являются первым и третьим входами блока соответственно; выход дешифратора подключен к третьему входу элемента управления и является первым выходом блока; группа входов дешифратора является группой входов и первой группой выходов блока информационные входы регистра являются шиной задания кода постоянной величины, а выходы являются- второй группой выходов блока второй

выход элемента управления является вторым выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь частота-код | 1987 |

|

SU1506553A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин с мультипликативной автокоррекцией | 1984 |

|

SU1185604A1 |

| Вероятностный интегрирующий преобразователь аналог-код | 1987 |

|

SU1441476A1 |

| Устройство для измерения механической скорости бурения | 1979 |

|

SU863843A1 |

| Умножитель частоты | 1980 |

|

SU868756A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| Преобразователь перемещения в код | 1982 |

|

SU1043701A1 |

| Устройство для контроля импульсных параметров магнитных сердечников | 1981 |

|

SU981908A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1102036A2 |

Изобретение относится к вычислительной технике и может быть использовано в составе частотно-импульсных вычислительных устройств для информационно-измерительных систем. Изобретение позволяет повысить быстродействие устройства за счет того, что в устройство, содержащее формирователь 1, два элемента 2 и 3 задержки, три ключа 6,7,8, счетчик 9, два блока 10 и 11 ключей, два цифровых экспоненциальных генератора 12 и 13, генератор 14 опорной частоты, блок 15 делителей и компаратор 16, введены блок 17 масштабирования, а также блок 18 управления, регистр 19 и два элемента 4 и 5 задержки. Введение этих блоков позволило сократить время преобразования, что, в свою очередь, позволяет расширить диапазон частот входного сигнала. 2 з.п. ф-лы.3 ил.

2

Ч/ V

25

IIL..

Фиг. 2

25

23

No i

NT

Т,

Составитель В Гейнрихс Редактор К. Крупкина Техред Л.Сердюкова

Заказ 5911/57

Тираж 884

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. А/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

фир.З

Корректор Э. Лончакова

Подписное

Авторы

Даты

1989-09-30—Публикация

1987-08-03—Подача