информационные выходы первого и второго блоков стековой памяти соединены соответственно с первым и вторым входами первого блока сравнения, выход сравнения которого соединен с первыми входами первого и второго элементов ИЛИ и со счетным входом второго счетчика, выход-несравнения первого блока сравнения соединен с вторым входом блока индикации, первый, второй и третий выходы дешифратора соединены соответственно с первым и вторым входами установки единицы и нуля триггера и с входами разрешения сравнения второго блока сравнения, второй выход дешифратора через элемент задержки соединен с вторым входом

седьмого элемента И, единичный выхед триг гера соединен с вторым входом второгв элемента И, информационные выходы первого счетчика и регистра соединены соответственно с первым и вторым информационными входами второго блока сравнения, выход сравнения которого соединен с вторыми входами первого и второго элементов ИЛИ, выход несравнения второго блока сравнения и выход переполнения первого счетчика соединены соответственно с третьим и четвертым входами блока индикации, выходы первого и второго элементов ИЛИ - соответственно с управляющими входами первого и второго блоков стековой памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля программно-аппаратных средств эвм | 1987 |

|

SU1513454A1 |

| Микропрограммное устройство для анализа программ | 1980 |

|

SU943729A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1522203A1 |

| Устройство для обработки выражений языков программирования | 1981 |

|

SU1016790A1 |

| Устройство для интерпретации выражений языков программирования | 1982 |

|

SU1078432A1 |

| Процессорный модуль | 1985 |

|

SU1343421A1 |

| УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ ОПЕРАТОРОВ | 1991 |

|

RU2011228C1 |

| УСТРОЙСТВО ОБУЧЕНИЯ ОПЕРАТОРОВ | 1997 |

|

RU2129734C1 |

| Устройство для программного управления технологическими процессами | 1987 |

|

SU1495746A1 |

| Устройство для определения кратчайшего пути на графе | 1983 |

|

SU1134944A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПРОГРАММ, содержащее первый счетчик, первый и второй элементы И, блок памяти и блок управления, содержащий элемент ИЛИ, блок элементов задержки и кнопку «Пуск, причем выход кнопки «Пуск соединен с первым входом блока элементов задержки и первым входом элемента ИЛИ, выход которого соединен с входом считывания блока памяти, первый выход блока элементов задержки блока управления соединен с первым входом первого элемента И, выход которого соединен с информационным входом первого счетчика, информационный выход блока памяти соединен с вторым входом первого элемента И, тактовый вход устройства соединен с первым входом второго элемента И, выход которого соединен со счетным входом первого счетчика, отличающееся тем, что, с целью повыщения достоверности контроля, в устройство введены третий, четвертый, пятый, шестой и седьмой элементы И, первый и второй элементы ИЛИ, первый и второй блоки стековой памяти, первый и второй блоки сравнения, регистр, блок индикации, триггер, элемент задержки, дешифратор и второй счетчик, а в блок управления - счетчик, дешифратор, триггер, элемент задержки, первый и второй элементы И, причем информационный выход блока памяти соединен с первыми входами третьего, четвертого, пятого и шестого элементов И, с входами дешифратора блока управления и первым входом первого элемента И блока управления, выход которого соединен с установочным входом счетчика блока управления, выходы счетчика блока управления и кнопки «Пуск соединены соответственно с нулевым и единичным входами триггера блока управления, единичный и нулевой выходы которого соединены соответственно с первым входом второго элемента И блока управления и с первым входом блока индикации, выход переполнения второго счетчика соединен со счетным входом счетчика блока управления и через элемент задержки блока управления - с вторым входом второго S элемента И блока управления, выход которого соединен с вторым входом элемента ИЛИ блока управления, первый, второй, третий, четвертый и пятый выходы дешифратора блока управления соединены соответственно с вторым, третьим, четвертым, пятым и шестым входами блока элементов задержки, блока управления, второй, третий, четвертый, пятый и шестой выходы которого соединены соответственно с вторым входом первого элемента И блока управления, ;о to с вторыми входами третьего, четвертого, пятого и шестого элементов И, первый, второй, третий, четвертый и пятый выходы дешифраО5 тора блока управления соединены соответСО ственно с третьим, четвертым, пятым, шестым и седьмым входами элемента ИЛИ блока управления, выходы третьего, четвертого, пятого и шестого элементов И соединены соответственно с информационным входом регистра, с информационным входом первого блока стековой памяти, с информационным входом второго счетчика и с информационным выходом устройства, информационный вход устройства соединен с входом дешифратора и первым входом седьмого элемента И, выход которого соединен с информационным входом второго блока стековой памяти.

1

Изобретение относится к вычислительной технике и может быть использовано в устройствах отладки программ, устройствах управления ходом выполнения программ и устройствах контроля правильности выполнения программ ЦВМ.

Известны устройства отладки программ, содержащие блок управления, наладочную оперативную память, блок обмена с внешними устройствами, блок формирования адреса. Под процессом отладки понимается проверка полученных на каждом шаге программы результатов с заранее вычисленными. С этой целью устройства функционируют как в автоматических, так и в наладочных режимах 1 и 2.

Однако известные устройства не отражают сам процесс проверки правил1; ности выполнения программ, не рассматривают возможность автоматического получения результатов проверки с учетом времени выполнения программы, в то время как вопрос проверки правильности функционирования программ становится все более актуальным в связи с возрастанием требований к надежности программного обеспечения.

Известно устройство для проверки блока микропрограммного управления, содержащее регистр команд, регистр адресов микрокоманд, дешифратор адреса микрокоманд, блок памяти микрокоманд, регистр микрокоманд, блок сравнения, блок времени 3.

Недостатком этого устройства является то, что оно требует для своей реализации либо дополнительные микрокоманды, либо дублирование некоторых микрокоманд в блоке памяти контрольных микрокоманд.

Кроме того, оценка правильности осуществляется сравнением лищь одного параметра, так как для контроля правильности выполнения переходов микропрограмм достаточно одного параметра.

Наиболее близким к изобретению по технической сущности является устройство для контроля времени выполнения программ, содержащее счетчик, вход и первый выход которого через вентили записи и вентили считывания соединены соответственно с первым входом и первым выходом устройства, схему управления, схемы ИЛИ, ИЛИ-НЕ,

0 ИСКЛЮЧАЮЩЕЕ ИЛИ и НЕ, триггер, второй, третий и четвертый входы устройства подключены соответственно к первому, второму и третьему входам схемы управления, выход которой подключен к первому входу

5 триггера, выход которого через первую схему ИЛИ-НЕ соединен со счетным входом счетчика и первыми входами второй и третьей схемы ИЛИ-НЕ, вторые входы которых через первую и вторую схемы НЕ соединены соответственно с вторым и пятым вхо0 дами устройства, выходы второй и третьей схем ИЛИ-НЕ подключены к соответствующим входам первой схемы ИЛИ-НЕ и схемы ИЛИ, выход которой подключен к второму выходу устройства, управляющие входы

5 вентилей записи и считывания подключены соответственно к выходу второй схемы ИЛИ- НЕ и выходу третьей схемы ИЛИ-НЕ, третий выход устройства соединен с вторым выходом счетчика, третий выход которого через схему ИСКЛЮЧАЮЩЕЕ ИЛИ подключен

к второму входу триггера, третий вход которого соединен с вторым входом устройства. Известное устройство засылает в счетчик код времени выполнения программы. Если до истечения этого промежутка времени в счетчик не записан код времени для нового цикла выполнения программ, то данная ситуация классифицируется как зацикливание, и

соответствующий сигнал поступает в блок контроля ЦВМ 4.

Недостатком известного устройства является то, что в программах возмо)Лио появление дефектов, которые не изменяют времени выполнения программы, искажая результат вычислений.

Цель изобретения - повышение достоверности диагностирования путем увеличения числа диагностируемых показателей, в число которых входят: время выполнения программы и совпадение результатов выполнения программы с эталонными результатами.

Цель достигается тем, что в устройство для контроля программ, содержащее первый счетчик, первый и второй элементы И, блок памяти и блок управления, содержащий элемент ИЛИ, блок элементов задержки и кнопку «Пуск, причем выход кнопки «Пуск соединен с первым входом блока элементов задержки и первым входом элемента ИЛИ, выход которого соединен с входом считывания блока- памяти, первый выход блока элементов задержки блока управления соединен с первым входом первого элемента И, выход которого соединен с информационным входом первого счетчика, информационный выход блока памяти соединен с вторым входом первого элемента И, тактовый вход устройства соединен с первым входом второго элемеита И, выход которого соединен со счетным входом первого счетчика, введены третий, четвертый, пятый, шестой и седьмой элементы И, первый и второй элементы ИЛИ, первый и второй блоки стековой памяти, первый и второй блоки сравнения, регистр, блок индикации, триггер, элемент задержки, дешифратор и второй счетчик, а в блок управления введены счетчик, дешифратор, триггер, элемент задержки, первый и второй элементы И, причем информационный выход блока памяти соединен с первыми входами третьего, четвертого, пятого и шестого элементов И, с входами дешифратора блока управления и первым входом первого а1емента И блока управления, выход которого соедииен с установочным входом счетчика блока управлеиия, выходы счетчика блока управления и кнопки «Пуск соединены соответственно с нулевым и единичным входами триггера блока управления, единичный и нулевой выходы которого соединены соответственно с первым входом второго элемента И блока управления и с первым входом блока индикации, выход переполиения второго счетчика соединен со счетным входом счетчика блока управления и через элемент задержки блока управления - с вторым вхадом второго элемента И блока управления, выход которого соединен с вторым входом элемента ИЛИ блока управления, первый.

второй, третий, четвертый и пятый выходы дешифратора блока управления соединены соответственно с вторым, третьим, четвертым пятым и шестым входами блока элементов задержки, блока управления второй, третий, четвертый, пятый и шестой выходы которого соединены соответственно с вторым входом первого элемента И блока управления, с вторыми входами третьего, четвертого, пятого и шестого элементов И, первый, второй,

0 третий, четвертый и пятый выходы дешифратора блока управления соединены соответственно с третьим, четвертым, пятым, шестым и седьмым входами элемента ИЛИ блока управления, выходы третьего, четвертого,

5 пятого и шестого элементов И соединены соответственно с информационным входом регистра, с информационным входом первого блока стековой памяти, с информационным входом второго счетчика и с информационным выходом устройства, информационный

0 вход устройства соединен с входом дешифратора и первым входом седьмого элемента И, выход которого соединен с информационным входом второго блока стековой памяти, информационные выходы первого и второго

5 блоков стековой памяти соединены соответственно с первым и вторым входами первого блока сравнения, выход сравнения которого соединен с первыми входами первого и второго элементов ИЛИ и со счетным входом второго счетчика, выход несравнения

0 первого блока сравнения соединен с вторым входом блока индикации, первый, второй и третий выходы дешифратора соединены соответственно с первым и вторым входами установки единицы и нуля триггера и с входами разрешения сравнения второго блока сравнения, второй выход дешифратора через элемент задержки соединен с вторым входом седьмого элемента И, единичный выход триггера соединен с вторым входом второго элемента И, информационные выходы перво0 го счетчика и регистра соединены соответственно с первым и вторым информационными входами второго блока сравнения, выход сравнения которого соединен с вторыми входами первого и второго элементов ИЛИ, вы ход несравнения второго блока сравнения и выход переполнения первого счетчика соединены соответственно с третьим и четвертым входами блока индикации, выходы первого и второго элементов ИЛИ соответственно с управляющими входами первого

0 и второго блоков стековой памяти.

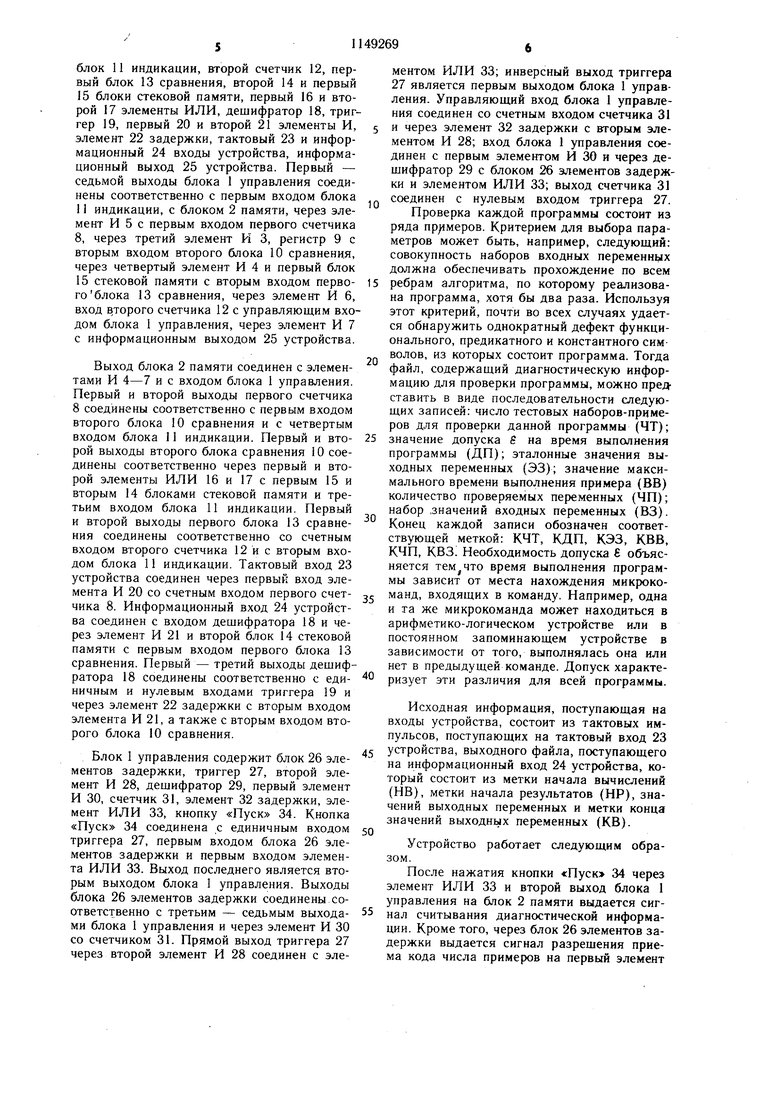

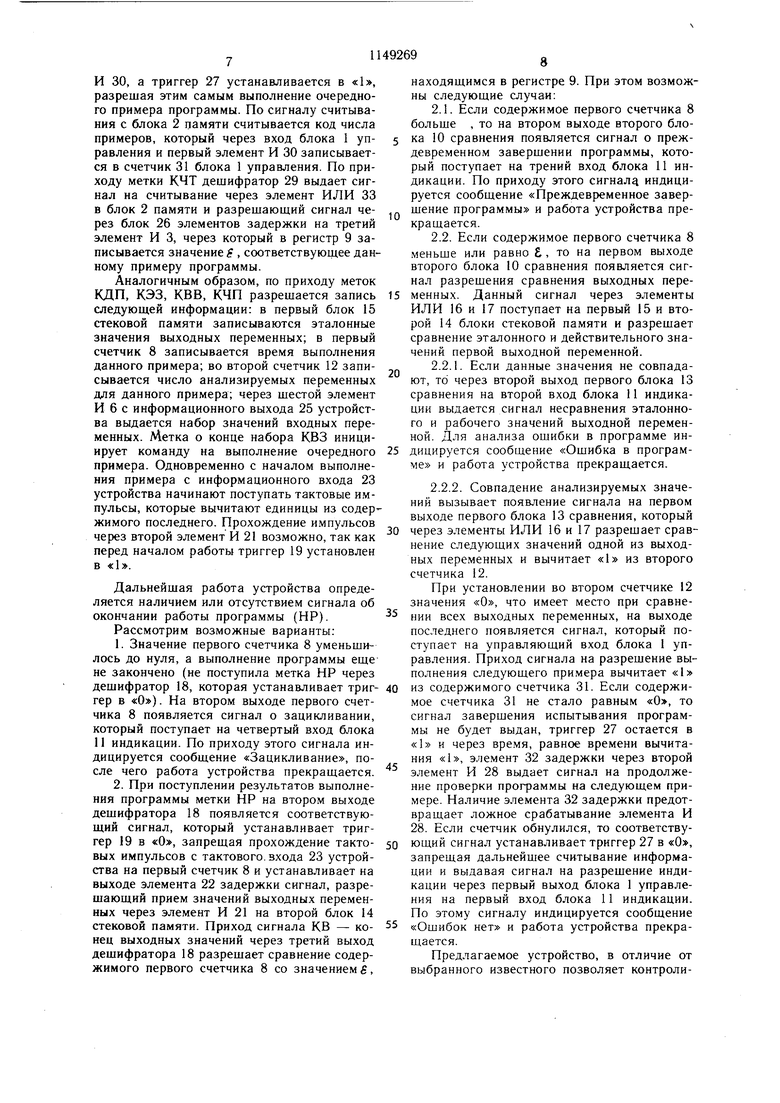

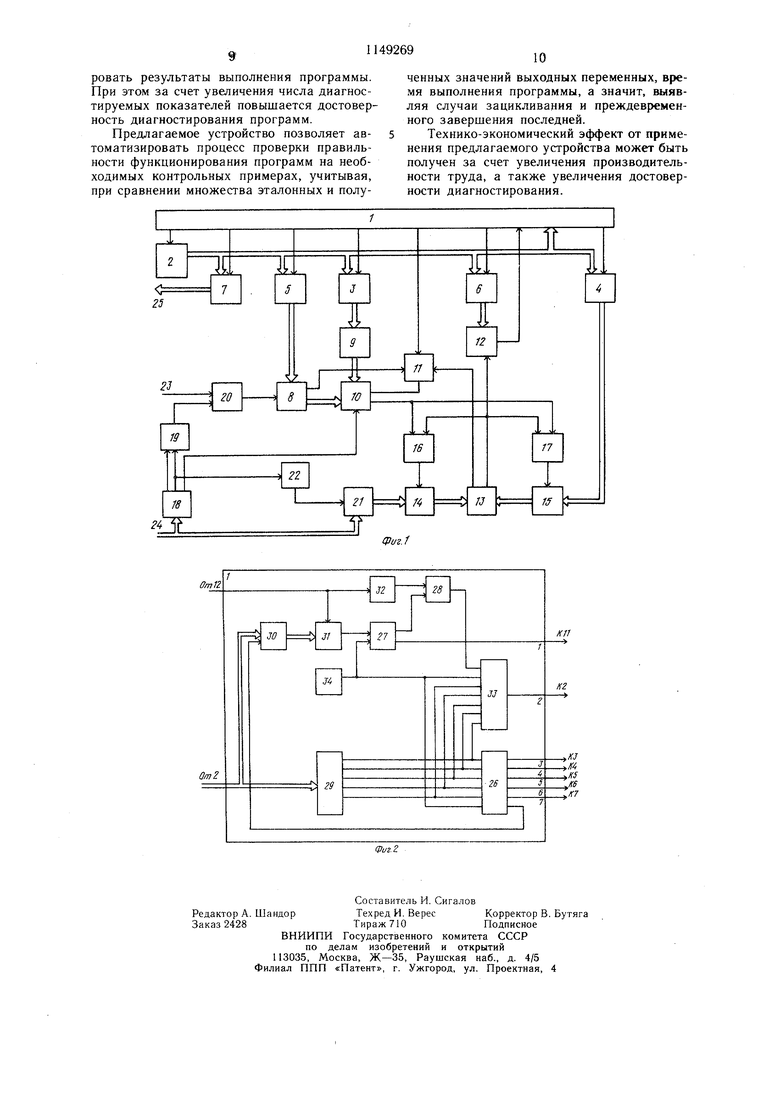

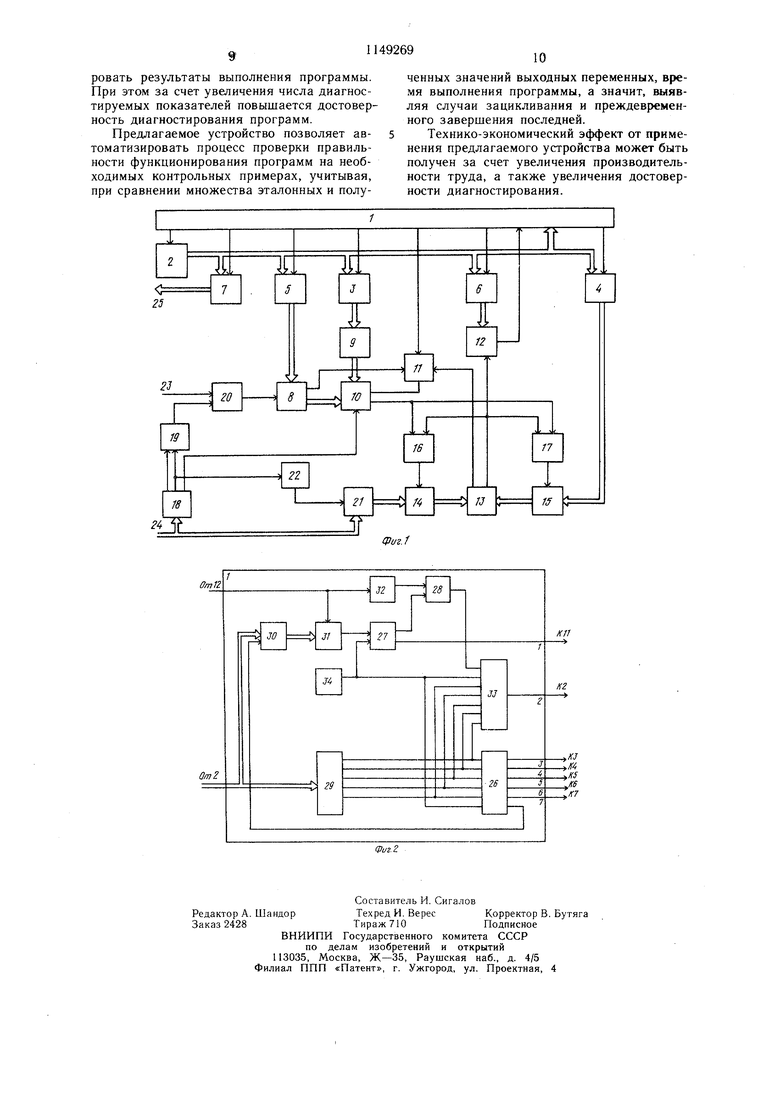

На фиг. I представлена структурная схема предлагаемого устройства; на фиг. 2 - пример конкретной реализации блока управления.

5 Устройство содержит блок 1 управления, блок 2 памяти, третий, четвертый, пятый, шестой и седьмой элементы И 3-7, первый счетчик 8, регистр 9, второй блок 10 сравнения. блок 11 индикации, второй счетчик 12, первый блок 13 сравнения, второй 14 и первый 15 блоки стековой памяти, первый 16 и второй 17 элементы ИЛИ, дешифратор 18, триггер 19, первый 20 и второй 21 элементы И, элемент 22 задержки, тактовый 23 и информационный 24 входы устройства, информационный выход 25 устройства. Первый - седьмой выходы блока 1 управления соединены соответственно с первым входом блока 11 индикации, с блоком 2 памяти, через элемент И 5 с первым входом первого счетчика 8, через третий элемент И 3, регистр 9 с вторым входом второго блока 10 сравнения, через четвертый элемент И 4 и первый блок 15 стековой памяти с вторым входом первогоблока 13 сравнения, через элемент И 6, вход второго счетчика 12 с управляющим входом блока 1 управления, через элемент И 7 с информационным выходом 25 устройства. Выход блока 2 памяти соединен с элементами И 4-7 и с входом блока 1 управления. Первый и второй выходы первого счетчика 8 соединены соответственно с первым входом второго блока 10 сравнения и с четвертым входом блока 11 индикации. Первый и второй выходы второго блока сравнения 10 соединены соответственно через первый и второй элементы ИЛИ 16 и 17 с первым 15 и вторым 14 блоками стековой памяти и третьим входом блока И индикации. Первый и второй выходы первого блока 13 сравнения соединены соответственно со счетным входом второго счетчика 12 и с вторым входом блока 11 индикации. Тактовый вход 23 устройства соединен через первый вход элемента И 20 со счетным входом первого счетчика 8. Информационный вход 24 устройства соединен с входом дешифратора 18 и через элемент И 21 и второй блок 14 стековой памяти с первым входом первого блока 13 сравнения. Первый - третий выходы дешифратора 18 соединены соответственно с едияичным и нулевым входами триггера 19 и через элемент 22 задержки с вторым входом элемента И 21, а также с вторым входом второго блока 10 сравнения. Блок 1 управления содержит блок 26 элементов задержки, триггер 27, второй элемент И 28, дешифратор 29, первый элемент И 30, счетчик 31, элемент 32 задержки, элемент ИЛИ 33, кнопку «Пуск 34. Кнопка «Пуск 34 соединена с единичным входом триггера 27, первым входом блока 26 элементов задержки и первым входом элемента ИЛИ 33. Выход последнего является вторым выходом блока 1 управления. Выходы блока 26 элементов задержки соединены соответственно с третьим - седьмым выходами блока 1 управления и через элемент И 30 со счетчиком 31. Прямой выход триггера 27 через второй элемент И 28 соединен с элементом ИЛИ 33; инверсный выход триггера 27 является первым выходом блока 1 управления. Управляющий вход блока 1 управления соединен со счетным входом счетчика 31 и через элемент 32 задержки с вторым элементом И 28; вход блока 1 управления соединен с первым элементом И 30 и через дешифратор 29 с блоком 26 элементов задержки и элементом ИЛИ 33; выход счетчика 31 соединен с нулевым входом триггера 27. Проверка каждой программы состоит из ряда пр меров. Критерием для выбора параметров может быть, например, следующий: совокупность наборов входных переменных должна обеспечивать прохождение по всем ребрам алгоритма, по которому реализована программа, хотя бы два раза. Используя этот критерий, почти во всех случаях удается обнаружить однократный дефект функционального, предикатного и константного символов, из которых состоит программа. Тогда файл, содержащий диагностическую информацию для проверки программы, можно представить в виде последовательности следующих записей: число тестовых наборов-примеров для проверки данной программы (ЧТ); значение допуска S на время выполнения программы (ДП); эталонные значения выходных переменных (ЭЗ); значение максимального времени выполнения примера (ВВ) количество проверяемых переменных (ЧП); набор .значений входных переменных (ВЗ). Конец каждой записи обозначен соответствующей меткой: КЧТ, КДП, КЭЗ, КВВ, КЧП, КВЗ. Необходимость допуска объясняется время выполнения программы зависит от места нахождения микрокоманд, входящих в команду. Например, одна и та же микрокоманда может находиться в арифметико-логическом устройстве или в постоянном запоминающем устройстве в зависимости от того, выполнялась она или нет в предыдущей команде. Допуск характеризует эти различия для всей программы. Исходная информация, поступающая на входы устройства, состоит из тактовых импульсов, поступающих на тактовый вход 23 устройства, выходного файла, поступающего на информационный вход 24 устройства, который состоит из метки начала вычислений (НВ), метки начала результатов (HP), значений выходных переменных и метки конца значений выходных переменных (KB). Устройство работает следующим образом. После нажатия кнопки «Пуск 34 через элемент ИЛИ 33 и второй выход блока 1 управления на блок 2 памяти выдается сигнал считывания диагностической информации. Кроме того, через блок 26 элементов задержки выдается сигнал разрешения приема кода числа примеров на первый элемент

И 30, а триггер 27 устанавливается в «1, разрешая этим самым выполнение очередного примера программы. По сигналу считывания с блока 2 памяти считывается код числа примеров, который через вход блока 1 управления и первый элемент И 30 записывается в счетчик 31 блока 1 управления. По приходу метки КЧТ дешифратор 29 выдает сигнал на считывание через элемент ИЛИ 33 в блок 2 памяти и разрешающий сигнал через блок 26 элементов задержки на третий элемент И 3, через который в регистр 9 записывается значение f , соответствующее данному примеру программы.

Аналогичным образом, по приходу меток КДП, КЭЗ, КВВ, КЧП разрешается запись следующей информации: в первый блок 15 стековой памяти записываются эталонные значения выходных переменных; в первый счетчик 8 записывается время выполнения данного примера; во второй счетчик 12 записывается число анализируемых переменных для данного примера; через шестой элемент И 6 с информационного выхода 25 устройства выдается набор значений входных переменных. Метка о конце набора КВЗ инициирует команду на выполнение очередного примера. Одновременно с началом выполнения примера с информационного входа 23 устройства начинают поступать тактовые импульсы, которые вычитают единицы из содержимого последнего. Прохождение импульсов через второй элемент И 21 возможно, так как перед началом работы триггер 19 установлен в «1.

Дальнейшая работа устройства определяется наличием или отсутствием сигнала об окончании работы программы (HP).

Рассмотрим возможные варианты:

11 индикации. По приходу этого сигнала индицируется сообщение «Зацикливание, после чего работа устройства прекращается.

находящимся в регистре 9. При этом возможны следующие случаи:

0 через элементы ИЛИ 16 и 17 разрешает сравнение следующих значений одной из выходных переменных и вычитает «1 из второго счетчика 12.

При установлении во втором счетчике 12 значения «О, что имеет место при сравне НИИ всех выходных переменных, на выходе последнего появляется сигнал, который поступает на управляющий вход блока 1 управления. Приход сигнала на разрешение выполнения следующего примера вычитает «1

0 из содержимого счетчика 31. Если содержимое счетчика 31 не стало равным «0, то сигнал завершения испытывания программы не будет выдан, триггер 27 остается в «1 и через вре.мя, равное времени вычитания «1, э.чемент 32 задержки через второй

элемент И 28 выдает сигнал на продолжение проверки программы на следующем примере. Наличие элемента 32 задержки предотвращает ложное срабатывание элемента И 28. Если счетчик обнулился, то соответствующий сигнал устанавливает триггер 27 в «О, запрещая дальнейшее считывание информации и выдавая сигнал на разрешение индикации через первый вы.ход блока 1 управления на первый вход блока 11 индикации. По этому сигналу индицируется сообщение

5 «Ошибок нет и работа устройства прекращается.

Предлагаемое устройство, в отличие от выбранного известного позволяет контролировать результаты выполнения программы. При этом за счет увеличения числа диагностируемых показателей повышается достоверность диагностирования программ.

Предлагаемое устройство позволяет автоматизировать процесс проверки правильности функционирования программ на необходимых контрольных примерах, учитывая, при сравнении множества эталонных и полученных значении выходных переменных, время выполнения программы, а значит, выявляя случаи зацикливания и преждевременного завершения последней.

Технико-экономический эффект от применения предлагаемого устройства может быть получен за счет увеличения производительности труда, а также увеличения достоверности диагностирования.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для отладки программ | 1977 |

|

SU630630A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-04-07—Публикация

1983-07-04—Подача