ел

ел

со

Oi (Г

В их од

го

-

Изобретение относится к автоматике и может быть использовано в системах 1-р|фровой синхрот1зации связных станщ1й.

Целью изобретения является расширение диапазона преобразованных частот следования импульсов.

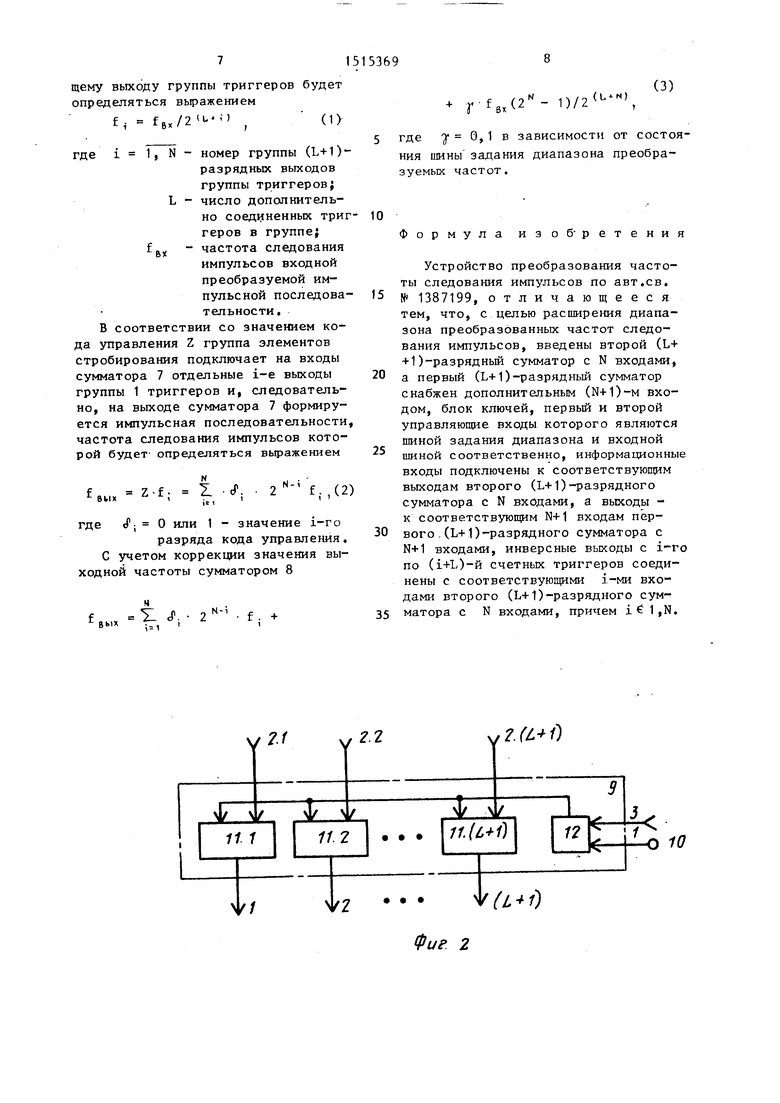

На фиг.1 представлена функциональная схема устройства;на фиг. 2 выполнение группы ключей; на фиг.З - пример подключения сумматора к группе триггеров для случая, когда , .,

Устройство преобразования частоты следования импульсов содержит группу 1 из (N+L) последовательно соединенных триггеров, формирователь 2 импульсов, этгемент ИЛИ 3, N-раз- рядный регистр 4, группу 5 из N элементов задержки 5.1-5.N, группу 6 из N элементов стробирования 6.1-6.N, (L+1 )-разрядн1,1е сумматоры 7 и 8с N входами, группу 9 ключей и 1Ш1ну 10 управления диапазоном преобразованных частот.

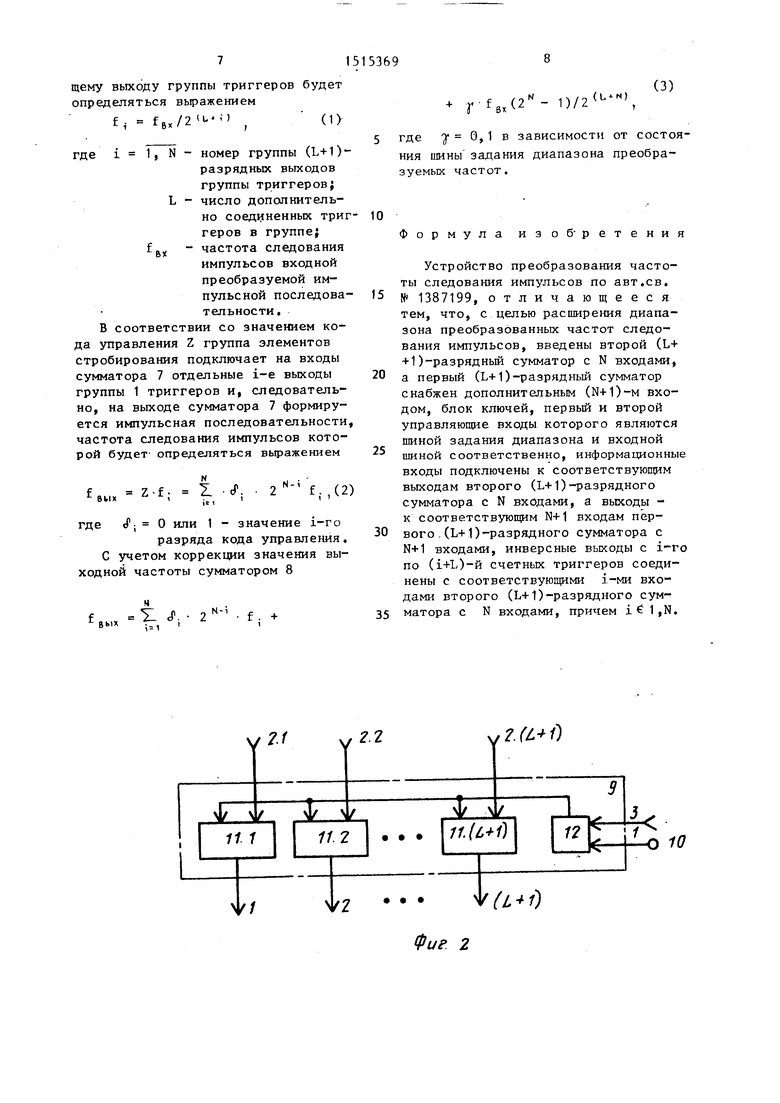

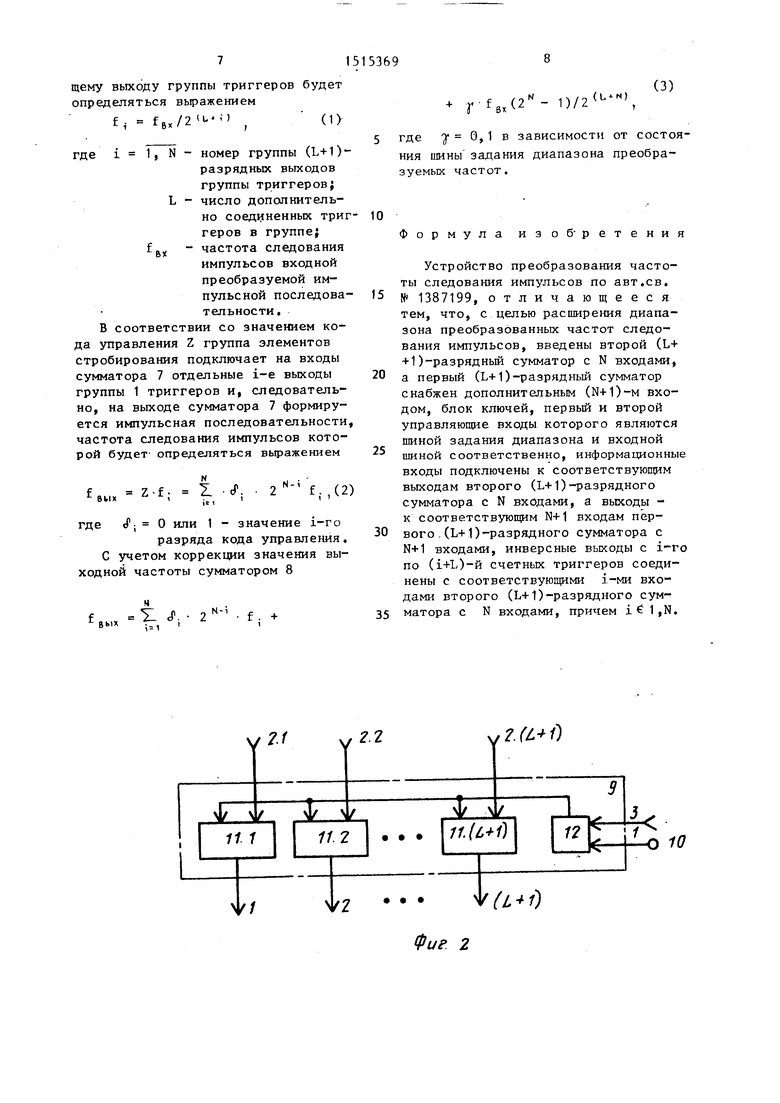

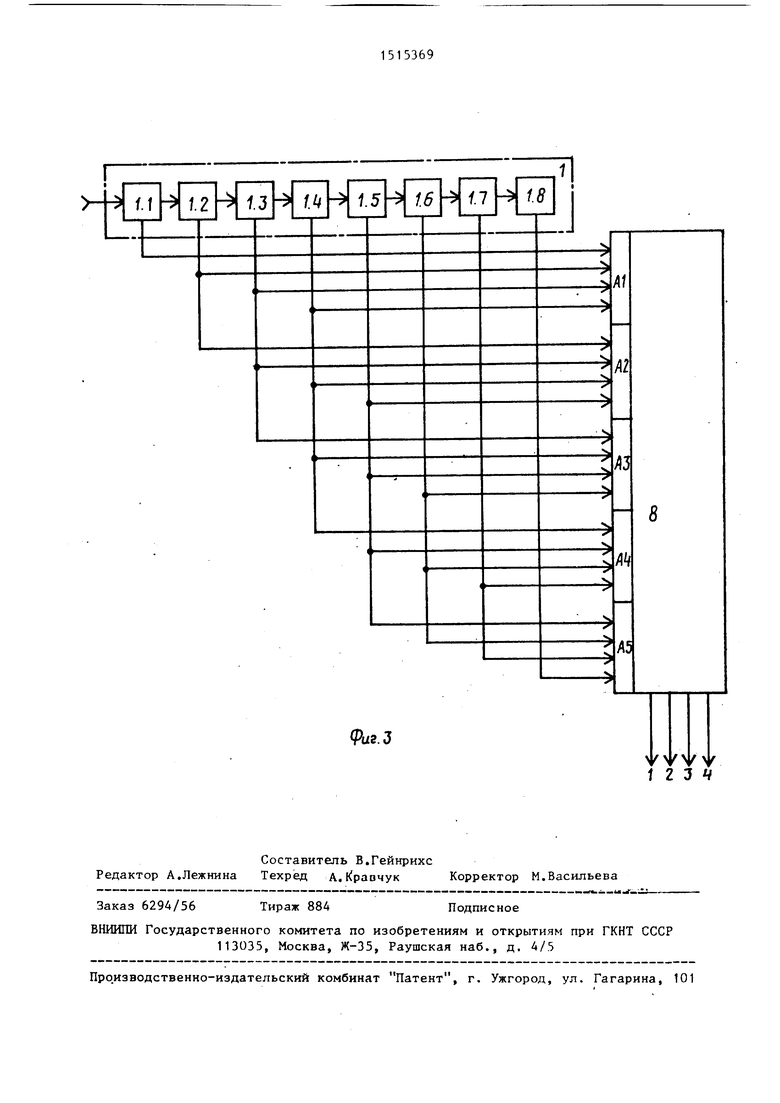

Группа 9 ключей содержит (Ь+1) логических элементов 2И 11.1-11.(L+ и D-триггер 12.

Устройство преобразования ча..1. - ты следования импульсов работаг:- следу ю;цим образом.

В исходном состоянии на входной шине цифрового упраапения н на игине 10 управления диапазоном присутству- ют сигналы О, При этом триттеры 1.1-l.() группы 1 триггеро} и регистр 4 могут находиться в произвольном состоянии. Сигнал О с вход

ной шины 10 управления диапазоном поступает на первый управляющий вход группы 9 ключс-; и запрещает прохождение сипналов с ипфopмaп oп ыx входов группы 9 ключей на его вьгходы.

8результате этого на выходах группы

9ключей присутствуют сигналы О.

С поступлеииеь управляюшег о импульсного кода па лходную шину цифрового управления ил в яходе И. 3 формируется имт1ульс 1ый сигнал, ус- танавливающи в одимичное состояние триггеры 1 .1-1. (tJ + .) rpyimb 1 триггеров и обиуляки .ип М-рлзрялт ы;1 регистр 4. Сформиронаиные сцгн; , О на выходах )рядного регистра 4 блокируют ;1лом; пт.1 6.1-6.N группы 6 элрмеито c i poonpoi amui , 1а выходах группм i -j.n г меитов CTpofiiipo-- вания также уст а1 Л1 гп(Г ЯН1Тся cuiпа.иы

10

20

ы з10 1)

- 30 е- 35 д25

од о

ы

о3 е ыы

515369

О. Данные сигналы поступают на входы (L+1)-разрядного сумматора 7, При этом на его (N4l)-ft вход поданы 5 сигналы О с выхода группы 9 ключей. На выходе (L+D-ro разряда суммы сумматора 7 формируется сигнал О. Через временной интервал TJQA задаваемый элементами .5.1-5.N группы 5 элементов задержки, в N-разряд- ный регистр 4 заносится новое значение управляющего кода, десятичный эквивалент которого определяет значение частоты следования импульсов выходной последовательности. С поступлением на вход первого триггера 1.1 группы 1 триггеров первого импульса входной последовательности на инверсных выходах триггеров 1.1 - 1.(N+T,) формируются уровни 1. Данные сигналы с инверсных выходов триггеров группы 1 триггеров поступают на входы сумматора 8 и на ин- формадаонные входы группы 6 элементов стробирования 6.1-6.Ы„ В соответствии со значением кода управления Z на выходе N-разрядного регистра 4 по входаг стробирования будут открыты соответствующие элементы 6.1-6.N группы 6 элементов строби- роиания. В результате этого к входам сумматора 7 будут подключены со- ответствуюцще (L+1)-разрядные выходы группы 1 триггеров и на выходе (L+ +1)-го разряда суммы сумматора 7 изменится напряжение с уровня О на 1. При этом формирователь 2 импульсов на своем выходе формирует первьй импульс выходной последовательности с преобразованной частотой следования. С поступлением на вход группы 1 триггеров очередных импульсов входной последовательности на ин- инверсных (L+1)-разрядных i-x (i 1, N) выходах группы 1 триггеров формируются линейно убьшающие двоичные коды, скорость изменения которых пропорциональна соответствующей преобразованной частоте следования импульсов. Данные коды через соответствующие элементы группы 6 элементов стробирования поступают на соответствующие входы (L-f 1)-разрядного сумматора 7, который суммируют коды по модулю . В зависимости от значения управляющего кода на выходе (L+1)-разрядного сумматора 7 формируется последовательность импульсов, частота следования которых

40

45

50

55

пропорциональна десятичному эквиваленту двоичного кода управления, поступившего на входную шину цифрового управления. Формирователь 2 импульсов на своем выходе формирует стандартные импульсы каждый раз,когда сигнал на выходе сумматора 7 изменяется с уровня О на 1,

При поступлении на входную шину 10 управления диапазоном сигнала 1 очередной импульс входной последовательности дает разрешение на прохождение сигнала с выхода сумматора 8 на (N+1)-A вход сумматора 7, В зависимости от значения управляющего кода на N входов сумматора 7 через элементы 6.1-6.N группы 6 элементов стробирования поступают линейно убывающие двоичные коды, значения которых за заданный промежуток времени изменяются с различной скоростью. Заданный промежуток времени определяется значением частоты входной импульсной последовательности, суммарной разрядностью группы 1 триггеров N и L и определяется как t )( 2 В результате суммирования двоичных кодов, поступающих с выходов группы 6 элементов стробирования на входы сумматора 7, с линейно убывающим двоичным кодом, поступающим на (Н+1)-й вход сумматора 7, на (L+1)-M выходе суммы сумматора 7 формируется импульсная последоватёльность, частота следования импульсов которой зависит от результата суммиования линейно убывающего двоичного кода на (N+1)-M входе сумматора

7 и с установленной регистром 4 и руппой 6 элементов стробирования омбинацией линейно убывающих двоичных кодов на N входах сумматора 7. С выхода формирователя 2 импульсов на

выход устройства поступают ставдарт- ные импульсы вькодной последовательности при изменении на (L41)-м выходе суммы сумматора 7 сигнала с уровня О на 1.

Группа 9 ключей работает следующим образом (фиг.2).

В исходном состоянии триггер 12 находится в нулевом состоянии, при котором на его прямом выходе присутствует сигнал О.. Исходное состояние триггера 12 может быть обеспечено, например, путем подачи на R- вход триггера кратковременного поло0

5

0

5

0

5

0

5

0

5

жительного импульса, формирование которого осуществляется с помощью дифференцирующей цепи, включенной между R-входом триггера и источником пита рп1их напряжений. Сигнал с прямого выхода триггера поступает на объединенные первые входы элементов 2И 11.1-11.(L+1) и запрещает прохождение сигналов в виде 1, поступающих на их вторые входы, ни выход блока. В результате этого на вьсходе группы 9 ключей присутствуют сигналы О. При поступлении на первый управляющий вход группы 9 ключей, а следовательно, и на информационный D-вход триггера 12 сигнала О очередным импульсом входной последовательности, поступающим на второй управляющий вход блока и далее на С-вход триггера 12, подтверждается исходное состояние триггера 12. При этом на выходе блока во всех (L+1) разрядах установлены сигналы в виде уровней О, что соответствует нулевому значению выходного двоичного кода на выходе блока. При поступлении на первый управ- вход сигнала в виде уровня 1 очередной импульс входной последовательности устанавливает триггер 12 в единичное состояние, при котором на его прямом выходе формируется сигнал 1. Данный сигнал поступает на объединенные первые входы элементов 2И 11.1-11.(L+1). В результате этого сигналы на вторых входах элементов 2И 11.1-11.(L+1) в виде О или 1 поступают на выход группы 9 ключей, т.е. тем самым обеспе.чивается передача сигналов с информационных входов блока на его выход,

/Таким образом, в зависимости от вида сигнала на первом управляющем входе блока последний обеспечивает передачу или запрет на прохождение линейно убьшающего двоичного кода, поступающего на информационный вход

блока.

I .

Вследствие того, что формируемая выходная последовательность поступает на вход формирователя импульсов со старшего (L+1)-ro разряда суммы сумматора,частота следования импуль- сов на выходе устройства при поступлении двоичньпс кодов на каждый i-й отдельно подключенный соответствующий вход сумматора к соответствующему выходу группы триггеров будет определяться выражением

f,-

fa,/24---)

;

(1)

где

L вх

i 1, N - номер группы (L+1)- разрядных выходов группы триггеров; число дополнительно соединенных триг геров в группе; частота следования импульсов входной преобразуемой импульсной последовательности,

В соответствии со значением кода управления Z группа элементов стробировання подключает на входы сумматора 7 отдельные i-e выходы группы 1 триггеров и, следовательно, на выходе сумматора 7 формируется импульсная последовательности, частота следования импульсов которой будет определяться выражением

feuK Z-f; i . f.,(2)

где сГ; О или 1 - значение i-ro разряда кода управления. С учетом коррекции значения выходной частоты сумматором 8

ВЫХ

N

, . f. +

. r fex( 1),

(3)

5 где J О, 1 в зависимости от состояния шины задания диапазона преобразуемых частот.

- 10

Формула изоб ретения

Устройство преобразования частоты следования импульсов по авт.св. № 1387199, отличающееся тем, что, с целью расширения диапазона преобразованных частот следования импульсов, введены второй (L+ +1)-разрядньш сумматор с N входами, а первый (L+1)-разрядный сумматор снабжен дополнительным (N+1)-M входом, блок ключей, первый и второй управляющие входы которого являются шиной задания диапазона и входной шиной соответственно, информационные входы подключены к соответствующим выходам второго (L+1)-разрядного сумматора с N входами, а вьгходы - к соответствующим N+1 входам первого . (Ь+1)-разрядного сумматора с N+1 входами, инверсные выходы с i-ro по (1+Ь)-й счетных триггеров соединены с соответствующими i-ми входами второго (L+1)-разрядного сумматора с N входами, причем ie 1 ,N.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования частоты следования импульсов | 1986 |

|

SU1387199A1 |

| Цифровой модулятор | 1991 |

|

SU1800604A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

| Цифроаналоговый преобразователь | 1989 |

|

SU1735999A1 |

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ ПРЕОБРАЗОВАТЕЛЯ ЧАСТОТЫ АСИНХРОННОГО ДВИГАТЕЛЯ | 1995 |

|

RU2111608C1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1317658A1 |

| Преобразователь двоичного кода в унитарный код | 1982 |

|

SU1049897A1 |

| Экстраполирующий умножитель частоты | 1987 |

|

SU1497706A1 |

| ОПЕРАТИВНЫЙ КОНТРОЛЛЕР СУММАРНОЙ МОЩНОСТИ НАГРУЗКИ ГРУППЫ ЭНЕРГОПОТРЕБИТЕЛЕЙ | 1998 |

|

RU2145717C1 |

| Генератор последовательности чисел | 1981 |

|

SU999032A1 |

Изобретение относится к автоматике и может быть использовано в системах цифровой синхронизации связных станций. Цель изобретения - расширение диапазона преобразованных частот следования импульсов. Поставленная цель достигается за счет того, что в устройство, содержащее группу 1 счетных триггеров, формирователь 2, элемент ИЛИ 3, N -разрядный регистр 4, группу 5 из N элементов задержки, группу 6 из N элементов стробирования,(L+1)-разрядный сумматор 7 с (N+1) входами, введены (L+1)-разрядный сумматор с N входами и блок ключей, что позволяет организовать дополнительный поддиапазон преобразованных частот. 3 ил.

v

)

Фиг. 2

| Жодзишский М.И | |||

| и др | |||

| Цифр овые системы фазовой синхронизации | |||

| М.: Советское радио, 1980, с.49, рис | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для преобразования частоты следования импульсов | 1986 |

|

SU1387199A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-10-15—Публикация

1987-10-26—Подача