00 00

со со

,N-i-i

фиг.

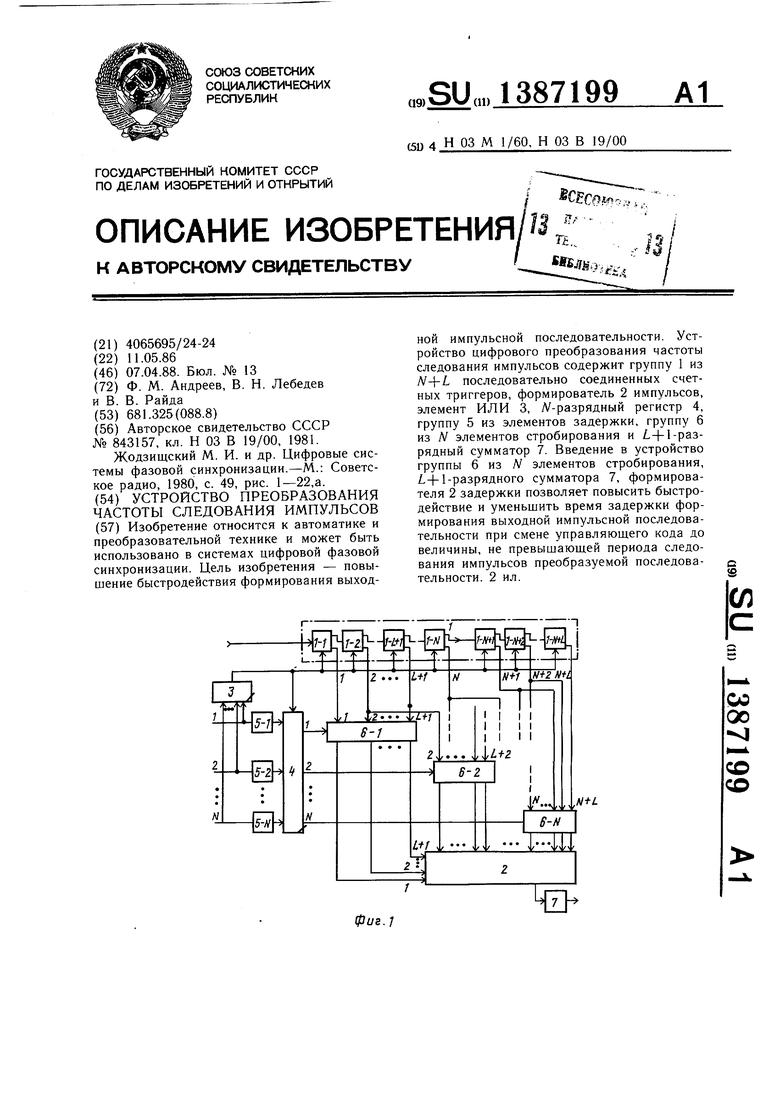

Изобретение относится к автоматике и преобразовательной технике и может быть использовано в системах цифровой синхронизации связных станций.

Цель изобретения - повышение быстродействия формирования выходной импульсной последовательности.

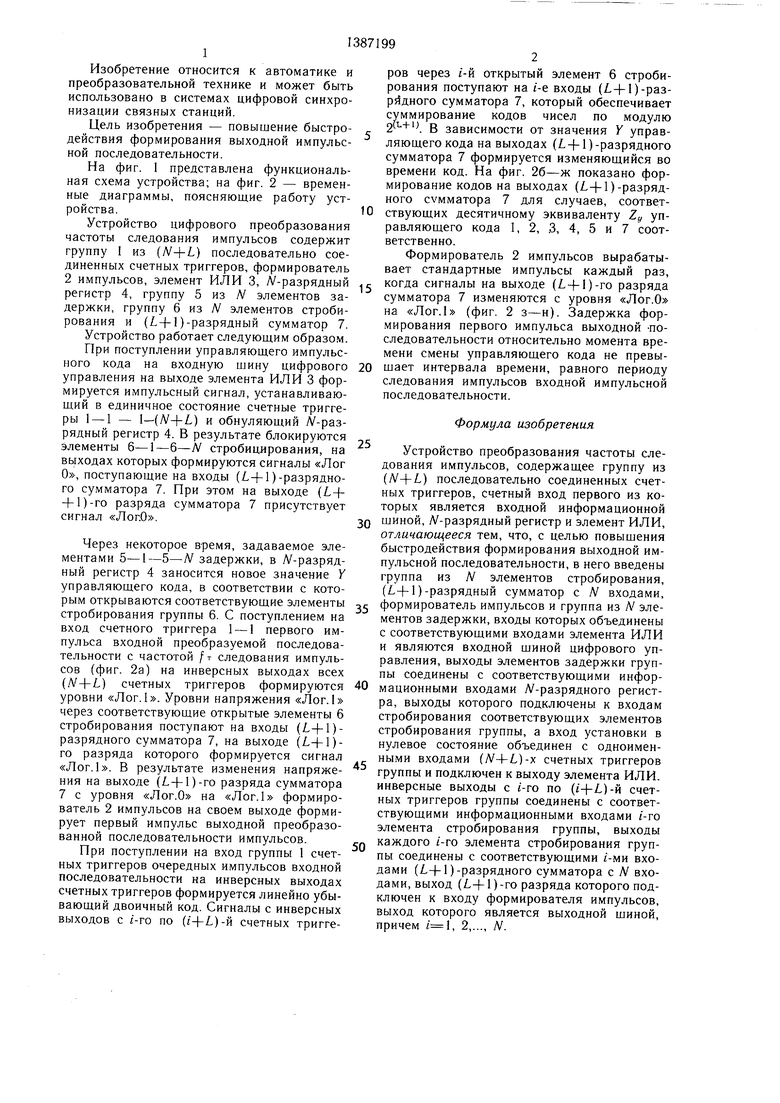

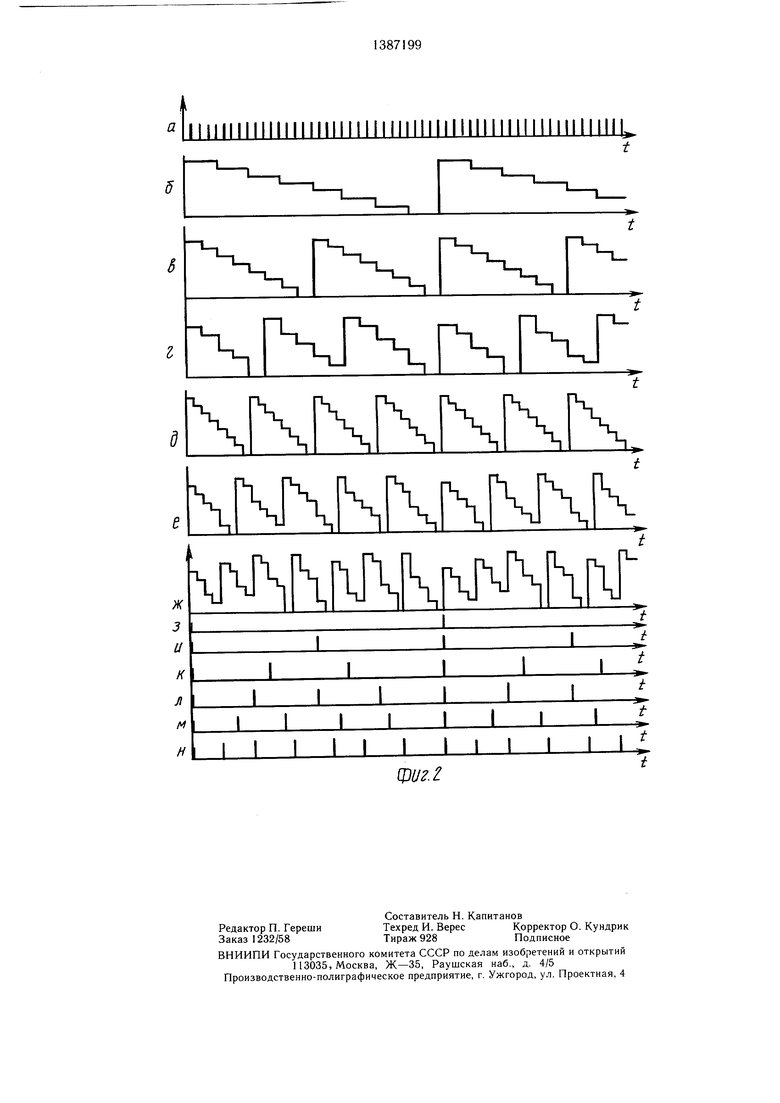

На фиг. I представлена функциональная схема устройства; на фиг. 2 - временные диаграммы, поясняющие работу устройства.

Устройство цифрового преобразования частоты следования импульсов содержит группу 1 из () последовательно соединенных счетных триггеров, формирователь

ров через /-и открытый элемент 6 строби- рования поступают на /-е входы (+1)-раз- р 1дного сумматора 7, который обеспечивает суммирование кодов чисел по модулю 2(+1) в зависимости от значения Y управляющего кода на выходах (L+1)-разрядного сумматора 7 формируется изменяющийся во времени код. На фиг. 26-ж показано формирование кодов на выходах (L+1)-разрядного сумматора 7 для случаев, соответ- 10 ствующих десятичному эквиваленту Zy управляющего кода 1, 2, .3, 4, 5 и 7 соответственно.

Формирователь 2 импульсов вырабатывает стандартные импульсы каждый раз.

2 импульсов, элемент ИЛИ 3, yV-разрядный . когда сигналы на выходе (L+l)-ro разряда регистр 4, группу 5 из /V элементов за-сумматора 7 изменяются с уровня «Лог.О

держки, группу 6 из /V элементов строби- рования и (1+1)-разрядный сумматор 7.

Устройство работает следующим образом.

При поступлении управляющего импульсного кода на входную щину цифрового 20 щает интервала времени, равного периоду управления на выходе элемента ИЛИ 3 фор-следования импульсов входной импульсной

мируется импульсный сигнал, устанавливающий в единичное состояние счетные триггеры 1 - 1 - I-(/V+L) и обнуляющий Л -раз- рядный регистр 4. В результате блокируются элементы 6-1-6-N стробицярования, на вьгходах которых формируются сигналы «Лог О, поступающие на входы (L-+-1)-разрядного сумматора 7. При этом на выходе {L-{- + 1)-го разряда сумматора 7 присутствует сигнал «Лог.О.

на «Лог. 1 (фиг. 2 3-н). Задержка формирования первого импульса выходной -последовательности относительно момента времени смены управляющего кода не превыпоследовательности.

Формула изобретения

25

Устройство преобразования частоты следования импульсов, содержащее группу из ) последовательно соединенных счетных триггеров, счетный вход первого из которых является входной информационной 30 шиной, /V-разрядный регистр и элемент ИЛИ,

35

отличающееся тем, что, с целью повыщения быстродействия формирования выходной импульсной последовательности, в него введены группа из N элементов стробирования, (L-f-1)-разрядный сумматор с N входами, формирователь импульсов и группа из N элементов задержки, входы которых объединены с соответствующими входами элемента ИЛИ и являются входной шиной цифрового управления, выходы элементов задержки группы соединены с соответствующими инфорЧерез некоторое время, задаваемое элементами 5-1-5-Л задержки, в УУ-разряд- ный регистр 4 заносится новое значение Y управляющего кода, в соответствии с которым открываются соответствующие элементы стробирования группы 6. С поступлением на вход счетного триггера 1 - 1 первого импульса входной преобразуемой последовательности с частотой /т следования импульсов (фиг. 2а) на инверсных выходах всех

() счетных триггеров формируются 40 мационными входами Л/-разрядного регист- уровни «Лог.I. Уровни напряжения «Лог. 1 ра, выходы которого подключены к входам через соответствующие открытые элементы 6 стробирования соответствующих элементов стробирования поступают на входы (L+l)-стробирования группы, а вход установки в

разрядного сумматора 7, на выходе (L+1)-нулевое состояние объединен с одноименго разряда которого формируется сигналными входами ()-x счетных триггеров

«Лог. 1. В результате изменения напряже- группы и подключен к выходу элемента ИЛИ. ния на выходе (L+l)-ro разряда сумматора 7 с уровня «Лог.О на «Лог. 1 формирователь 2 импульсов на своем выходе формирует первый импульс выходной преобразованной последовательности импульсов.

При поступлении на вход группы 1 счетных триггеров очередных импульсов входной последовательности на инверсных выходах

счетных триггеров формируется линейно убывающий двоичный код. Сигналы с инверсных выходов с /-ГО по ()-H счетных триггеинверсные выходы с г -го по () -н счетных триггеров группы соединены с соответствующими информационными входами /-го элемента стробирования группы, выходы гп каждого /-ГО элемента стробирования группы соединены с соответствующими /-ми входами ()-разрядного сумматора с N входами, выход (L+1) -го разряда которого подключен к входу формирователя импульсов, выход которого является выходной щиной, причем , 2,..., Л.

ров через /-и открытый элемент 6 строби- рования поступают на /-е входы (+1)-раз- р 1дного сумматора 7, который обеспечивает суммирование кодов чисел по модулю 2(+1) в зависимости от значения Y управляющего кода на выходах (L+1)-разрядного сумматора 7 формируется изменяющийся во времени код. На фиг. 26-ж показано формирование кодов на выходах (L+1)-разрядного сумматора 7 для случаев, соответ- 0 ствующих десятичному эквиваленту Zy управляющего кода 1, 2, .3, 4, 5 и 7 соответственно.

Формирователь 2 импульсов вырабатывает стандартные импульсы каждый раз.

когда сигналы на выходе (L+l)-ro разряда сумматора 7 изменяются с уровня «Лог.О

когда сигналы на выходе (L+l)-ro разряда сумматора 7 изменяются с уровня «Лог.О

щает интервала времени, равного периоду следования импульсов входной импульсной

на «Лог. 1 (фиг. 2 3-н). Задержка формирования первого импульса выходной -последовательности относительно момента времени смены управляющего кода не превыпоследовательности.

Формула изобретения

Устройство преобразования частоты следования импульсов, содержащее группу из ) последовательно соединенных счетных триггеров, счетный вход первого из которых является входной информационной шиной, /V-разрядный регистр и элемент ИЛИ,

отличающееся тем, что, с целью повыщения быстродействия формирования выходной импульсной последовательности, в него введены группа из N элементов стробирования, (L-f-1)-разрядный сумматор с N входами, формирователь импульсов и группа из N элементов задержки, входы которых объединены с соответствующими входами элемента ИЛИ и являются входной шиной цифрового управления, выходы элементов задержки группы соединены с соответствующими информационными входами Л/-разрядного регист- ра, выходы которого подключены к входам стробирования соответствующих элементов стробирования группы, а вход установки в

группы и подключен к выходу элемента ИЛИ.

инверсные выходы с г -го по () -н счетных триггеров группы соединены с соответствующими информационными входами /-го элемента стробирования группы, выходы каждого /-ГО элемента стробирования группы соединены с соответствующими /-ми входами ()-разрядного сумматора с N входами, выход (L+1) -го разряда которого подключен к входу формирователя импульсов, выход которого является выходной щиной, причем , 2,..., Л.

Illlllllllllllll

ILL

Illlllllllllliilllill

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство преобразования частоты следования импульсов | 1987 |

|

SU1515369A2 |

| Экстраполирующий умножитель частоты | 1987 |

|

SU1497706A1 |

| Цифроаналоговый преобразователь | 1989 |

|

SU1735999A1 |

| Устройство для извлечения корня седьмой степени | 1983 |

|

SU1120321A1 |

| Умножитель частоты | 1985 |

|

SU1305822A1 |

| Устройство задержки | 1985 |

|

SU1298876A1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ТЕЛЕВИЗИОННЫХ СИГНАЛОВ | 1991 |

|

RU2014745C1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

| ДВОИЧНЫЙ УМНОЖИТЕЛЬ | 1992 |

|

RU2006918C1 |

Изобретение относится к автоматике и преобразовательной технике и может быть использовано в системах цифровой фазовой синхронизации. Цель изобретения - повышение быстродействия формирования выходной импульсной последовательности. Устройство цифрового преобразования частоты следования импульсов содержит группу 1 из N+L последовательно соединенных счетных триггеров, формирователь 2 импульсов, элемент ИЛИ 3, jV-разрядный регистр 4, группу 5 из элементов задержки, группу 6 из N элементов стробирования и L+1-разрядный сумматор 7. Введение в устройство группы 6 из /V элементов стробирования, L+1-разрядного сумматора 7, формирователя 2 задержки позволяет повысить быстродействие и уменьшить время задержки формирования выходной импульсной последовательности при смене управляющего кода до величины, не превышающей периода следования импульсов преобразуемой последовательности. 2 ил. (Q (Л

ж

I I

I I I

I I I I I I I 1 I I i

I I I

| Цифровой синтезатор частот | 1979 |

|

SU843157A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Жодзищский М | |||

| И | |||

| и др | |||

| Цифровые системы фазовой синхронизации.-М.: Советское радио, 1980, с | |||

| Способ смешанной растительной и животной проклейки бумаги | 1922 |

|

SU49A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-04-07—Публикация

1986-05-11—Подача