Изобретение относится к радиосвязи, предназначено для использования в системах передачи дискретной информации и является усовершенствованием устройства по авт. св.№1078662.

Цель изобретения - повышение достоверности принимаемых сообщений.

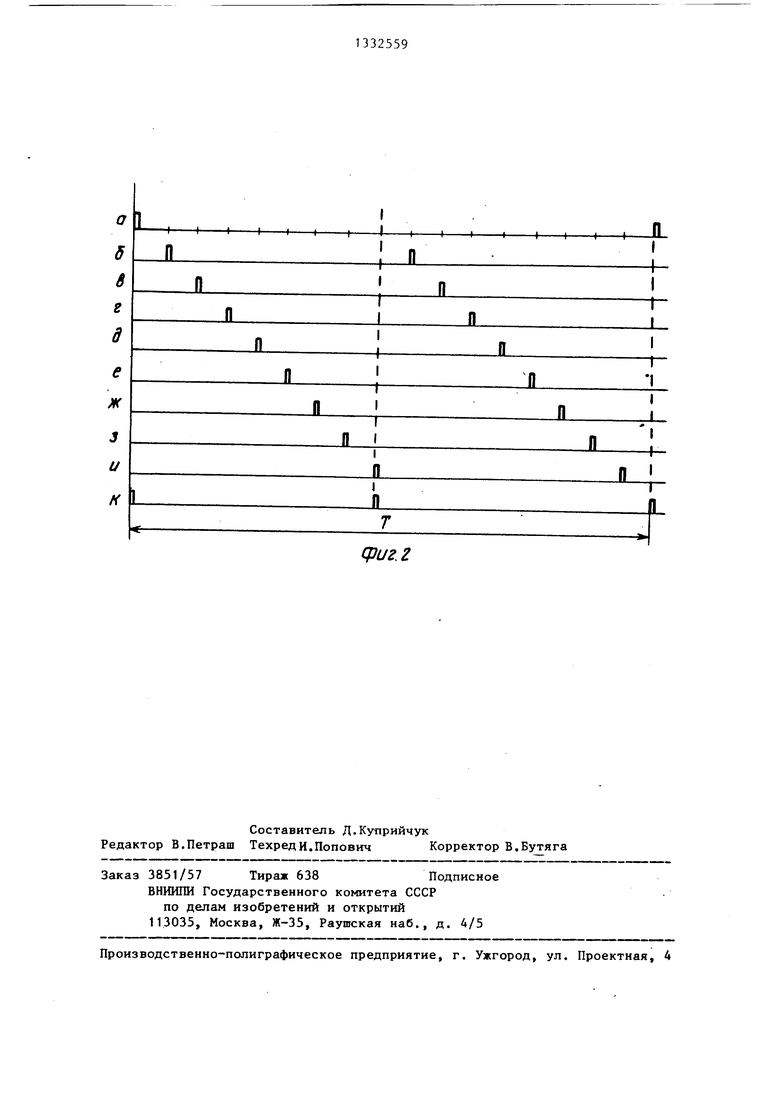

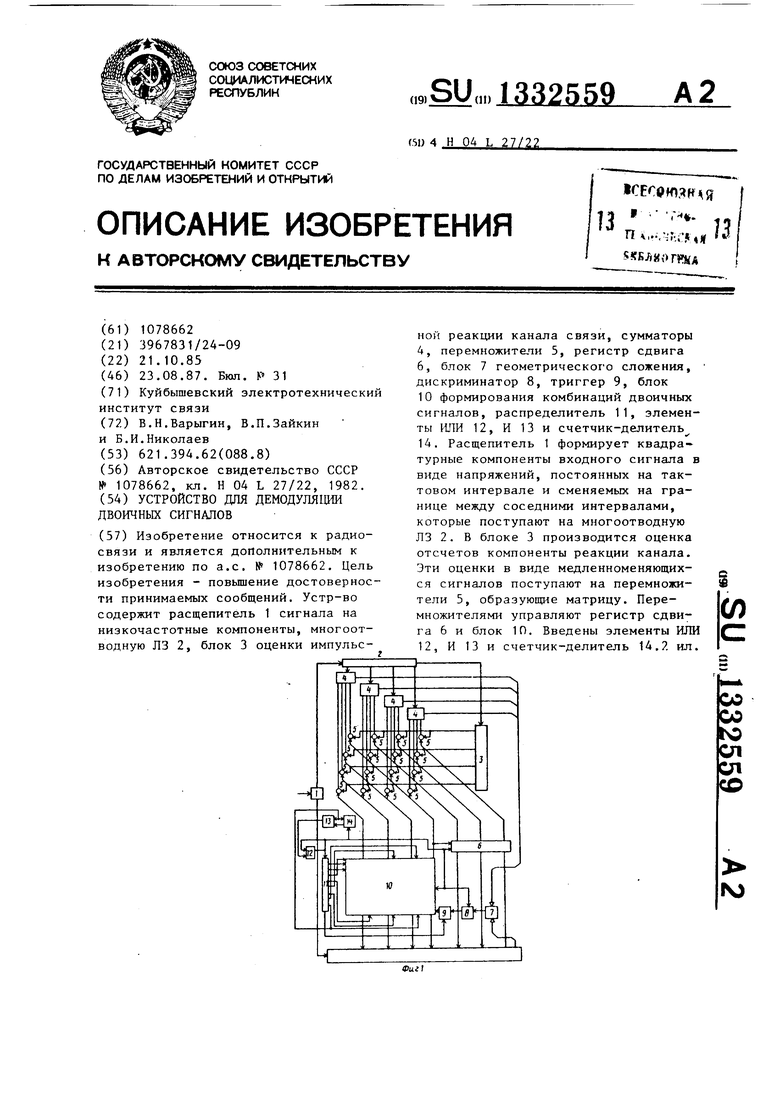

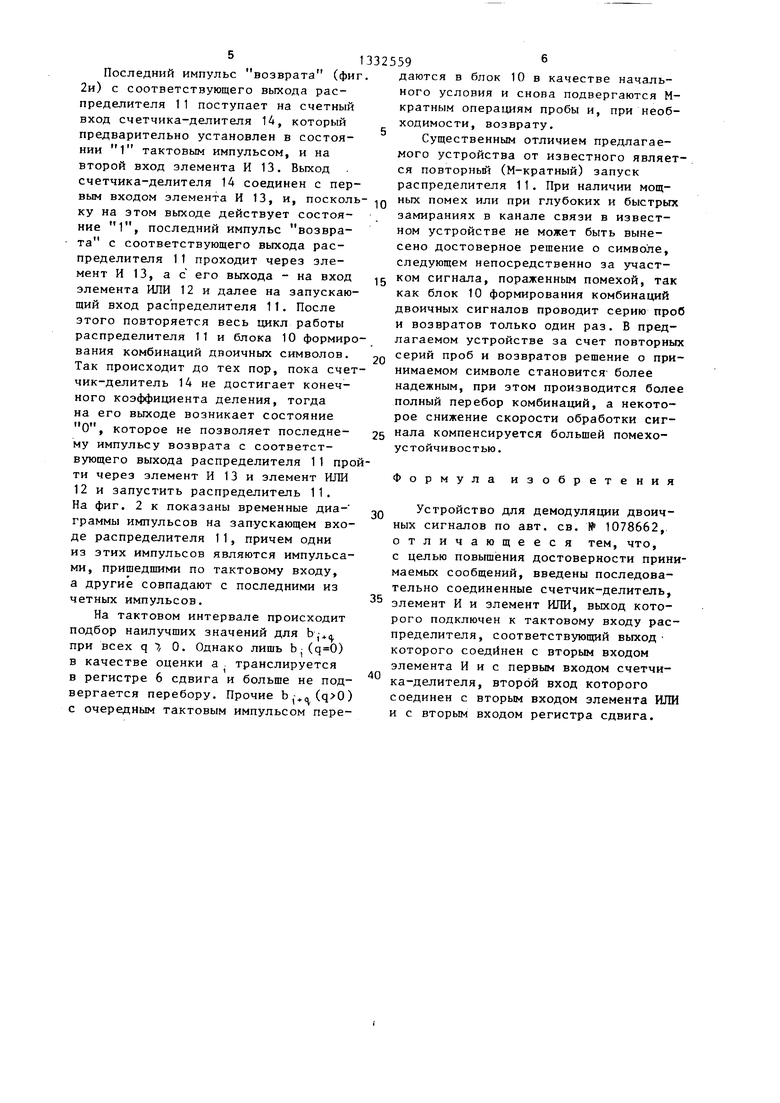

На фиг. 1 представлена структурна электрическая схема устройства для демодуляции двоичных сигналов; на фиг. 2 - временные диаграммы работы распределителя при коэффициенте деления счетчика-делителя равном двум.

Устройство для демодуляции двоичных сигналов содержит расщепитель 1 сигнала на н изкочастотные компоненты многоотводную линию 2 задержки, блок 3 оценки импульсной реакции канала связи, сумматоры 4, перемножители 5, регистр 6 сдвига, блок 7 геометрического сложения, дискриминатор 8, триггер 9, блок 10 формирования комбинаций двоичных сигналов, распределитель 11, элемент ИЛИ 12, элемент И 13, счетчик-делитель 14.

Устройство работает следующим образом.

Сигнал с Л1хода канала связи поступает на вход расщепителя 1, на выходе которого за счет синхронного детектирования с взаимно ортогональными гетеродинными напряжениями образуются квадратурные компоненты X и У входного сигнала. Эти компоненты поступают на вход многоотводной лини 2 задержки в виде напряжений, постоянных на тактовом интервале Т (фиг 2а) и сменяемых на границе между соседними интервалами.

Таким образом, на протяжении интервала обработки Т с выходов многоотводной линии 2 задержки на входы сумматоров 4 подаются N отсчетов компоненты входного сигнала. Далее вводятся следующие обозначения:

1Л

.х

отсчет компоненты сигнала X на i-M тактовом интервале в отводе многоотводной 50 линии задержки (К 1,2,..., N, счет отводов ведется справа налево); помеха;

i-й отсчет компоненты реак- gg ции канала (1 1,2,...,N, счет ведется в естественной временной последовательности) ;

0

0

а.

1

знак i-й информационной посылки, реакция канала на которую целиком укладывается в многоотводной линии 2 задержки.

В блоке 3 оценки импульсной реакции канала связи производится оценка отсчетов gJ данной компоненты реакции канала. Эти оценки в форме медленноменяющихся сигналов поступают с выходов блока 3 на вторые входы перемножителей 5, которые помимо аналоговых (вторых входов) содержат

g дискретные (первые) входы и могут быть вьтолнены в виде электронных ключей, подающих отсчеты реакции с выходов блока 3 на входы сумматоров 4 то с положительным, то с отрица„ тельным весом, в зависимости от знака управляющего напряжения на их первом входе. Перемножители 5 образуют матрицу, причем счет номеров строк 1 ведется снизу вверх, счет номеров

5 столбцов К ведется справа налево, в диагонали объединяют первые входы пе-; ремножителей. Вводя q « К-1 (номер диагонали), имеем для главной диагонали () , С перемещением вправо

Q вверх номер диагонали уменьшается до 1-N, а с перемещением влево вниз увеличивается до N-1. В зависимости от того, с выходом какого блока (6 или 10) соединены первые входы перемножителей 5, они подразделяются на пер- вые (вьш1е главной диагонали, т.е. для q i 0) и вторые перемножители (q 0). Первые перемножители 5 получают управление от регистра 6 сдвига - это информационные символы , являющиеся окончательными оценками для передаваемых символов а

V

,- -1,-21-N

Вторые перемножители 5 получают управление от блока 10 - это информационные символы Ь,, являющиеся пробными значениями (псевдооценками) для а:.а :

Ч

0,1,2,...,N-1

С учетом отрицательного масштабного множителя, который может быть введен или на выходах блока 3, или в перемножителях 5, или на входах сумматоров 4, на выходах сумматоров (номер сумматора совпадает с номером отвода многоотводной линии 2 задерж31332559

ки н столбца матрицы) образуются сигналы , t:

г

(1)

Подставляя (1), получаем с учетом

1.

N

Рм

1 +1 - е Ч р, V

(2) 10

.Р. отсутвие помехи (U «0) и при точной оценке реакции канала связи (ч ( - Ч р X - существует комбинация 1ь, а; , обращающая все о у в 0. В блоке 7 геометрического сложения, осуществляющем сложение квадратов всех(з(,,и ,, при этом происхо15

20

2. В течении i-ro тактового интервала на тактовые входы блока 10 и регистра 6 сдвига не поступает никаких импульсов, но на вторые входы блока 10 с выходов распределителя 11 один за другим поступают 2N импульса, при этом каждый нечетньш импульс (фиг. 2б,г,е,з) поступает также на второй вход триггера 9, устанавливая его в состояние 1 (вход S). Таким образом, триггер 9 в течение тактового интервала N раз устанавливается в состояние 1. Блок 10 выдает соответствующий сигнал,, в результате чего изменяется на противоположный управляющий сигнал bj,. на первых входах перемножителей 5, примыкающих к соответствующей q-й диагонали (q 7/ 0) . Это один из шагов перебора (проба).

Если очередная проба приводит к снижению сигнала на выходе блока 7 геометрического сложения, то на выходе

х,Ь Xt

дит сложение нулей, и на вход дискриминатора 8 поступает минимально возможнь й, нулевой, сигнал.

При наличии помехи или при неточной оценке реакции канала нуль на

выходе блока 7 невозможен, поэтому во

г,7 дискриминатора о возникает импульс,

задачу дискриминатора о входит не рекоторьи поступает на первый вход

триггера 9 и восстанавливает его в нулевое состояние (вход R). При этом на второй вход блока 10 с выхода трИггер-а 9 поступает нулевой сигнал, который препятствует продвижению очередного четного импульса. Таким

гистрация нулевого сигнала, а регистрация минимума среди сигналов, последовательно поступающих на его вход с выхода блока 7; в общем случае этот минимум может иметь место при нару- щении равенства Ь; + л Если неравенство b,vc), 1 -Ki наступает для q О, т.е. на этапе принятия окон- |чательного решения относительно q., то в устройстве в целом происходит ошибка. Если же неравенство bj,., 5

30

35

образом, состояние в блоке 10, приведшее к снижению сигнала на выходе блока 7, сохраняется.

а; наступает при q О (на стадии предварительного решения), то ошибки не происходит, и равенство может быть восстановлено на следующем (i+1)-M тактовом интервале.

При этом-возможны следующие варианты.

Если же очередная проба не приводит к снижению сигнала на выходе блока 7, то дискриминатор 8 не формирует импульс, триггер 9 остается 40 в состоянии 1 и очередной четный импульс (фиг. 2 в,ж,д,и) поступает в блок 10, возвращая соответствующий элемент в нем в исходное состояние, соответствующее начальному усло- 1. На границе между (1-1)-м и i-м 45 вию, заданному на первом этапе тактовыми интервалами производится (сдвиг). Это так же один из шагов пе- установка начальных условий в блоке ребора (возврат). Таким образом, опе- 10, перезапись информационного со- рация пробы осуществляется в элемен- держания (счет ведется справа налево) тах блока 10, а возврат осуществляет50 ся тогда, когда предыдущая проба не приводит к снижению сигнала на выходе блока 7. В результате же происходит целенаправленный перебор чисел b,4tv приводящий к уменьшению отли- в блоке 10 и в регистре 6 сдвига, ко- 55 чия формируемого в матрице ожидаемо- торые образуют единый однотактовый го сигнала от происходящего каналь- сдвигающий регистр из (2N-1) ячеек, ного сигнала, а следовательно, к на вход которого заведен один из дво- уменьшению отличия комбинации {Ь;4 ичных уровней.от {а;+(.

в регистр 6 сдвига и сдвиг информации в нем на один разряд вправо. Эти операции происходят при поступлении тактового импульса. При этом информация последовательно перемещается

5

0

2. В течении i-ro тактового интервала на тактовые входы блока 10 и регистра 6 сдвига не поступает никаких импульсов, но на вторые входы блока 10 с выходов распределителя 11 один за другим поступают 2N импульса, при этом каждый нечетньш импульс (фиг. 2б,г,е,з) поступает также на второй вход триггера 9, устанавливая его в состояние 1 (вход S). Таким образом, триггер 9 в течение тактового интервала N раз устанавливается в состояние 1. Блок 10 выдает соответствующий сигнал,, в результате чего изменяется на противоположный управляющий сигнал bj,. на первых входах перемножителей 5, примыкающих к соответствующей q-й диагонали (q 7/ 0) . Это один из шагов перебора (проба).

Если очередная проба приводит к снижению сигнала на выходе блока 7 геометрического сложения, то на выходе

о

35

образом, состояние в блоке 10, приведшее к снижению сигнала на выходе блока 7, сохраняется.

Последний импульс возврата (фиг 2и) с соответствующего выхода распределителя 11 поступает на счетный вход счетчика-делителя 14, который предварительно установлен в состоянии 1 тактовым импульсом, и на второй вход элемента И 13. Выход счетчика-делителя 14 соединен с первым входом элемента И 13, и, поскольку на этом выходе действует состояние 1, последний импульс возврата с соответствующего выхода распределителя 11 проходит через элемент И 13, а с его выхода - на вход элемента ИЛИ 12 и далее на запускающий вход распределителя 11. После этого повторяется весь цикл работы распределителя 11 и блока 10 формирования комбинаций двоичных символов. Так происходит до тех пор, пока счетчик-делитель 14 не достигает конечного коэффициента деления, тогда на его выходе возникает состояние О, которое не позволяет последнему импульсу возврата с соответствующего выхода распределителя 11 проти через элемент И 13 и элемент ИЛИ 12 и запустить распределитель 11. На фиг. 2 к показаны временные диа- граммы импульсов на запускающем входе распределителя 11, причем одни из этих импульсов являются импульсами, пришедшими по тактовому входу, а другие совпадают с последними из четных импульсов.

На тактовом интервале происходит подбор наилучших значений для Ь,-. при всех q 7, 0. Однако лишь Ь ()

в качестве оценки а транслируется в регистре 6 сдвига и больше не подвергается перебору. Прочие () с очередным тактовым импульсом пере

даются в блок 10 в качестве начального условия и снова подвергаются М- кратным операциям пробы и, при необходимости, возврату.

Существенным отличием предлагаемого устройства от известного является повторный (М-кратный) запуск распределителя 11. При наличии мощных помех или при глубоких и быстрых замираниях в канале связи в известном устройстве не может быть вынесено достоверное решение о символе, следующем непосредственно за участком сигнала, пораженным помехой, так как блок 10 формирования комбинаций двоичных сигналов проводит серию проб и возвратов только один раз. В предлагаемом устройстве за счет повторных серий проб и возвратов решение о принимаемом символе становится- более надежным, при этом производится более полный перебор комбинаций, а некоторое снижение скорости обработки сигнала компенсируется большей помехоустойчивостью.

Формула изобретения

Устройство для демодуляции двоичных сигналов по авт. св. № 1078662, отличающееся тем, что, с целью повышения достоверности принимаемых сообщений, введены последовательно соединенные счетчик-делитель, элемент И и элемент ИЛИ, выход которого подключен к тактовому входу распределителя, соответствуюш 1й выход- которого соединен с вторым входом элемента И и с первым входом счетчика-делителя, второй вход которого соединен с вторым входом элемента ИЛИ и с вторым входом регистра сдвига.

Составитель Д.Куприйчук Редактор В.Петраш Техред И. Попович Корректор В.Бутяга

Заказ 3851/57 Тираж 638Подписное

ВНИИПИ Государственного кою1тета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для демодуляции двоичных сигналов | 1982 |

|

SU1078662A1 |

| Устройство для демодуляции двоичных сигналов | 1987 |

|

SU1515386A2 |

| Устройство для демодуляциидВОичНыХ СигНАлОВ | 1979 |

|

SU794767A1 |

| СПОСОБ ДЕМОДУЛЯЦИИ ДИСКРЕТНЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2102836C1 |

| УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ ДВОИЧНЫХ СИГНАЛОВ | 1989 |

|

SU1809739A1 |

| Нелинейно-нелинейное устройство коррекции межсимвольной интерференции при приеме коррелированного сигнала | 1983 |

|

SU1125750A1 |

| Устройство демодуляции двоичных сигналов | 1980 |

|

SU896788A1 |

| Нелинейно-нелинейный корректор коррелированного сигнала | 1984 |

|

SU1225017A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Ранговый обнаружитель сигналов | 1981 |

|

SU970291A1 |

Изобретение относится к радиосвязи и является дополнительным к изобретению по а.с. № 1078662. Цель изобретения - повышение достоверности принимаемых сообщений. Устр-во содержит расщепитель 1 сигнала на низкочастотные компоненты, многоотводную ЛЗ 2, блок 3 оценки импульс-Ч ной реакции канала связи, сумматоры 4, перемножители 5, регистр сдвига 6, блок 7 геометрического сложения, дискриминатор 8, триггер 9, блок 10 формирования комбинаций двоичных сигналов, распределитель 11, элементы ИЛИ 12, И 13 и счетчик-делитель 14. Расщепитель 1 формирует квадратурные компоненты входного сигнала в виде напряжений, постоянных на тактовом интервале и сменяемьк на границе между соседними интервалами, которые поступают на многоотводную ЛЗ 2. В блоке 3 производится оценка отсчетов компоненты реакции канала. Эти оценки в виде медленноменяющих- ся сигналов поступают на перемножители 5, образующие матрицу. Перемножителями управляют регистр сдвига 6 и блок in. Введены элементы ИЛИ 12, И 13 и счетчик-делитель 14.7. ил. (Л 1Ч Фиг1

| Устройство для демодуляции двоичных сигналов | 1982 |

|

SU1078662A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-08-23—Публикация

1985-10-21—Подача