113224

Изобретение относится к измерительной и вычислит шьной технике и может быть использовано в линейных и нелинейных преобразователях напряжения в воичный позиционный код с наносе- 5 кундными временам- преобразования, а так же для цифрового представления видеосигналов радио или промеясуточ- ной частоты без преобразования в ана- оговый сигнал.10

Цель изобретения - расширение функ- ионапьных возможностей аналого-цифрового преобразователя ( АЦП и повыение его надежности при измерении параметров радиочастотных сигналов, 5

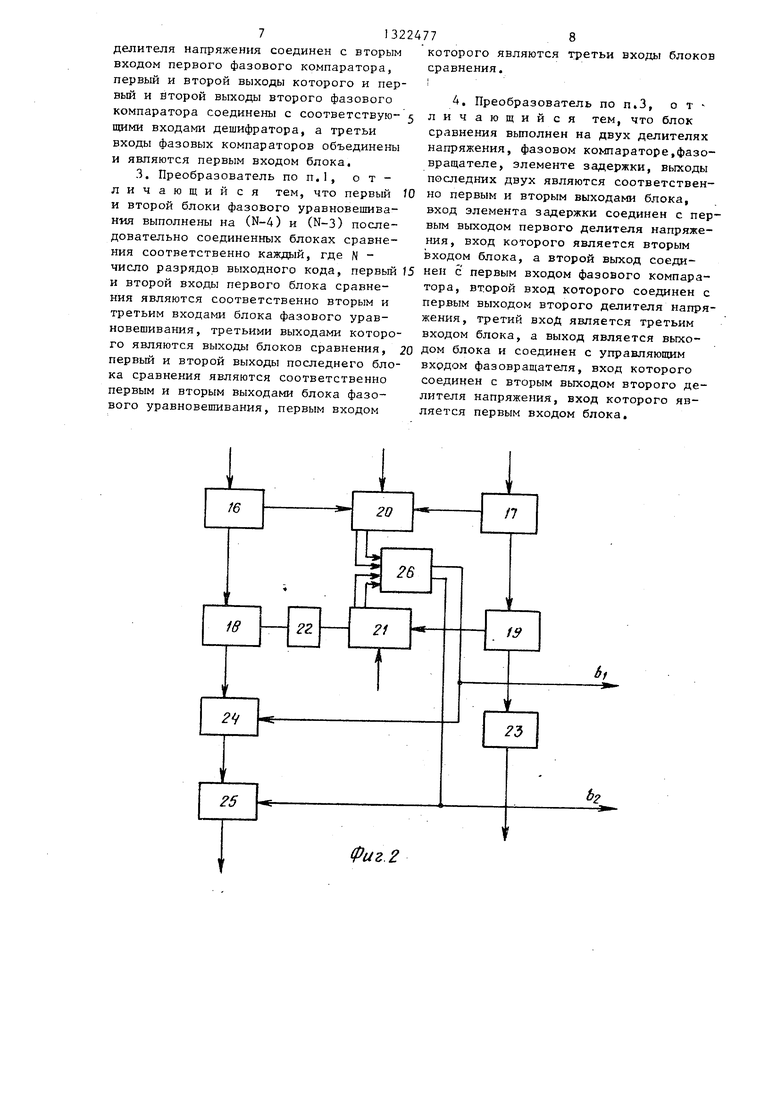

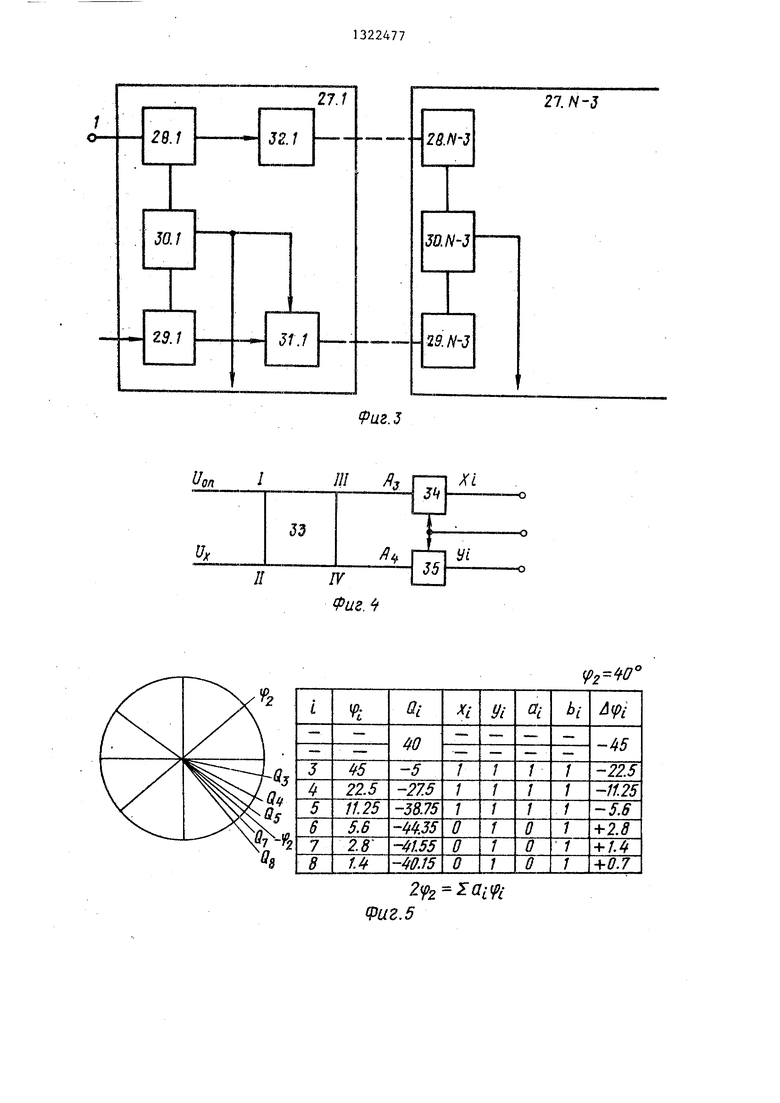

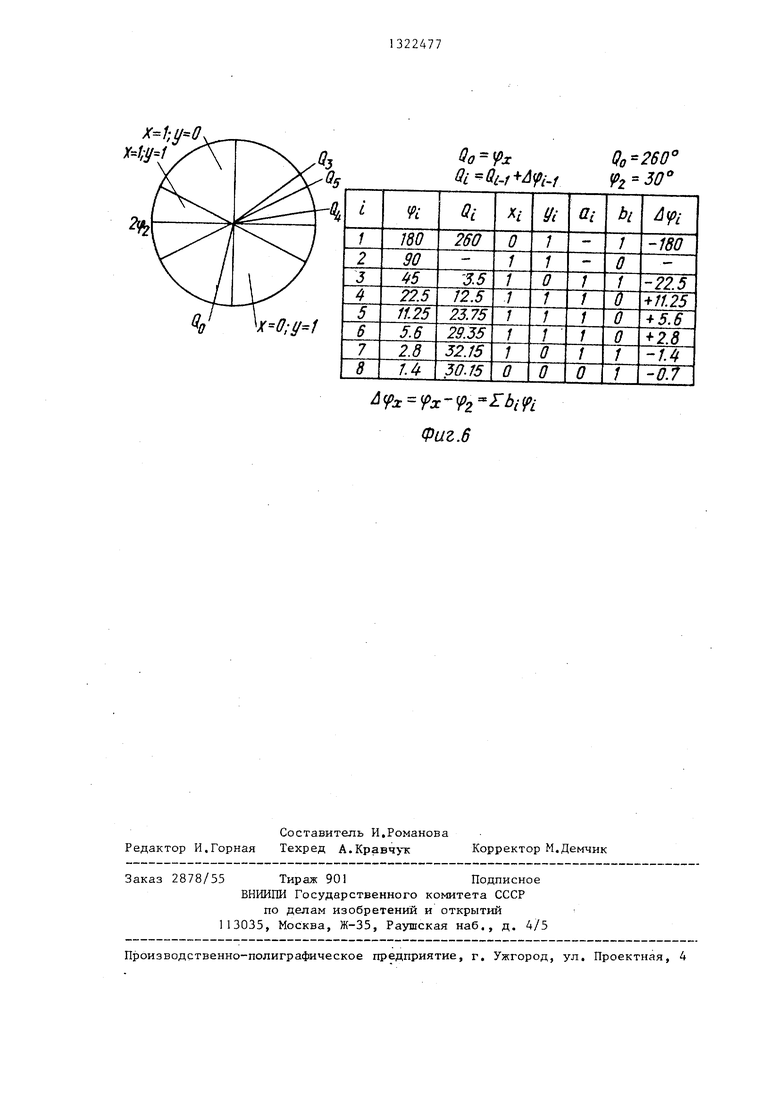

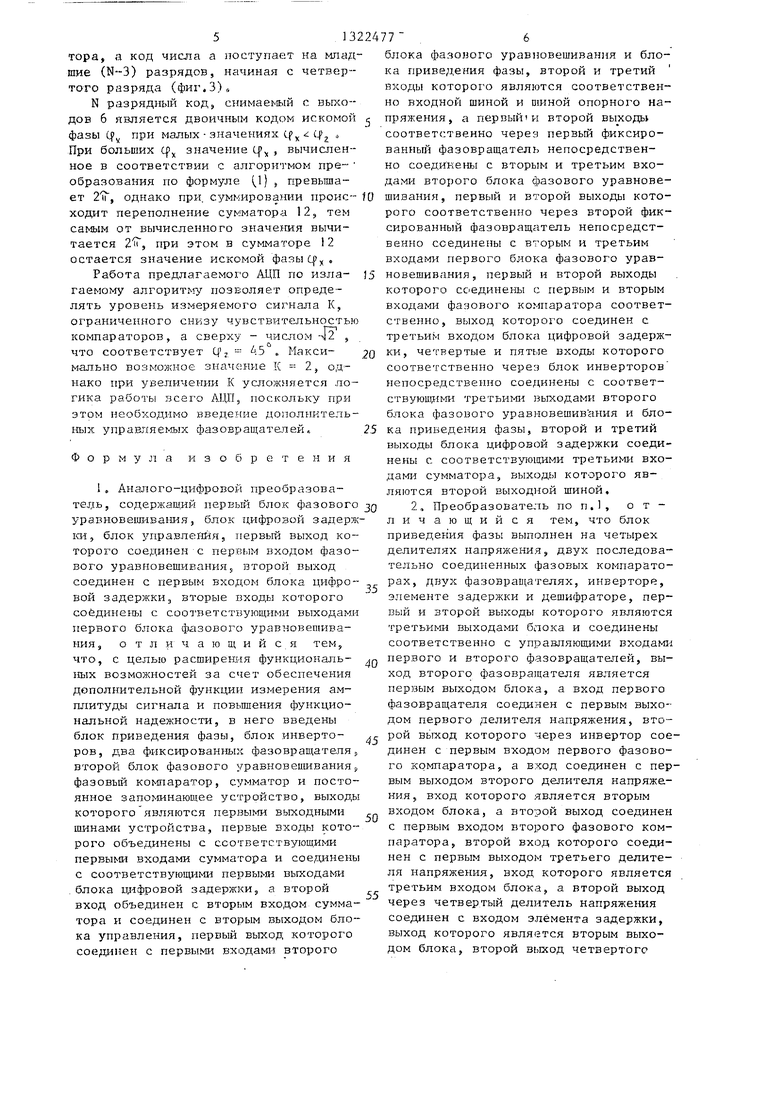

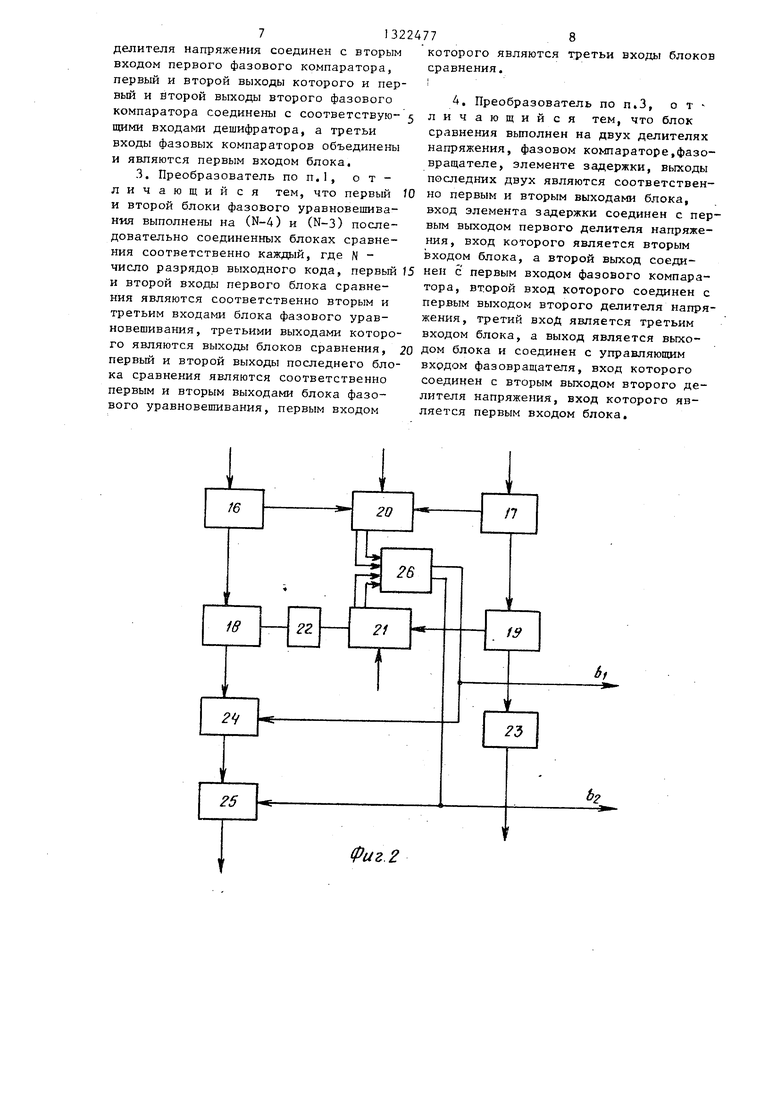

На фиг.1 представлена функциональная схема нрер,лагаемого АЦП; па фиг.2 - функциональная схема блока приведения фазы; на - функциональная схема блока фазового уравно- 20 вешивания ; на фиг «4 -- пример реализации фазового компаратора на фиг,5 диаграмма и таблица, характеризующие процесс компенсации фазы сигнала; на диаграмма и таблица измерения 25 граничного значения tfp ,

На диаграммах и в таблицах (фиг.5 и б) обозначены измеряемое значе1ше (п фазы, граничное значение Cf фазы, опорная величина ср: фазовых сдвигов 30 сигналов в i разряде,, приращение йср; фазового сдвига сигнала в соответствующем разряде, результирующее значение. Q; фазы сигнала, логические переменные X,, у, , и х,, у первого и 5 второго фазовых компараторов блока приведения фазы к первому квадранту., выходные значения b и Ь кода логического блока, соответствуюш,ие 180 и 90°.40

АЦП содержит входную шину I , un-J- ну 2 опорного напряжения, второй блок 3 фазового уравновешивания,, блок 4 цифровой задержки, блок 5 управления j вторую выходную шину 6, 45 блок 7 приведения .фазы сигнала в первый квадрант, первьш фикси1 ованный фазовращатель 8, блок 9 инверторов, BTopovi фиксированный фазовращатель 10, первый блок 11 фазового уравновегаива 5о ния, сумматор 12, постоянное запоминающее устройство 13, первую выходную шину 14, фазовый компаратор 15

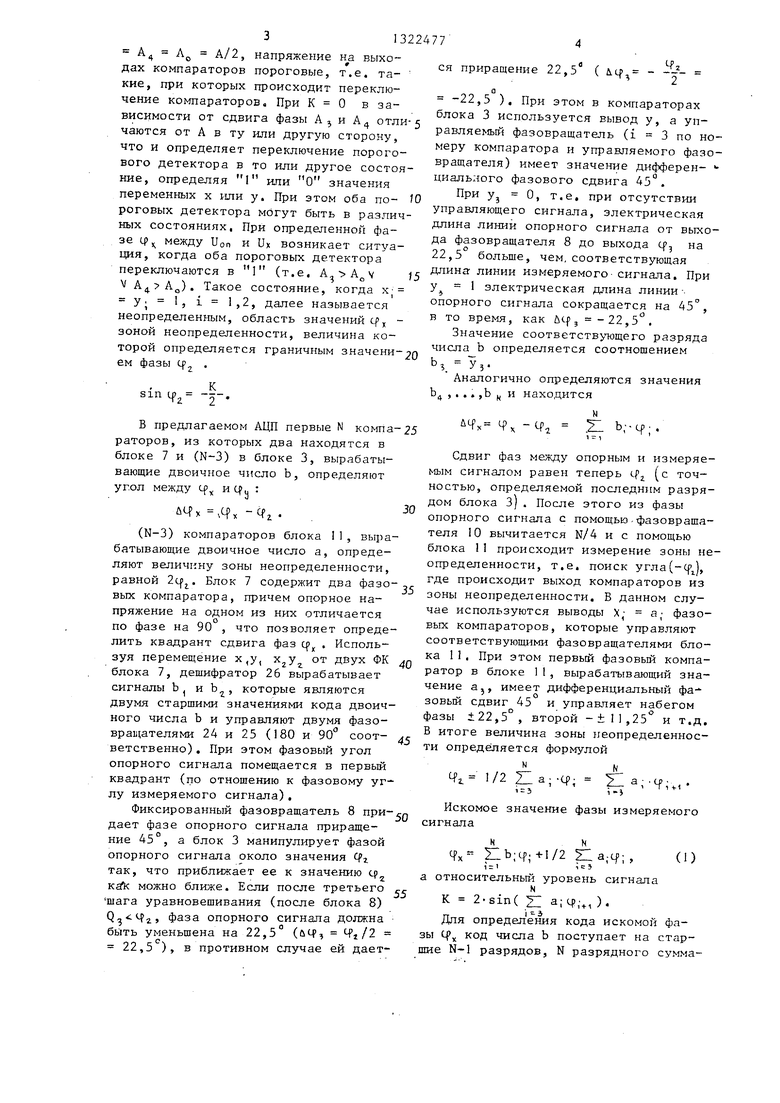

Блок 7 приведения фазы в первый квадрант (фиг.2) содержит две пары делителей напряжения 16, 17 и 18, 19, фазовые компараторы 20 и 21, инвертор 22, элемент 23 за,аерж:ки, первый 24

5 0

5

0 5

0 5 0

5 о

5

77 ,2

и второй 25 фазовращатели, дешифратор 26.

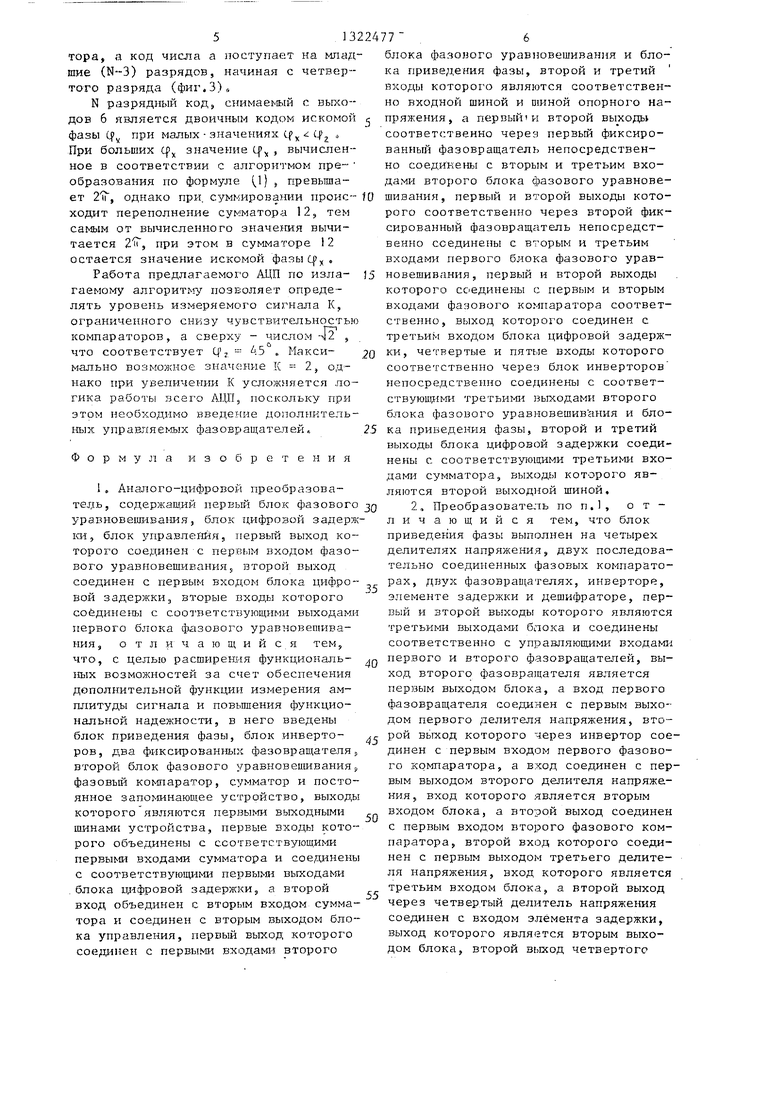

Первый 11 и второй 3 блоки фазового уравновешивания состоят из N-3 и М-4 последовательно соединенных- блоков 27 сравнения, каждый из кото- pbfx выполнен на двух делителях 28 и 29 найряжения, фазовом компараторе 30, фазовращатепе 31, элементе 32 задержки.

Фазо})ый компаратор выполнен на СВЧ-мосте 33 и дву;х: пороговых детекторах 34 и 35,

Блок 7 .предназначен для приведения сдвига фазы опорного и измеряемого сигналов в первый квадрант.

Два ФК, входящие в блок 7, образуют квадратурную схему по определению квадранта сдвига фаз измеряемого и опорного сигналов. Дешифратор 26 по сигналам х,, х, у,, у двух фазовых компараторов 20 и 21 блока 7 формирует сигналы Ъ, и bj, управляющие фазо- вращателягум 24 и 25, осуществляющими сдвиг фазы на 180 и 90 соответственно „

Фиксированные фазовращатели 8 и 10 дают приращение-фазы опорного сигнала 45 (фиг„5) для фазового уравнове- ишвания.

Разрядный сумматор 12 предназначен для сумм1-1рования двух чисел а и Ь, при этом число b подключено к старшим N- разрядам, а число а - к последним N-3 разрядам, в это время к остальным разрядам подключен логический О

Аналого-цифровой преобразователь работает следующим образом.

Мощности преобразуемого и опорного сигналов, представляющие радиочастот- шле (СВЧ) сигналы в блоках 7, 3 и 11 с помощью делителей напряжения равно мерно распределяются между компараторами.

Когда на первый и второй выходы любого из фазовых компараторов поступают сигналы 1 - а sin cot и U B(t) sinCut-tpCt) , на выходах моста 33,, входящего в состав компаратора, появляются колебаршя с амплитудами Ад и А4 соответственно.

А f 2K-sin4)J,

где К В/А.

Режим пороговых детекторов 34 и 35 выбирается так, что при отсутствии измеряемого сигнала, когда К О и А

313224

Ajj A/2, напряжение на выходах компараторов пороговые, т.е. та- кие, при которых происходит переключение компараторов. При К О в зависимости от сдвига фазы А и А о тли-5 чаются от А в ту или другую сторону, что и определяет переключение порогового детектора в то или другое состояние, определяя I или О значения переменных х или у. При этом оба по- )0 роговых детектора могут быть в различных состояниях. При определенной фазе q между Uon и Ux возникает ситуация, когда оба пороговых детектора

переключаются в I (т.е. А,, А v

V ), Такое состояние, когда х; у. 1, ,2, далее называется неопределенным, область значений ср - зоной неопределенности, величина которой определяется граничным значени-20 ем фазы Ц). .

sin 2

В предлагаемом АЦП первые N компараторов, из которых два находятся в блоке 7 и (N-3) в блоке 3, вырабатывающие двоичное число Ь, определяют угол между cf ч

s4 x

(N-3) компараторов блока I1, вырабатывающие двоичное число а, определяют величину зоны неопределенности, равной Zcfj. Блок 7 содержит два фазовых компаратора, причем опорное напряжение на одном из них отличается по фазе на 90 , что позволяет определить квадрант сдвига фаз ( , Используя перемещение х ,у, , от двух ФК блока 7, дешифратор 26 вырабатывает сигналы Ь и Ъ, которые являются двумя старшими значениями кода двоичного числа b и управляют двумя фазо- врацателями 24 и 25 (180 и 90 соот- ветственно), При этом фазовый угол опорного сигнала помещается в первый квадрант (по отношению к фазовому уг лу измеряемого сигнала),

Фиксированный фазовращатель 8 придает фазе опорного сигнала приращение 45°, а блок 3 манипулирует фазой опорного сигнала около значения Cf так, что приближает ее к значению ср KsfK можно ближе. Если после третьего шага уравновешивания (после блока 8) Q ц, фаза опорного сигнала должна быть уменьшена на 22,5 (ьЧ., Ч г/2 22,5), в противном случае ей дает77

5 0,

5

0

5

°

, д

ся приращение 22,5 (лср - -

а

-22,3 ). При этом в компараторах блока 3 используется вывод у, а управляемый фазовращатель (i 3 по номеру компаратора и управляемого фазовращателя) имеет значение дифферен- диальлого фазового сдвига 45.

При у 0, т.е. при отсутствии управляющего сигнала, электрическая длина линии опорного сигнала от выхода фазовращателя 8 до выхода ср на 22,5 больше, чем, соответствующая длина линии измеряемого-сигнала. При у 1 электрическая длина линии-- опорного сигнала сокращается на 45, в то время, как , 22,5 .

Значение соответствующего разряда числа b определяется соотношением

b S. У 5

Аналогично определяются значения

Ь , , .. ,Ь , и находится

N

йЧ х tf, -tf . b;-cp;. 1 1

Сдвиг фаз между опорным и измеряемым сигналом равен теперь ср (с точностью, определяемой последним разрядом блока З). После этого из фазы опорного сигнала с помощью-фазовраша- теля 10 вычитается N/4 и с помощью блока 1I происходит измерение зоны неопределенности, т.е. поиск угла(-ср), где происходит выход компараторов из зоны неопределенности. В данном случае используются выводы X; а; фазовых компараторов, которые управляют соответствуюшд1ми фазовращателями блока 1 1 , При этом первьй фазовый компаратор в блоке 11, вырабатывающий значение а,, имеет дифференциальный фа зовый сдвиг 45 и управляет набегом

о -о

фазы ± 22,5 , второй -±11,25 и т.д. В итоге величина зоны неопределенности определяется формулой

4, 1/2 Ila- if- Z:a;.cf;,. 1-31-}

Искомое значение фазы измеряемого сигнала

cfx 21Ьч|.; 1-1/2 a;t|.;, (1)

1 : 11 3

а относительный уровень сигнала

К 2.sin( Z: а;Ч),ч,).

Для определения кода искомой фазы tp код числа b поступает на старшие N-1 разрядов, N разрядного сумматора, а код числа а поступает на младшие (N--3) разрядов, начиная с четвертого разряда (фиг,3)„

N разрядный код, снимаемьдй с выходов 6 является двоичным кодом искомой фазы СУ гфи малых значениях tf i ilj ., При больших tp значение Ц , вычисленное в соответствии с алгоритмом образования но формуле (1) , превышает 2 ir, однако при. суммироватш проис--fO шивания, первый и второй выходы котоходит переполнение сумматора 12, тем самым от вычисленного значения вычитается Z H , при этом в сумматоре 12 остается значение искомой фазыср.

Работа предлагаемого АЦП по излагаемому aлгopит гy позволяет определять уровень измеряемого сигнала К, ограниченного снизу чувствитешьностью компараторов, а сверху - числом , что соответствует Q j - А5 . Максимально возможное зна чение К 2, однако при увеличении К усложняется логика работы всего АЦП, поскольку при этом необходимо х ведение дополнительных управляемых фазовращателей,.

Формула изобретения

1, Аналого-цифровой преобразова- тедь, содержащий первый блок фазового уравновешивания, блок цифровой задержим, блок управления, первый выход которого соединен с первым входом фазового уравновещиваниЯ;. второй выход соединен с первым входом блока дифро- вой задержки, вторые входы которого соединены с соответствующими выходами первого блока ф 13ового уравновешивания, отличающийся тем, что, с делыо расширения функционапь- laix возможностей за счет обеспечения дополнительной функции измерения амплитуды сигнала и повьпления функциональной надежности, в него введены блок приведения фазы, блок инверторов, два фиксированных фазоврап- атепя второй блок фазового уравновеишванияj фазовьм компаратор, сумматор и постоянное запоминающее устройство, выхорД)

которого являются первыми выходными шинами устройства, первые входы которого объединены с соответствующими первыми входами сумматора и соединены с соответствующими пepвы п выходами . блока ПД1ФРОВОЙ задержки, а второй вход объединен с вторым входом сумматора и соединен с вторым выходом блока управления, первый выход, которого соеданен с первыми входами второго

2477 .6

блока фазоного уравновешивания и блока приведения фазы, второй и третий входы которого являются соответственно входной шиной и шиной опорного напряжения, а первый И второй выходь соответственно через первый фиксированный фазовращатель непосредственно соединены с вторым и третьим входами второго блока фазового уравновеJQрого соответственно через второй фиксированный фазовращатель непосредственно соединены с вторым и третьим входами первого блока фазового урав15 новешивания, первый и второй выходы которого сс единены с первым и вторым входами фазового компаратора соответственно, вЕ)1ход которого соединен с третьим входом блока цифровой задерж0 ки, четвертые и пятые входы которого соответственно через блок инверторов непосредствепно соединены с соответствующими третьими )зыходами второго блока фазового уравновешивания и бло25 ка приведения фазы, второй и третий выходы блока цифровой задержки соединены с соответствующими третьими входами сумматора, выход,1 которого являются второй выходной шиной,

2. Преобразователь по п.1, отличающийся тем, что блок приведения фазы выполнен на четырех делителях напряжения, двух последовательно соединенных фазовых компараторах, двух фазовращателях, инверторе, элементе задержки и дешифраторе, первый и второй вь ходы которого являются третьими выходами блока и соединены соответственно с управляющими входами первого и второго фазовращателей, выход второго фазовращателя является первым выходом блока, а вход первого фазовращателя соединен с первым выходом первого делителя напряжения, второй вьтход которого через инвертор соединен с первым входом первого фазового компаратора, а вход соединен с первым выходом второго делителя напряже35

40

45

ния, вход которого является вторым входом блока, а второй выход соединен с первым входом второго фазового компаратора, второй вход которого соединен с первым выходом третьего делителя напряжения, вход которого является третьим входом блока, а второй выход через четвертый делитель напряжения соединен с входом элемента задержки, выход которого является вторым выходом блока, второй выход четвертого

делителя напряжения соединен с входом первого фазового компаратора, первый и второй выходы которого и первый и Второй выходы второго фазового компаратора соединены с соответствую- щими входами дешифратора, а третьи входы фазовых компараторов объединены и являются первым входом блока.

3. Преобразователь по п.1, отличающийся тем, что первый и второй блоки фазового уравновешивания выполнены на (N-4) и (N-3) последовательно соединенных блоках сравневторым

4, Преобразователь по п.З, отличающийся тем, что блок сравнения вьтолнен на двух делителях напряжения, фазовом компараторе,фазовращателе, элементе задержки, выходы последних двух являются соответственно первым и вторым выходами блока, вход элемента задержки соединен с первым выходом первого делителя напряжения, вход которого является вторым входом блока, а второй выход соединия соответственно каждый, где N - число разрядов выходного кода, первый 15 нен с первым входом фазового компара- и второй входы первого блока сравне- тора, второй вход которого соединен с кия являются соответственно вторым и третьим входами блока фазового уравновешивания, третьими выходами которо- входом блока, а выход является выхо- го являются выходы блоков сравнения, 20 Дом блока и соединен с управляющим первый и второй выходы последнего блока сравнения являются соответственно первым и вторым выходами блока фазового уравновешивания, первым входом

первым выходом второго делителя напряжения, третий вход является третьим

входом фазовращателя, вход которого соединен с вторым выходом второго делителя напряжения, вход которого является первым входом блока.

тора, и перовогоствую- j тьи динены

1322477

вторым которого являются сравнения.

4, Преобразователь по п.З, отличающийся тем, что блок сравнения вьтолнен на двух делителях напряжения, фазовом компараторе,фазовращателе, элементе задержки, выходы последних двух являются соответственно первым и вторым выходами блока, вход элемента задержки соединен с первым выходом первого делителя напряжения, вход которого является вторым входом блока, а второй выход соединен с первым входом фазового компара- тора, второй вход которого соединен с входом блока, а выход является выхо- Дом блока и соединен с управляющим

нен с первым входом фазового компара- тора, второй вход которого соединен с входом блока, а выход является выхо- Дом блока и соединен с управляющим

первым выходом второго делителя напряжения, третий вход является третьим

нен с первым входом фазового компара- тора, второй вход которого соединен с входом блока, а выход является выхо- Дом блока и соединен с управляющим

входом фазовращателя, вход которого соединен с вторым выходом второго делителя напряжения, вход которого является первым входом блока.

27.1

о29.1

32.1

30.1

27. А/-J

28.N-3

30.N-3

| название | год | авторы | номер документа |

|---|---|---|---|

| КВАЗИКОГЕРЕНТНЫЙ МОДУЛЯТОР СИГНАЛОВ КВАДРАТУРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2581646C1 |

| Устройство для обратного тригонометри-чЕСКОгО пРЕОбРАзОВАНия | 1979 |

|

SU849239A1 |

| ГЕНЕРАТОР С РАЗДЕЛЬНОЙ ЦИФРОВОЙ РЕГУЛИРОВКОЙ ЧАСТОТЫ И ФАЗЫ ИМПУЛЬСОВ | 2000 |

|

RU2168268C1 |

| Измеритель разности фаз | 1977 |

|

SU711492A1 |

| Цифровой фазовращатель | 2024 |

|

RU2823429C1 |

| Фазометр | 1991 |

|

SU1817037A1 |

| Формирователь сложного сигнала с частотной и частотно-фазовой манипуляцией | 1982 |

|

SU1136323A1 |

| УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ МНОГОФАЗНОГО ПЕРИОДИЧЕСКОГО СИГНАЛА | 1991 |

|

RU2017063C1 |

| КВАЗИКОГЕРЕНТНЫЙ ДЕМОДУЛЯТОР СИГНАЛОВ КВАДРАТУРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2582331C1 |

| Цифровой измеритель фазовых флуктуаций сигналов | 1986 |

|

SU1368805A1 |

Изобретение может быть использовано в линейных и нелинейных преобразователях напряжения в двоичный позиционный код с наносекундными временами преобразования. Цель изобретения - расширение функциональных возможностей путем одновременного измерения амплитуды и фазы радиосигнала и повышение надежности. Для этого в аналого-цифровой преобразователь, содержащий первый блок 11 фазового уравновешивания, блок 5 управления и блок 4 цифровой задержки, введены блок 9 инверторов, блок 7 приведения фазы сигнала в первый квадрант, два фиксированных фазовращателя 8 и 10, второй блок 3 фазового уравновешивания, сумматор 12 и постоянное запоминающее устройство 13. Входное напряжение на входе I сравнивается в блоке 7 с опорным напряжением, определяется номер квадранта, к которому относится разность фаз измеряемого и опорного сигналов, и находятся значения первых двух старших разрядов цифрового кода результата. Затем фазовращатель 8 придает фазе приращение 45 , а блок 3 осуществляет ее измерение, последовательно находя алгебраическую сумму опорных сдвигов фазы, равных 45 /2. Изменение зоны неопределенности, оставшейся после блока 3, осуществляет блок 11. Выходы блоков 7, 3, II через блок цифровой задержки 4 подаются на двоичный сумматор 12, выходы которого являются результирующим кодом фазы, а выход 14 постоянного запоминающего устройства 13, осуществляющего преобразование типа sinx, дает значение относительного уровня сигнала. .3 3.п. ф-лы, 6 ил. § (Л 00 ND ЬО vl

Z9.N-d

ФигЛ

fpLLZ. J

9

(

2(

.5

Qo x Qi di-f- i-f

2 30°

Составитель И.Романова Редактор И.Горная Техред А.КравчукКорректор М.Демчик

Заказ 2878/55 Тираж 901Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

Фаг.6

| Аналого-цифровой преобразователь | 1976 |

|

SU571896A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Автометрия | |||

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Зубчатое колесо со сменным зубчатым ободом | 1922 |

|

SU43A1 |

Авторы

Даты

1987-07-07—Публикация

1985-02-25—Подача