Пуск

рг

Изобретение относится к функциональным аналого-цифровым преобразователям и предназначено для использования в приборостроении, управляющих и информационно-измерительных системах

Цель изобретения - расширение области применения за счет обеспечения формирования экспоненциальной зависимости выходных сигиалоВо

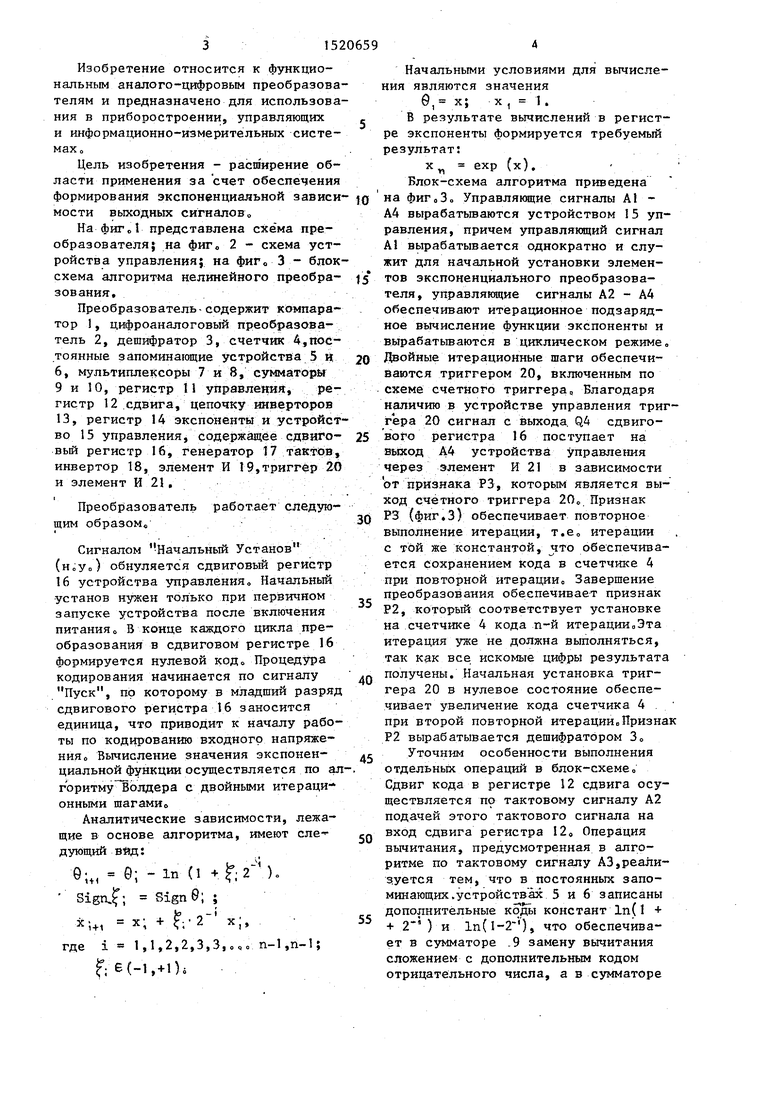

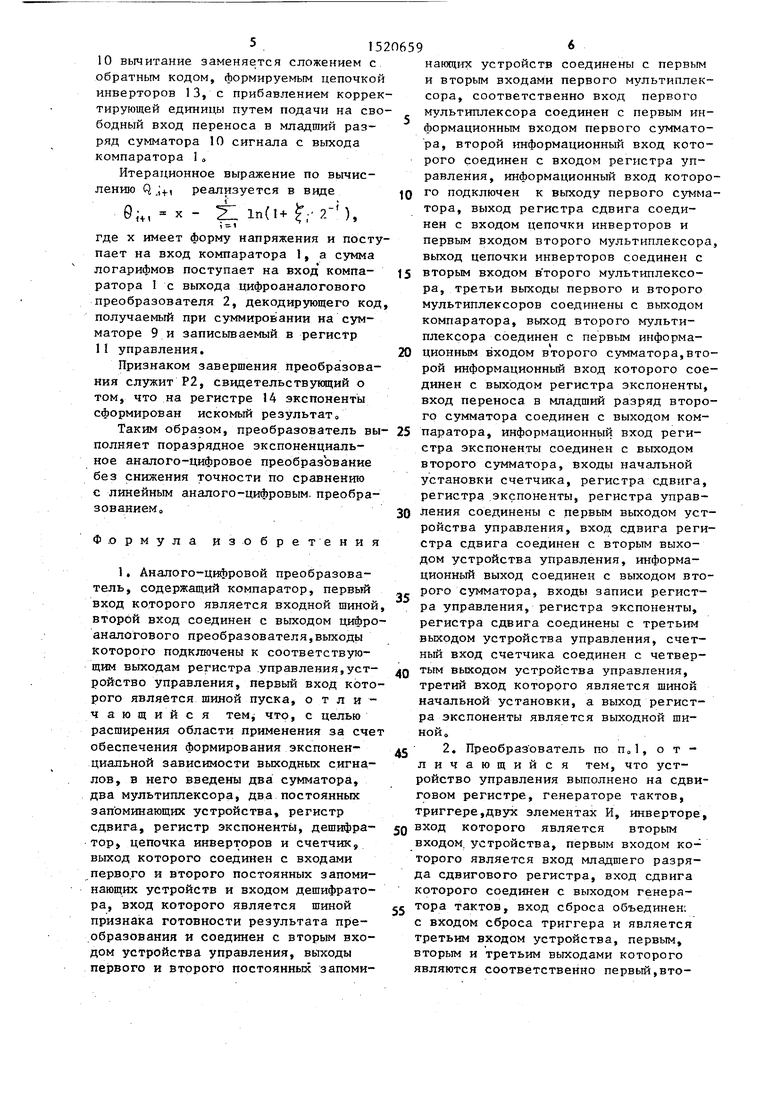

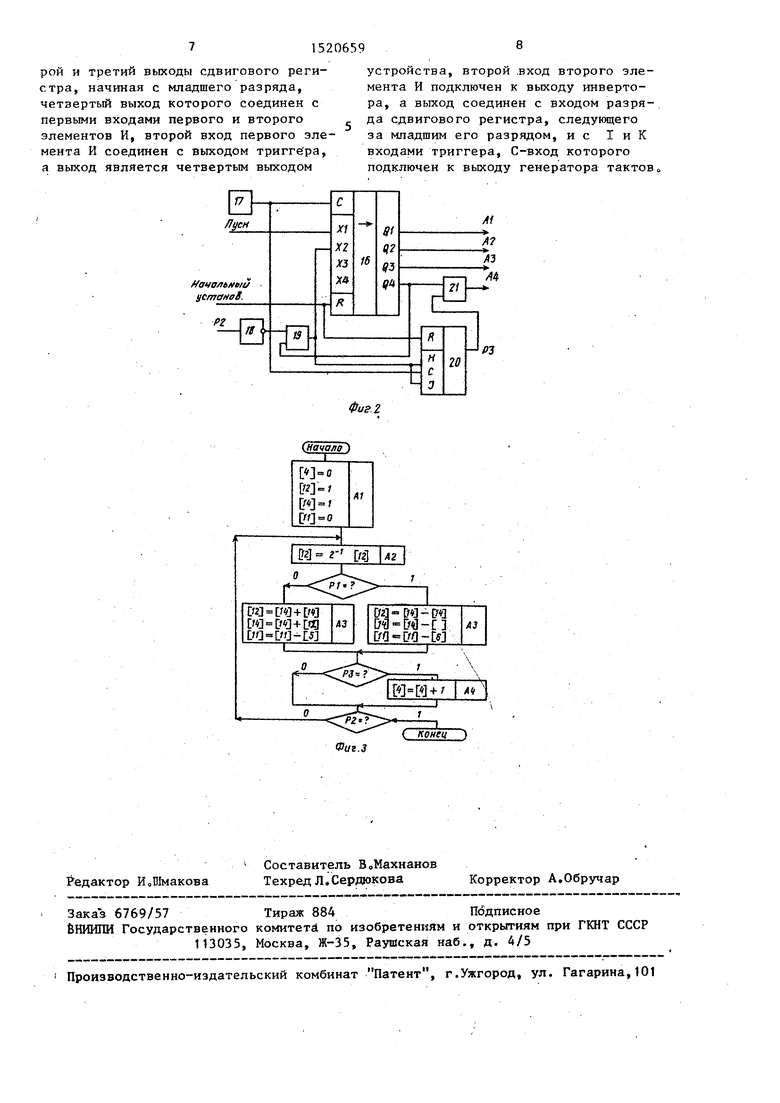

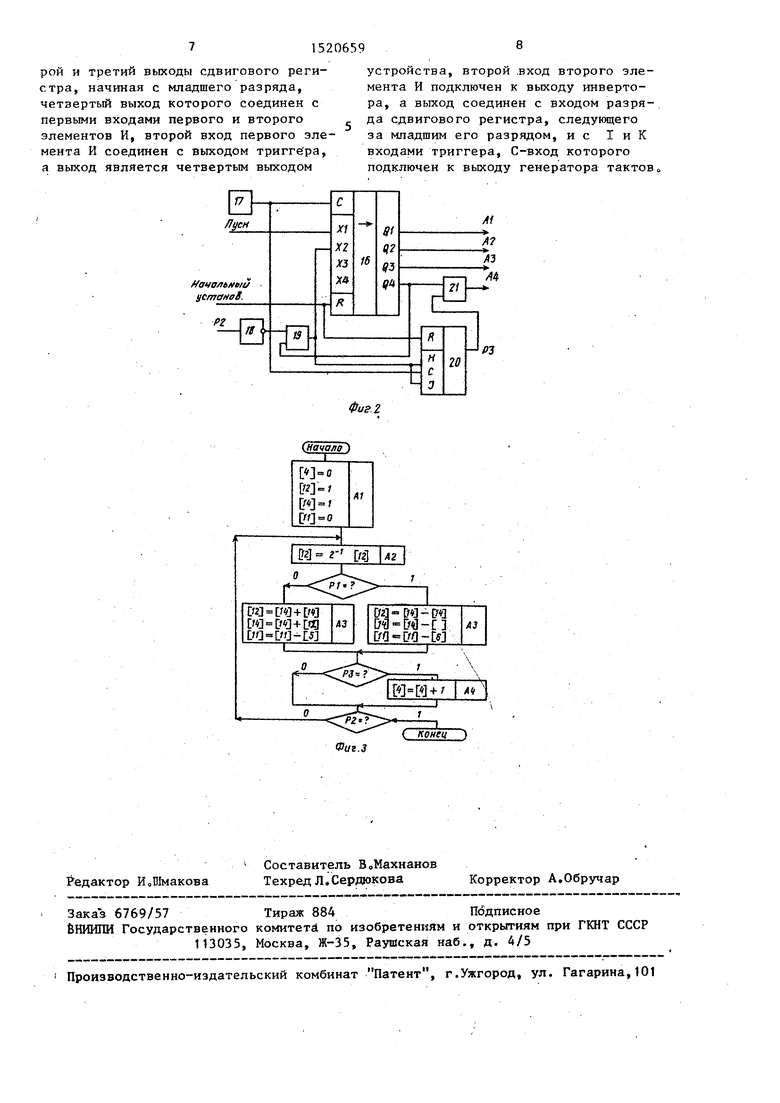

На фиг о 1 представлена схема преобразователя; на фиг« 2 - схема устройства управления; на фиГо 3 - блок схема алгоритма нелинейного преобразования.

Преобразователь-содержит компаратор , цифроаналоговый преобразователь 2, дешифратор 3, счетчик 4,постоянные запоминающие устройства 5 И 6, мультиплексоры 7 и 8, сумматора 9 и 10, регистр 11 управлеиияг, регистр 12 сдвига, цепочку инверторов 13, регистр 14 экспоненты и устройство 15 управления, содержащее сдвиговый регистр 16, генератор 17 тактов, инвертор 18, элемент И 19,триггер 20 и элемент И 21,

Преобразователь работает следующим образом.

Сигналом Начальный Установ (ноУо) обнуляется сдвиговый регистр 16 устройства управления. Начальный установ нужен только при первичном запуске устройства после включения питанияо В конце каждого цикла преобразования в сдвиговом регистре 16 формируется нулевой код Процедура кодирования начинается по сигналу Пуск, по которому в младший разряд сдвигового регистра 16 заносится единица, что приводит к началу работы по кодированию входного напряжения Вычисление значения экспоненциальной функции осуществляется по ал горитмуЧВолдера с двойными итерационными шагамио

Аналитические зависимости, лежащие в основе алгоритма, имеют сле- дующий Вид:

QU, 0; -ш (1 Г;2 Ь.

Sigruf; Sign0; ;

1+1

х; ч- ;-2- : где i 1,1,2,2,3,3,, f;6(-l,-H).

ч

5

0

5

0

5

0

5

0

5

Начальными условиями для вычисления являются значения 0, х; х, 1.

В результате вычислений в регистре экспоненты формируется требуемый результат:

х ехр (х).

Блок-схема алгоритма приведена на фиГоЗо Управлякщие сигналы А1 - А4 вырабатьдааются устройством 15 управления, причем управляющий сигнал А1 вырабатывается однократно и служит для начальной установки элементов экспоненциального преобразователя, управляющие сигналы А2 - А4 обеспечивают итерационное подзаряд- ное вычисление Функции экспоненты и вырабатьгоаются в циклическом режиме ойные итерационные шаги обеспечиваются триггером 20, включенным по схеме счетного триггера„ Благодаря наличию в устройстве управления триггера 20 сигнал с выхода, Q4 сдвигового регистра 16 поступает на вьпсод А4 устройства управления через элемент И 21 в зависимости от признака РЗ, которым является выход счетного триггера 20о Признак РЗ (фиг.З) обеспечивает повторное выполнение итерации, т.е, итерации с той же константой, что обеспечивается сохранением кода в счетчике 4 при повторной итерациио Завершение преобразования обеспечивает признак Р2, который соответствует установке на счетчике 4 кода п-й итерацииоЭта итерация уже не должна выполняться, так как все искомые цифры результата получены. Начальная установка триггера 20 в нулевое состояние обеспечивает увеличение кода счетчика 4 . при второй повторной итерацииоПризнак Р2 вырабатывается дешифратором 3,

Уточним особенности выполнения отдельньк операций в блок-схеме Сдвиг кода в регистре 12 сдвига осуществляется по тактовому сигналу А2 подачей этого тактового сигнала на вход сдвига регистра 12, Операция вычитания, предусмотренная в алгоритме по тактовому сигналу АЗ,реаЛи- з.уется тем, что в постоянных запоминающих.устройствах 5 и 6 записаны дополнительные кодь констант 1п( 1 + + 2 ) и ln() что обеспечивает в сумматоре .9 замену вычитания сложением с дополнительным кодом отрицательного числа, а в сумматоре

10 вычитание заменяется сложением с обратным кодом, формируемым цепочкой инверторов 13, с прибавлением корректирующей единицы путем подачи на свободный вход переноса в младший разряд сумматора 10 сигнала с выхода компаратора К

Итерационное выражение по вычислению Q ,i., реализуется в виде

X

1п(К,. .- ),

где X имеет форму напряжения и поступает на вход компаратора 1, а сумма логарифмов поступает на вход компаратора I с выхода цифроаиалогового преобразователя 2, декодирующего код получаемый при суммировании на сумматоре 9 и записьшаемый в регистр 1I управления.

Признаком завершения преобразования служит Р2, свидетельствзгкяций о том, что на регистре 14 экспоненты сформирован искомый результат

Таким образом, преобразователь вы полняет поразрядное экспоненциальное аналого-цифровое преобразование без снижения точности по сравнению с линейным аналого-цифровым, преобразованием

Формула изобретения

1. Аналого-цифровой преобразователь, содержащий компаратор, первый вход которого является входной шиной второй вход соединен с выходом цифро аналогового преобразователя,выходы которого подключены к соответствующим выходам регистра .управления,устройство управления, первый вход которого является шиной пуска, о т л и - ч ающийс я тем что, с целью расширения области применения за сче обеспечения формирования экспоненциальной зависимости выходных сигна,- лов, в него введены два: сумматора, два мультиплексора, два постоянных запоминающих устройства, регистр сдвига, регистр экспоненты, дешифратор, цепочка инверторов и счетчик, выход которого соединен с входами первого и второго постоянных запоминающих устройств и входом дешифратора, вход которого является шиной признака готовности результата преобразования и соединен с вторым входом устройства управления, выходы первого и второго постоянных запоми0

5

0

5

0

5

0

нающих устройств соединены с первым и вторым входами первого мультиплексора, соответственно вход первого мультиплексора соединен с первым информационным входом первого сумматора, второй шформационный вход которого соединен с входом регистра управления, информационный вход которого подключен к выходу первого сумматора, выход регистра сдвига соединен с входом цепочки инверторов и первым входом второго мультиплексора, выход цепочки инверторов соединен с вторым входом в торого мультиплексора, третьи выходы первого и второго мультиплексоров соединены с выходом компаратора, выход второго мультиплексора соединен с первым информационным входом второго сумматора,второй информационный вход которого соединен с выходом регистра экспоненты, вход переноса в младший разряд второго сумматора соединен с выходом компаратора, информационный вход регистра экспоненты соединен с выходом второго сумматора, входы начальной установки счетчика, регистра сдвига, регистра экспоненты, регистра управления соединены с первым выходом устройства управления, вход сдвига регистра сдвига соединен с вторым выходом устройства управления, информационный выход соединен с выходом второго сумматора, входы записи регистра управления, регистра экспоненты, регистра сдвига соединены с третьим вькодом устройства управления, счет- ньй вход счетчика соединен с четвертым выходом устройства управления, третий вход которого является шиной начальной установки, а выход регистра экспоненты является выходной шиной.

45

По 1

о т 2. Преобраз ователь по личающийся тем, что устройство управления вьтолнено на сдвиговом регистре, генераторе тактов, триггере,двух элементах И, инверторе 5Q вход которого является вторым входом, устройства, первым входом которого является вход младшего разряда сдвигового регистра, вход сдвига которого соединен с выходом генератора тактов, вход сброса объединен; с входом сброса триггера и является третьим входом устройства, первым, вторым и третьим выходами которого являются соответственно первый,вто55

Начальный установ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1989 |

|

SU1690195A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1612374A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1686697A1 |

| Цифровой фазометр | 1986 |

|

SU1368807A1 |

| Масштабирующий преобразователь | 1982 |

|

SU1038880A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2006936C1 |

| Цифровой нелинейный масштабирующий преобразователь | 1981 |

|

SU1057953A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2455682C1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2459241C1 |

Изобретение предназначено для использования в качестве функционального преобразователя для ввода аналоговой информации в микро- и мини- ЭВМ и может найти применение в приборостроении, управляющих и информационно-измерительных системах. В устройстве решается задача расширения области применения за счет обеспечения формирования экспоненциальной зависимости выходных сигналов. Для решения поставленной задачи в устройство, содержащее компаратор 1, цифроаналоговый преобразователь 2, регистр 11 управления, устройство 15 управления, введены дешифратор 3, счетчик 4, постоянные запоминающие устройства 5,6, мультиплексоры 7,8, сумматоры 9,10, регистр 12 сдвига, цепочка 13 инверторов, регистр 14 экспоненты. 1 з.п. ф-лы, 3 ил.

С конец

| Анисимов АоВо и др | |||

| Аналоговые и гибридные вычислительные машины, 1984, Со 75, рисо 2о 15 Балакай ВоГ, и дро Интегральные схемы АЦП и ЦАП, 1978, с 45-27, рис о 1-13, |

Авторы

Даты

1989-11-07—Публикация

1988-03-01—Подача