Изобретение представляет собой функциональной аналого-цифровой преобразователь и предназначено для использования в приборостроении, управляющих и информационно-измерительных системах.

Цель изобретения - расширение области применения,

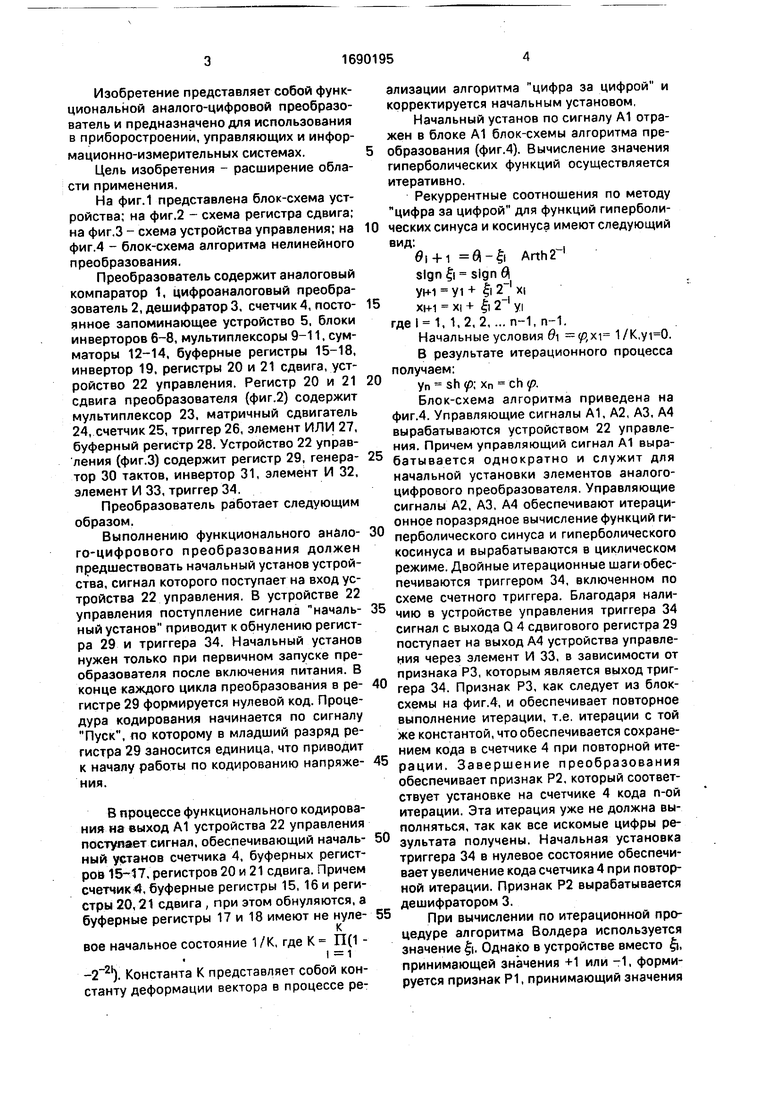

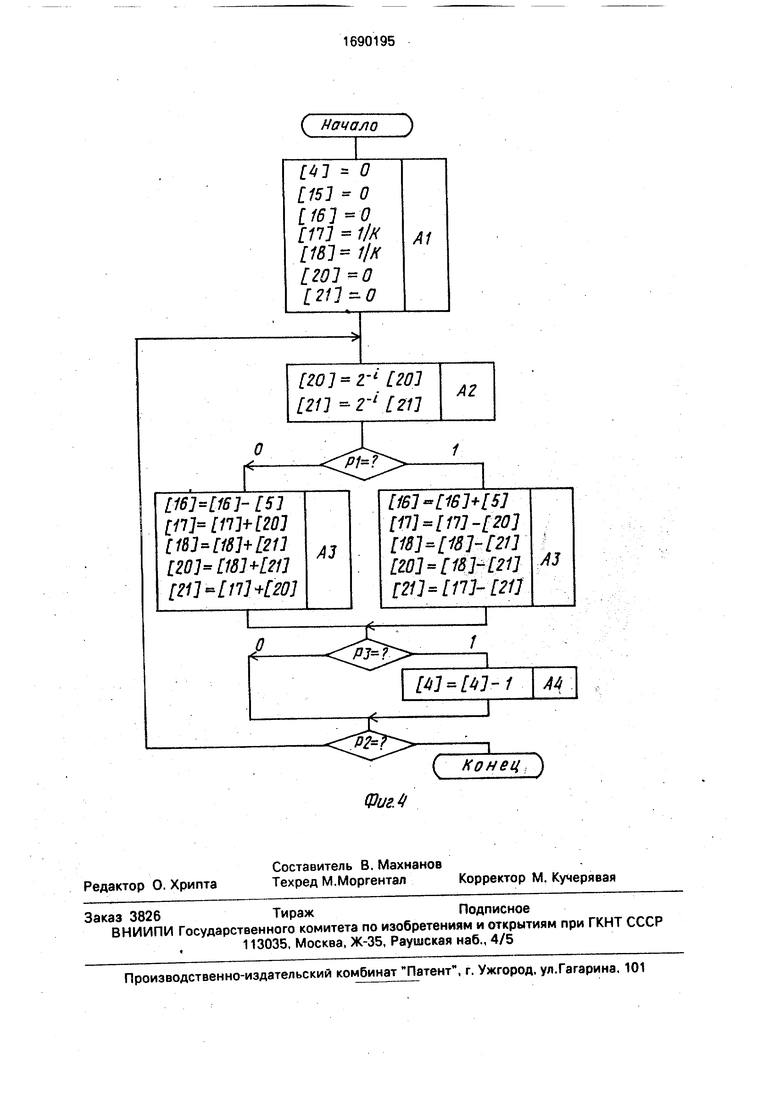

На фиг.1 представлена блок-схема устройства; на фиг.2 - схема регистра сдвига; на фиг.З - схема устройства управления; на фиг.4 - блок-схема алгоритма нелинейного преобразования.

Преобразователь содержит аналоговый компаратор 1, цифроаналоговый преобразователь 2, дешифратор 3, счетчик 4, посто- янное запоминающее устройство 5, блоки инверторов 6-8, мультиплексоры 9-11, сумматоры 12-14, буферные регистры 15-18, инвертор 19, регистры 20 и 21 сдвига, устройство 22 управления. Регистр 20 и 21 сдвига преобразователя (фиг.2) содержит мультиплексор 23, матричный сдвигатель 24, счетчик 25, триггер 26, элемент ИЛИ 27, буферный регистр 28. Устройство 22 управ- ления (фиг.З) содержит регистр 29, генера- тор 30 тактов, инвертор 31, элемент И 32, элемент И 33, триггер 34.

Преобразователь работает следующим образом.

Выполнению функционального знало- го-цифрового преобразования должен предшествовать начальный установ устройства, сигнал которого поступает на вход устройства 22 управления. В устройстве 22 управления поступление сигнала началь- ный установ приводит к обнулению регистра 29 и триггера 34. Начальный установ нужен только при первичном запуске преобразователя после включения питания. В конце каждого цикла преобразования в ре- гистре 29 формируется нулевой код. Процедура кодирования начинается по сигналу Пуск, по которому в младший разряд регистра 29 заносится единица, что приводит к началу работы по кодированию напряже- ния.

В процессе функционального кодирования на выход А1 устройства 22 управления поступает сигнал, обеспечивающий началь- ный установ счетчика 4, буферных регистров 15-17, регистров 20 и 21 сдвига. Причем счетчик4, буферные регистры 15,16 и регистры 20,21 сдвига , при этом обнуляются, а буферные регистры 17 и 18 имеют не нуле-

К

вое начальное состояние 1/К, где К П(1 i 1

). Константа К представляет собой константу деформации вектора в процессе реализации алгоритма цифра за цифрой и корректируется начальным установом,

Начальный установ по сигналу А1 отражен в блоке А1 блок-схемы алгоритма преобразования (фиг.4). Вычисление значения гиперболических функций осуществляется итеративно.

Рекуррентные соотношения по методу цифра за цифрой для функций гиперболических синуса и косинуса имеют следующий вид:

01 + 1 fl-Јi Arth2H

sign Јi sign fl

ун-1 yi + Јi xi

xi+1 xi + |i 2 yi где I 1, 1,2, 2,... n-1, n-1.

Начальные условия Q 1/K,.

В результате итерационного процесса получаем:

yn sh p: xn ch р.

Блок-схема алгоритма приведена на фиг.4. Управляющие сигналы А1, А2, A3, А4 вырабатываются устройством 22 управления. Причем управляющий сигнал А1 вырабатывается однократно и служит для начальной установки элементов аналого- цифрового преобразователя. Управляющие сигналы А2, A3, А4 обеспечивают итерационное поразрядное вычисление функций гиперболического синуса и гиперболического косинуса и вырабатываются в циклическом режиме. Двойные итерационные шаги обеспечиваются триггером 34, включенном по схеме счетного триггера. Благодаря наличию в устройстве управления триггера 34 сигнал с выхода Q 4 сдвигового регистра 29 поступает на выход А4 устройства управления через элемент И 33, в зависимости от признака РЗ, которым является выход триггера 34. Признак РЗ, как следует из блок- схемы на фиг.4, и обеспечивает повторное выполнение итерации, т.е. итерации с той же константой, что обеспечивается сохранением кода в счетчике 4 при повторной итерации. Завершение преобразования обеспечивает признак Р2, который соответствует установке на счетчике 4 кода п-ой итерации. Эта итерация уже не должна выполняться, так как все искомые цифры результата получены. Начальная установка триггера 34 в нулевое состояние обеспечивает увеличение кода счетчика 4 при повторной итерации. Признак Р2 вырабатывается дешифратором 3.

При вычислении по итерационной процедуре алгоритма Волдера используется значение §. Однако в устройстве вместо |i, принимающей значения +1 или -1, формируется признак Р1, принимающий значения

О и 1 и обеспечивающий в преобразователе действия, эквивалентные смене знака у §. Операция вычитания, предусмотренная алгоритмом Волдера, реализуется в устройстве сложением с дополнительным кодом. Для формирования дополнительного кода используются блок инверторов 6-8 и входы переноса в младший разряд в сумматорах 9-11. В обычных режимах использования комбинационных сумматоров эти входы переносов остаются свободными.

После выполнения начального установа начинается циклическая часть алгоритма преобразования, в блоке А2 которого выполняется сдвиг на I разрядов содержимого сдвиговых регистров 20 и 21. Схема сдвиговых регистров 20 и 21 приведена на фиг.2. Величина I формируется в счетчике 25, устанавливаемом в начальное состояние по сигналу А1. Подсчет величины сдвига I выполняется при поступлении импульсов с выхода А2 устройства 22 управления на счетный вход счетчика 25. Этот же сигнал (А2) поступает на триггер 26, который переключает мультиплексор 23 на выход матричного сдвигателя 24. Сигнал А2 обеспечивает также через элемент ИЛИ 27 стробирование записи результата сдвига в регистр-защелку 28, устанавливаемый в начальное состояние по сигналу А1.

После выполнений действий, предусматриваемых по сигналу А2 устройства управления, устройство переходит к выполнению действий, предусматриваемых по сигналу A3 управления. Выход A3 устройства 22 управления соединен с входами записи в буферные регистры 16-18, что обеспечивает запись в эти регистры результата сложения в сумматорах 12-14, причем в этих сумматорах может быть выполнено и вычитание путем сложения с дополнительным кодом отрицательного числа.

В сумматоре 12 выполняется сложение в соответствии с формулой

01+1 0-Јi Arth24, где 01 0.

Значение Arth2 берется из постоянного запоминающего устройства 5 по адресу, формируемому счетчиком 4. Знак Ј| вводится путем выбора между значением гиперболического арктангенса и обратным кодом этого значения, формируемым блоком инверторов 6, осуществляемым мультиплексором 9 под воздействием управляющего сигнала Р1. Значение арктангенса, выбранное мультиплексором 9, фиксируется в буферном регистре 15 стро- бируемым сигналом A3, складывается со значением ft, формируемым в буферном

регистре 16, в сумматоре 12, В случае, если выполняется вычитание, Р1 принимает значение 0, которое инвертируется инвертором 19, и в сумматоре 12 происходит сложение

с дополнительным кодом отрицательного числа путем подачи с мультиплексора 9 обратного кода, а на младший разряд сумматора 12 - корректирующей единицы с выхода инвертора 19.

0 Значение 9, сформированное сумматором 12, поступает на вход цифроаналогово- го преобразователя 2, преобразуется в аналоговую величину и сравнивается со значением компаратором 1. При этом значе5 ние § определяется из соотношения:

i

sign § (p- Ј & Ar th24).

k 1

Это соотношение эквивалентно классиче0 скому рекуррентному соотношению алгоритма Волдера: slgn§ sign 0, 01 + 1 fl-§ Arth2H. где 01 p.

5 В сумматоре 13 выполняется сложение в соответствии с формулой:

хн-1 xi + § 2H f

Сдвиг кода yi на i разрядов осуществлен по сигналу А2 в регистре 20 сдвига. Выход ре0 гистра 20 сдвига соединен с входом мультиплексора 10, на второй вход которого подается выход цепочки инверторов 7. В сочетании с подачей значения Р1 на младший разряд сумматора 13 в сумматоре 13

5 происходит либо сложение, либо вычитание путем сложения с дополнительным кодом числа. Результат сложения-вычитания фиксируется в буферном регистре 17 и в регистре-защелке 28 регистра сдвига 21.

0 Фиксация результата в регистре-защелке 28 обеспечивается тем, что по сигналу А2 триггер 26 регистра 21 сдвига переключает мультиплексор 23 на прием кода с информационного входа В, который соединен с вы5 ходом сумматора 13. Стробируется запись в регистр-защелку 28 синхросигналом, поступающим через элемент ИЛИ 27. Аналогичным образом осуществляется и запись результата, полученного в сумматоре 14, в

0 регистр 20 сдвига.

В сумматоре 14 выполняется сложение в соответствии с формулой

у 1+1 yi + § 2Н xi. Код xi, сдвинутый по сигналу А2 на i разря5 дов в регистре 21 сдвига, поступает на вход мультиплексора 11, на второй вход которого поступает обратное значение этого кода, сформированное цепочкой инверторов 8. В сочетании с подачей значения Р1 на младший п разряд сумматора 14 в сумматоре 14

происходит либо сложение, либо вычитание путем сложения с дополнительным кодом Отрицательного числа. Результат сложения- вычитания фиксируется в буферном регистре 18 и регистре 20 сдвига.

После завершения 1-го цикла преобразования либо повторная итерация с той же Образующей константой, либо значение Счетчика 4 инкрементируется по сигналу А4 устройства 22 управления и происходит итерация со следующей эталонной константой.

Завершается процесс преобразования при вычислении всех разрядов результата. Это фиксирует дешифратор 3, на который поступает код со счетчика 4. Выход дешифратора 3 является признаком Готов устройства, а также поступает на вход устройства 22 управления в качестве признака Р2, который через инвертор 31 и элемент И 32 инициирует новый цикл работы устройства путем занесения единицы на вход Х2 регистра 29 сдвига, что приводит к появлению сигнала А2 на выходе Q 2 регистра 29 сдвига.

Формирование сигналов А1, А2, A3, А4 происходит путем сдвига кода в регистре 21 сдвига ро синхросигналам, вырабатываемым генератором 30 тактов. В младший разряд Х1 регистра 29 запись происходит по сигналу Пуск, поэтому сигнал А1 появляется только один раз в процессе преобразования. В цикле вырабатываются сигналы А2, A3, А4. Завершение процесса кодирования обеспечивается блокировкой записи в разряд Х2.

Формула изобретения Аналого-цифровой преобразователь, содержащий первый и второй буферные регистры, компаратор, первый вход которого соединен с выходом цифроаналогового преобразователя, устройство управления, первый вход которого является шиной пуска, второй вход - шиной начальной установки, третий вход - шиной готовности результата и соединен с выходом дешифратора, счетчик, вход начальной установки которого соединен с первым выходом устройства управления, а счетный вход - с вторым выходом устройства управления, выход счетчика соединен с входом постоянного запоминающего устройства и вхсчом дешифратора, первый регистр сдвига, выход которого соединен с первым входом первого мультиплексора и входом первого блока инверторов, выход которого соединен с вторым входом первого мультиплексора, выход которого соединен с первым информационным входом первого сумматора, выход которого соединен с информационным входом

первого буферного регистра, входы начальной установки первого и второго буферных регистров и первого регистра сдвига соединены с первым выходом устройства управления, третий выход которого соединен с входом управления первого регистра сдвига, четвертый выход соединен с входом синхронизации первого и второго буферных регистров, входом синхронизации первого

0 регистра сдвига, выход компаратора соединен с входами управления первого и второго мультиплексоров и входом переноса в младший разряд первого сумматора, второй сумматор, отличающийся тем, что, с целью

5 расширения области применения за счет увеличения числа формируемых нелинейных функций, в него введены инвертор, второй регистр сдвига, второй и третий блок . инверторов, третий мультиплексор, третий

0 сумматор, третий и четвертый буферные регистры, причем выход инвертора соединен с входом переноса в младший разряд третьего сумматора, выход которого соединен с цифровым входом цифроаналогового пре5 образователя и информационным входом третьего буферного регистра, выход которого соединен с первым информационным входом третьего сумматора, второй информационный вход которого соединен с выхо0 дом четвертого буферного регистра, информационный вход которого соединен с выходом третьего мультиплексора, первый и второй информационные входы которого соединены с выходом постоянного запоми5 нающего устройства непосредственно и через второй блок инверторов соответственно, аналоговый вход цифроаналогового преобразователя является шиной опорного напряжения, второй вход

0 компаратора является входной шиной, выход компаратора соединен с входом инвертора, входом управления третьего мультиплексора и входом переноса в младший разряд второго сумматора, выход кото5 рого соединен с информационным входом первого регистра сдвига, информационным входом второго буферного регистра, информационный входвторогорегистра

0 сдвига соединен с выходом первого сумматора, выход второго регистра сдвига соединен с первым информационным входом второго мультиплексора и входом третьего блока инверторов, выход которого соединен

5 с вторым информационным входом второго мультиплексора, выход которого соединен с первым информационным входом второго сумматора, второй информационный вход которого соединен с выходом второго буферного регистра и является выходной шиной гиперболического синуса, выходной шиной гиперболического косинуса является выход первого буферного регистра, входы начальной установки третьего и четвертого буферных регистров и второго регистра сдвига соединены с первым выходом устройства управления, с третьим выходом которого соединен вход управления второго регистра сдвига, а с четвертым выходом - входы синхронизации третьего и четвертого буферных регистров и входы синхронизации второго регистра сдвига.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1988 |

|

SU1520659A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1612374A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ | 1988 |

|

SU1755650A1 |

| Устройство для вычисления тригонометрических функций | 1980 |

|

SU928348A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU940155A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2006936C1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1686697A1 |

| Преобразователь координат | 1988 |

|

SU1566345A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1035604A1 |

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

Аналого-цифровой преобразователь предназначен для использования в качестве гиперболического преобразователя для ввода аналоговой информации в микро- и миниЭВМ и может найти применение в приборостроении, управляющих и информационно-измерительных системах. В устройстве решается задача расширения области применения аналого-цифровых преобразователей. Для решения поставленной задачи в устройство, содержащее компаратор 1 аналоговых сигналов, первый вход которого соединен с входной шиной устройства в целом, цифроаналоговый преобразователь 2. выход которого соединен с вторым входом компаратора 2 аналоговых сигналов, устройство 22 управления, первый вход которого является шиной пуска, введены дешифратор 3, счетчик 4, постоянное запоминающее устройство 5, блоки инверторов 6-8, мультиплексоры 9-11. сумматоры 12-14, буферные регистры 15- 18, инвертор 19, регистры 20 и 21 сдвига, причем выход счетчика соединен с входами постоянного запоминающего устройства 5 и дешифратора 3, выход которого соединен с входом устройства 22 управления, выход постоянного запоминающего устройства 5 соединен с первым входом мультиплексора 9 и входом блока инверторов 6, выход которого соединен с вторым входом мультиплексора 9У последний соединен с информационным входом буферного регистра 15, выход которого соединен с первым входом сумматора 12, выход которого сое-с динен с цифровым входом цифроаналогово- го преобразователя 2. 4 ил. Ne fe О о о ю ел

Фиг.2

Пуск

Начальный установ

Фкг.З

29

31 Q2 Q3

Q4

41

А2

A3

33

А4

К К

С

J

( НачалоJ

141 О 151 - О 161 0, 111 llK

201 Z 1 201

211 211

L16M161- 51

211

20

О

A1

A2

211 211

1

( конец

| IRE Transectlon on Electronic Сотр., 1959, vol | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Катодная трубка Брауна | 1922 |

|

SU330A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1612374A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-11-07—Публикация

1989-01-18—Подача