Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных системах, микропроцессорных управляющих комплексах и устройствах

Целью изобретения является повышение быстродействия устройства путе сокращения перебора столбцов таблицы неисправностей.

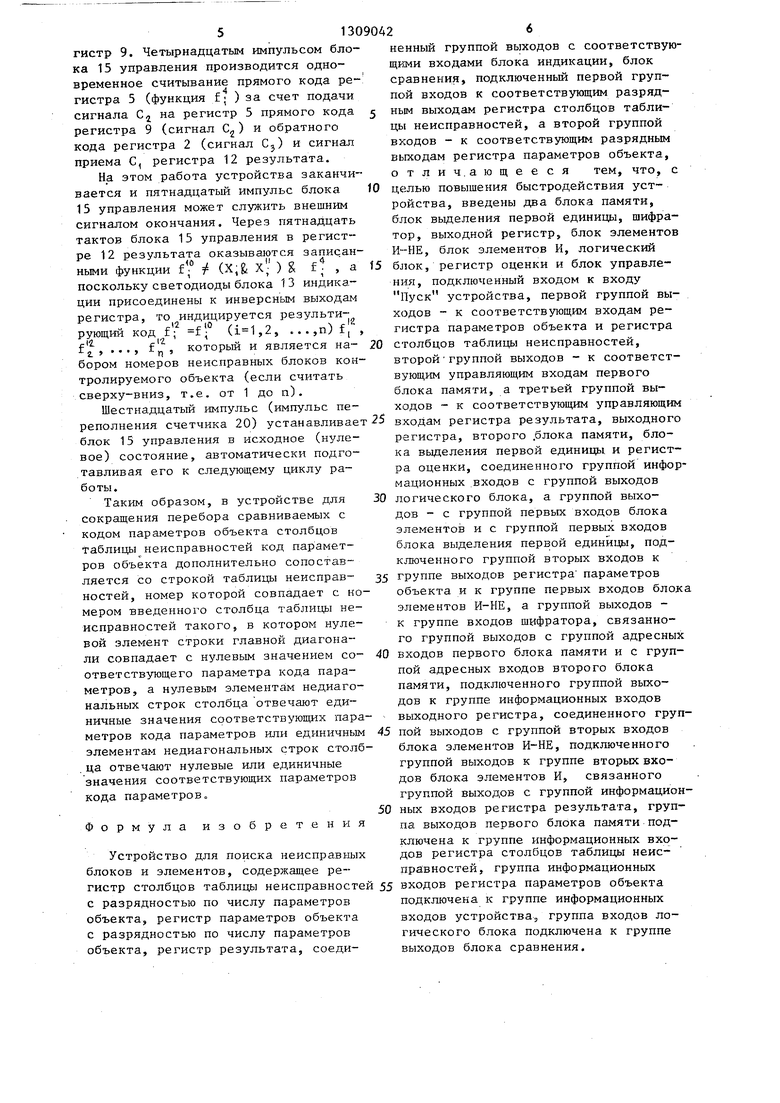

На фиг. 1 представлена структур- ная схема устройства; на фиг. 2 функциональная схема блока управления.

Устройство содержит (фиг. 1) регистр 1 столбцов таблицы неисправное тей, регистр 2 параметров объекта, блок 3 сравнения, логический блок 4, регистр 5 оценки, блок б выделения первой единицы, шифратор 7, второй блок 8 памяти, выходной регистр 9, блок элементов И-НЕ 10, блок элементов И 11, регистр 12 результата, бло 13 индикации, первый блок 14 памяти, блок 15 управления, вход 16 Пуск устройства, группу информационных входов 17 устройства.

Блок 15 управления (фиг. 2) содержит генератор 18 импульсов, элемент И 19, счетчик 20 импульсов, дешифратор 21 и триггер 22.

Все регистры устройства имеют типовую структуру на статических триггерах, что позволяет осуществить при

ем прямого кода при подаче управляю

щего сигнала С,, хранение кода и выдачу прямого (по сигналу С) или обратного (по сигналу Cj) кода, хранящегося в регистре, при этом установка в исходное (нулевое) состояние производится сигналом С,. Шифратор 7 представляет собой типовое устройство, преобразующее унитарный код в двоич- ньй позиционный код. Блок 13 индикации реализуется в виде п светодиодов, каждый из которых соединен с потенциальными инверсными выходами тригге- .ров блока 12. Блоки 8 и 14 представляют собой постоянные запоми- ншощие устройства с электрическим или ультрафиолетовым стиранием информации допускающие запись любых таблиц неисправностей. Причем в блок 8 памяти и в блок 14 памяти записывается одна и таже таблица неисправностей, одна- ко в блок 8 памяти запись производится таким образом, чтобы обеспечивалось считывание ее по строкам, а в блок 14 памяти - по столбцам.,Блок 6

вьщеления первой единицы в двоичном коде реализуется либо в виде регистра сдвига, либо для обеспечения быстродействия в виде известного устройства.

Логический блок 4 представляет собой логическую комбинационную схему, реализующую логическую функцию вида

т.е. на каждом i-м выходе блока 4 образуются конъюнкции между значениями всех остальных выходов блока 3 и инверсией рассматриваемого i-ro выхода блока 3.

Каждая из (||ункций fj реализуется с помощью одного элемента НЕ и одного п-разрядного элемента И, причем п-1 (кроме i-ro) выходов блока 3 соединены соответственно с 1, 2, ..., i-1, i+1, .,.., n входами соответствующего элемента И в i-M разряде блока 4, а i-й выход блока 3 перед соединением с входом элемента И проходит через элемент НЕ.

При описании работы устройства ий- пользованы следующие обозначения:

- код параметров объекта;

,Х,

код столбца таблицы неисправностей; - код строки таблицы неисправностей;

принимают значение 1 или О в зависимости от значения параметра;

- логические функции, реализуемые на выходах разрядов блока 3 сравнения (двоичных кодов параметров объекта и столбцов таблицы неисправностей);

- логические функции, реализуемые на выходах разрядов логического блока 4;

f,f,fj, ... - логические функции реализуемые на инвертирующих выходах разрядов логического блока 4; f fj f, ... - логические функции реализуемые на выходах блока 11. С д - сигнал приема адраса в блок памяти Сд - сигнал установки

исходного (нулевого) состояния со- ответствущего бло- :ка,-

С,, - сигнал записи кода

на регистр,

Cj - сигнал считьтания прямого кода регистра;Cj - сигнал считывания обратного кода регистра;

. - считывание информации из блока памяти.

Устройство работает следующим образом.

По сигналу Пуск (фиг. 1 и 2) начинается работа счетчика 20 блока 15 управления, которьй выдает импульс с нулевого выхода дешифратора 21. При этом все регистры 1, 2, 5, 9, 12 и (блоки 6, 8, 14 устанавливаются в исходное (нулевое) состояние, для это- го нулевой выход дешифратора 21 соединен с нулевыми входами С всех перечисленных устройств.

Вторьм импульсом блока 15 управления (с первого выхода дешифратора 21 осуществляется прием (сигнал С| регистра 2) кода параметра объекта на регистр 2 параметров объекта.

Третий импульс подается для переписи обратного кода с регистра 2 (сигнал Cj регистра 2) на блок 6 выделения первой единицы, а четвертым и пятым импульсом производится выделение первой единицы в обратном коде параметров объекта (т.е. первого ну- ля в коде параметров объекта). Шестым импульсом код первой единицы через шифратор 7 записывается в регистр адреса блока 14 памяти (который входит в состав любого серийного посто- янно запоминающего устройства).

Седьмым импульсом производится считывание информации с блока 14 памяти и запись ее в регистр Г. Для этого восьмой выход дешифратора 21 должен быть соединен с управляющим входом регистра 1 (сигнал С записи кода на регистр 1) и с управляющим входом блока 14 памяти (сигнал Cjp считывание информации из блока памяти по заданному адресу). -Восьмью импульсов обратный код Х и прямой код Х- , т.е. соответственно содержимое регистра 1 и содержимое регистра 2 (сигналы С - считывания офэатного кода и С - сигнал считывания прямого кода) считываются, проходят через блоки 3 и 4 и за счет одновременной начала сигнала С, - записи кода в регистр 5 - осуществляется запись логической функ- в регистр 5.

г

ции f, г

г Л

Тогда f -Х & Х; а результирующая п-разрядная функция f , записанная в регистре 5, имеет вид f

(.Af) J .

Для правильной записи значения образованных функций fj (j 1,2, ..., п) длительность импульса управления, поданого одновременно на соответствующие управляющие входы регистра I (сигнал Cj) и регистр 2 (сигнал Cj) регистра 5 и управляющий вход приема кода (сигнал С), должна быть больше, чем время срабатывания логических элементов И-НЕ и НЕ-И в структурах 3 и 4. Это условие легко выполняется для любого логического базиса, (например, типовой логики К 155) за счет выбора тактовой частоты работы счетчика 20 в блоке 15 управления.

Девятым импульсом производится считьшанием обратного кода регистра 5 (т.е. образуется функция ff ft с одновременной записью в блок 6 выделения первой единицы. Десятый и одиннадцатый импульс необходимы для работы блока 6. Двенадцатый импульс осуществляет запись через шифратор 7 в регистр адреса блока 8 памяти (сигнал ) приема кода адреса блока 8 памяти). Этим же импульсом произво- дйтся начальная установка (сигнал Сд) выходного регистра 9. Тринадцатым импульсом производится считывание содержимоего блока 8 памяти (сигнал Cgp) по адресу, записанному в предьщущем такте блока 15 управления. Для этого одновременно с сигналом Cfr подается сигнал С, на рет

гистр 9. Четырнадцатым импульсом блока 15 управления производится одновременное считывание прямого кода регистра 5 (функция f; ) за счет подачи сигнала Cj на регистр 5 прямого кода регистра 9 (сигнал С) и обратного кода регистра 2 (сигнал С) и сигнал приема С, регистра 12 результата.

На этом работа устройства заканчивается и пятнадцатый импульс блока 15 управления может служить внешним сигналом окончания. Через пятнадцать тактов блока 15 управления в регистцелью повышения быстродействия устройства, введены два блока памяти, блок выделения первой единицы, шифратор, выходной регистр, блок элементов И-ЫЕ, блок элементов И, логический

ре 12 результата оказываются записанными функции f. i (Х;& Х ) & f . , а 15 блок, регистр оценки и блок управления, подключенный входом к входу Пуск устройства, первой группой выходов - к соответствующим входам регистра параметров объекта и регистра

поскольку светодиоды блока 1 3 индикации присоединены к инверсным выходам

регистра, то индицируется результи . ,-(0 / лп с

рующии КОД Г; 1; (,,/, ...,п; ±1

f , .,., f 5 который и является на- 20 столбцов таблицы неисправностей.

бором номеров неисправных блоков контролируемого объекта (если считать сверху-вниз, т.е. от 1 до п).

Шестнадцатый импульс (импульс певтороигруппой выходов - к соответствующим управляющим входам первого блока памяти, а третьей группой выходов - к соответствующим управляющим

реполнения счетчика 20) устанавливает 25 входам регистра результата, выходного блок 15 управления в исходное (нулевое) состояние, автоматически подготавливая его к следующему циклу работы.

Таким образом, в устройстве для сокращения перебора сравниваемых с кодом параметров объекта столбцов Таблицы неисправностей код параметров объекта дополнительно сопоставляется со строкой таблицы неисправрегистра, второго .блока памяти, блока выделения первой единицы и регистра оценки, соединенного группой информационных входов с группой выходов

30 логического блока, а группой выходов - с группой первых входов блока элементов и с группой первых входов блока выделения первой единицы, подключенного группой вторых входов к

35 группе выходов регистра параметров

ностей, номер которой совпадает с номером введенного столбца таблицы неисправностей такого, в котором нулевой элемент строки главной диагонали совпадает с нулевым значением со- 40 входов первого блока памяти и с групответствующего параметра кода параметров, а нулевым элементам недиагональных строк столбца отвечают единичные значения соответствующих параметров кода параметров или единичным 45 пой выходов с группой вторых входов элементам недиагональных строк столб- блока элементов И-НЕ, подключенного

. ца отвечают нулевые или единичные значения соответствующих параметров кода параметров.

Формула изобретения

группой выходов к группе вторых входов блока элементов И, связанного группой выходов с группой информацио 50 ных входов регистра результата, груп па выходов первого блока памяти подключена к группе информационных входов регистра столбцов таблицы неис- пра:вностей, группа информационных

Устройство для поиска неисправных блоков и элементов, содержащее регистр столбцов таблицы неисправностей 55 входов регистра параметров объекта

с разрядностью по числу параметровподключена к группе информационных

объекта, регистр параметров объектавходов устройстваэ группа входов лос разрядностью по числу параметровгического блока подключена к группе

объекта, регистр результата, соеди-выходов блока сравнения.

неиньш группой выходов с соответствующими входами блока индикации, блок сравнения, подключенньш первой группой входов к соответствующим разрядным выходам регистра столбцов таблицы неисправностей, а второй группой входов - к соответствующим разрядным выходам регистра параметров объекта.

отлич.ающееся

тем, что, с

целью повышения быстродействия устройства, введены два блока памяти, блок выделения первой единицы, шифратор, выходной регистр, блок элементов И-ЫЕ, блок элементов И, логический

блок, регистр оценки и блок управления, подключенный входом к входу Пуск устройства, первой группой выходов - к соответствующим входам регистра параметров объекта и регистра

второигруппой выходов - к соответствующим управляющим входам первого блока памяти, а третьей группой выходов - к соответствующим управляющим

входам регистра результата, выходного

регистра, второго .блока памяти, блока выделения первой единицы и регистра оценки, соединенного группой информационных входов с группой выходов

логического блока, а группой выходов - с группой первых входов блока элементов и с группой первых входов блока выделения первой единицы, подключенного группой вторых входов к

группе выходов регистра параметров

объекта и к группе первых входов блока элементов И-НЕ, а группой выходов - к группе входов шифратора, связанного группой выходов с группой адресных

пой адресных входов второго блока памяти, подключенного группой выходов к группе информационных входов выходного регистра, соединенного групгруппой выходов к группе вторых входов блока элементов И, связанного группой выходов с группой информацион- 50 ных входов регистра результата, группа выходов первого блока памяти подключена к группе информационных входов регистра столбцов таблицы неис- пра:вностей, группа информационных

55 входов регистра параметров объекта

16

9иг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство поиска неисправных блоков и элементов | 1989 |

|

SU1709351A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162247C2 |

| Устройство для сопряжения источника и приемника информации | 1986 |

|

SU1401468A1 |

| УСТРОЙСТВО СОРТИРОВКИ ИНФОРМАЦИИ МЕТОДОМ ПРЕОБРАЗОВАНИЯ ДАННЫХ В АДРЕС | 2008 |

|

RU2382396C2 |

| Многоканальное устройство для включения резервных радиостанций | 1990 |

|

SU1748299A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

| Микропрограммное устройство управления с контролем | 1982 |

|

SU1038944A1 |

Изобретение относится к области вычислительной техники и может быть использовано в специализированных системах, микропроцессорных управляющих комплексах и устройствах. Цель изобретения - повышение быстродействия устройства за счет сокращения перебора столбцов таблицы неисправностей. Устройство содержит регистр 1 столбцов таблицы неисправностей, регистр 2 параметров объекта, блок 3 сравнения, логический блок 4, регистр 5 оценки, блок 6 выделения первой единицы, шифратор 7, второй блок 8 памяти, выходной регистр 9, блок элементов И-НЕ 10, блок элементов И 11, регистр 12 результата, блок 13 индикации, первый блок 14 памяти, блок 15 управления, вход Пуск 16 устрой- ства, группу 17 информационных входов устройства. 2 ил. (Л П со о со о н( ьо

| УНИВЕРСАЛЬНОЕ УСТРОЙСТВО ДЛЯ ПОИСКА НЕИСПРАВНЫХ | 0 |

|

SU220636A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА НЕИСПРАВНЫХ БЛОКОВ | 0 |

|

SU345492A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для последовательногоВыдЕлЕНия ЕдиНиц из п-РАзРядНОгОКОдА | 1979 |

|

SU809156A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-05-07—Публикация

1985-12-17—Подача