ЕЫЗ-т

ел 1C to

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях, в частности в устройствах для вычисления спектра Фурье.

Целью изобретения является повышение быстродействия и расширение функциональных возможностей за счет выполнения операции умножения комплекс ных чисел.

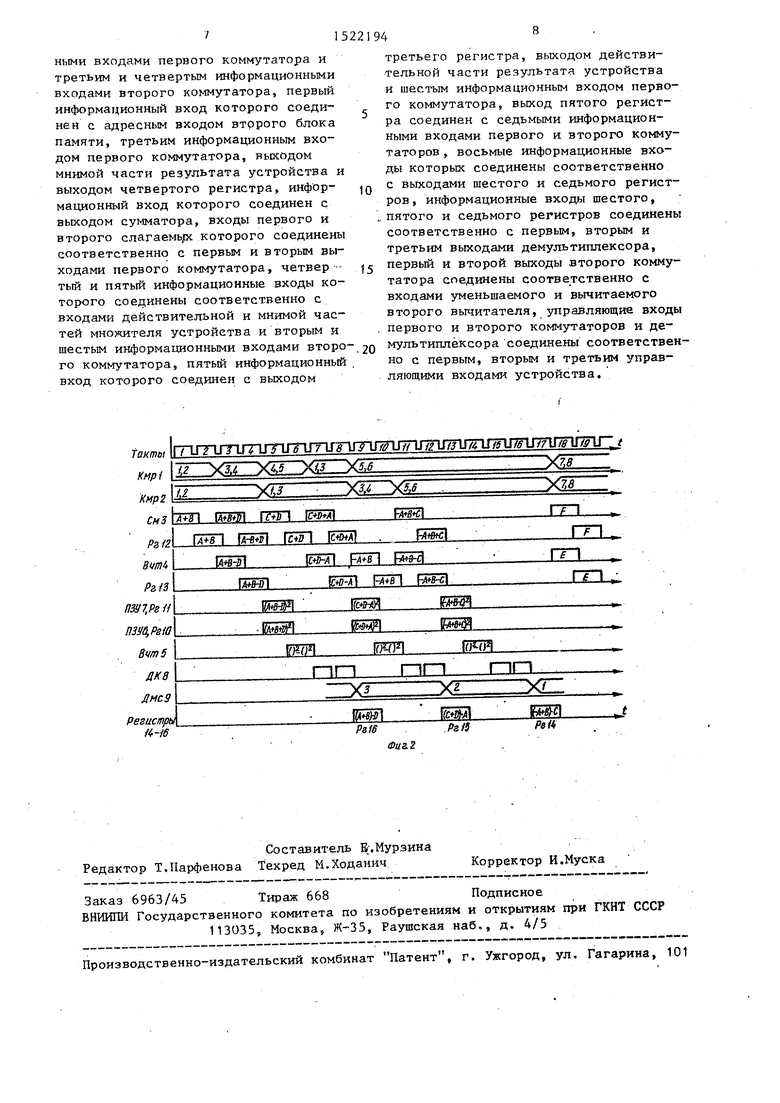

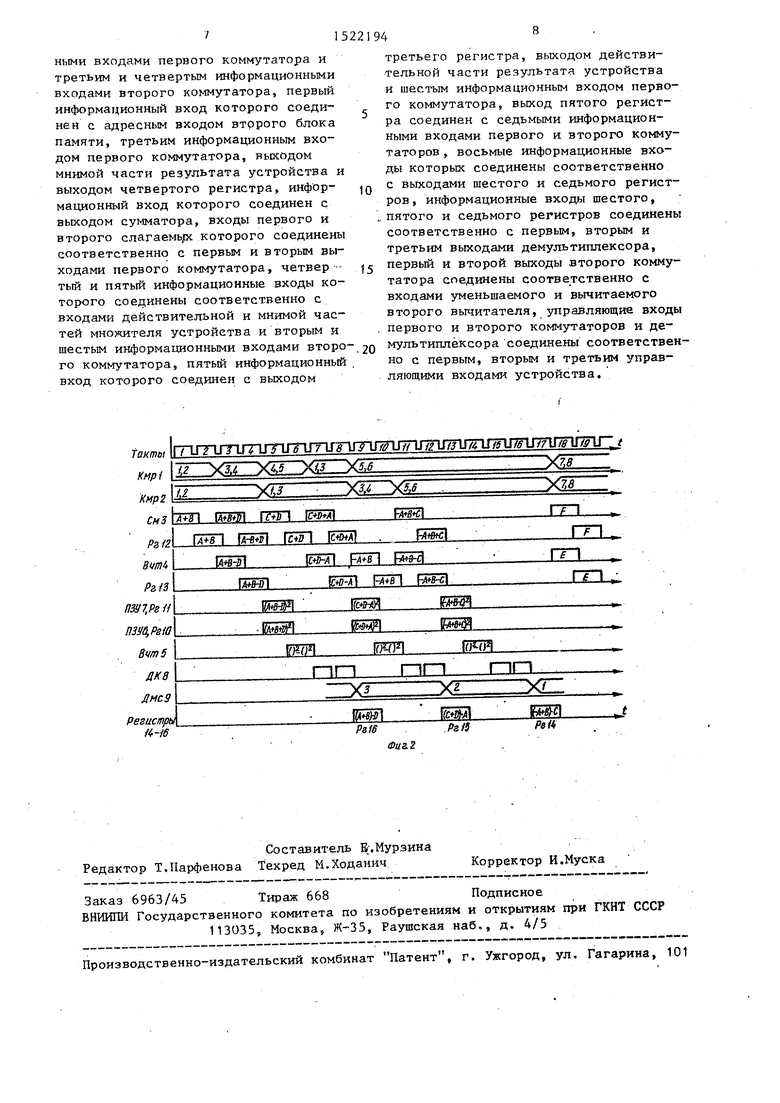

На фиг. представлена функциональная схема предлагаемого устройства для умножения; на фиг. 2 - вр еменная диаграмма работы устройства.

Устройство для умножения содержит коммутаторы 1 и 2, сумматор 3, вычи- татели 4 и 5, блоки 6 и 7 памяти, блок 8 деления на константу, демультт типлексор 9, регистры 10 - 16, вхо- ды действительной 17 и мнимой 18 частей множимого устройства, входы действительной 19 и мнимой 20 частей множителя устройства, управляющие входы 21-23 устройства. Сумматор 3 и вычитатели 4 и 5 имеют внутренние выходные регистры (внутреннюю память), в которых фиксируется результат выполнения операции.

Алгоритм умножения двух комплекс- ных чисел построен на использовании системы билинейных форм

E+jF {A+jB)(c+jD) (G+D)A-(A+B)D

d+ j(C+D)A+(-A+B)(1)

где Ей - действительная и мнимая

части результата умножег-. Q

ния; А и В - действительная и мнимая

части множимоt o.; С и D - действительная и мнимая

части множителя. 45 Промежуточные значения произведений в приведенном выражении определяются по следующим формулам

(.А+В ) D + (A+B+D) - (A+B-D f J ( 2) g

(C+D) A -)-C(C+D+A)-() (3)

(A+B).C .l-(-A+B+C)-(-A+

+B;-.c).

(4)

Таким образом, вычисление произведения двух комплексных чисел сос

Ю

15

20 25

JQ

Q

45

g

55

тоит из четырех этапов: вычисления промежуточных значений произведения по формулам (2) - (4) и определения окончательного результата по формуле (1 ).

Устройство работает следующим образом,. - J

Работу устройства рассмотрим в соответствии с временной диаграммо, на которой показаны моменты срабатывания элементов устройства по отношению к тактовой последовательности. Входы синхронизации на схеме не показаны.

В исходном состоянии все регистры устройства обнулены.В соответствии с формулами (}) - (4) перемножаемые комплексные числа подаются на входы множимог.о 7 и 18 и множителя 1 9 и 20 устройства.Сигналами управления, поступающими на входы 21 и 22 устройства, коммутаторы 1 и 2 устанавливаются в режим передачи данных с первог о и - второго информационных входов на входы сумматора 3 и вычитателя 4.

Рассмотрим работу устройства на первом этапе вычисления промежуточного результата (А+В) D в соответствии с формулой (2).В.первом такте сумматор 3 вычисляет значение суммы (А+В), которое запоминается в его выходном внутреннем регистре и во втором такте переписывается в регистр 12. В третьем такте коммутатор 1 сигналом управления, поступающим на вход 21 устройства, устанавливается в режим передачи данных с третьего и четвертого информациогйых входов. При этом сумматор 3 и вычитатель 4 вычися ляют соответственно значения суммы (A+B-fD) и разности (А+В-О), кото йле запоминаются в их выходных внутренних регистрах. В нетв ёртом такте вычисленные значения суммы и разности переписываются соответственно в регистр 12 и 13 и поступают на адресные входы блоков 6 и 7 памяти,Г и пятом такте с.выхода блока 6 памяти считывается значение () , которое запоминается в регистре 10, ас выхода блока памяти 7 - значение (A+B-D)-, которое запоминается в регистре 11, Полученные значения поступают на входы соответственно уменьшаемого и вычитаемого вычитателя 5, который в шестом такте вычисляет значение разности (A+BfD) - - (A+B-D) , запоминаемое в его внут515Z21

рением выходном регистре, В седьмом и восьмом тактах блок 8 деления на константу осуществляет деление полученного значения на четыре (выполняется путем сдвига) таким образом вы числяется значение произведения (A+B)D в соответствии с формулой (2)- В девятом такте демультиплексор 9 с сигналом управления, поступающим на д Вход 23 устройства, устанавливается в режим передачи данных на третий вход. Вычисленное ранее значение (А+В)В запоминается в регистре 16. На этом заканчивается первый этап вычислений J5 по формированию первого промежуточного результата в соответствии с формулой (2). Аналогично вычисляются значения произведений (C+D)A и (-А+В)С по формулам (З) и (4) на, втором и20

третьем этапах в соответствии с временной диаграммой. Необходимо только учитьшать, что второй этап начинается на пятом такте и заканчивается на -тринадцатом. При этом коммутатор 1 25 сигналом управления, постзтающим на вход 21 устройства, устанавливается в режим передачи данных cJ четвертого и питого информационных входов при вычислении значения (C+D) в пятом так-зо те и в режим передачи данных с первого и третьего информационных входов - при вычислении значения () в седьмом такте. Коммутатор 2 в пятом такте устанавливается в режим передачи ; -, данных с первого и третьего информационных входов на входы соответ- ; ственно уменьшаемого и вычитаемого V вычитателя 4, что обеспечивает вычисление значения (C+D-A) в седьмом дО такте. В тринадцатом такте демультиплексор 9 устанавливается в режим передачи данных на второй выход, и вычисленное значение (C+D)A запоминается в регистре 15. Третий этапдз вычислений начинается в девятом такте и заканчивается в семнадцатом такте. При этом коммутатор 2 устанавливается в режим передачи данных с. третьего и четвертого информационных 50 входов на входы соответственно вычитаемого и уменьшаемого вычитателя 4, обеспечивая вычисление значения (-А+В) в девятом такте. В. одиннадцатом такте коммутатор 2 устанавливает- 55 ся в режим передачи данных с пятого и шестого информа1Ц10ннь1Х входов на входы соответственно уменьшаемого и . вычитаемого вычитателя 4, обеспечивая

946

вьиисление значения (-А+В-С). Коммутатор 1 устанавливается в режим передачи данных с пятого и шестого информационных входов, обеспечивая при этом вычисление значения (-А+В+С) сумматором 3 в одиннадцатом такте. На семнадцатом такте демультиплексор 9 устанавливается в режим передачи данных на первый выход, и вычисленное значение (-А+В)С запоминается в регистре 14. На четвертом этапе оба коммутатора устанавливаются в режим передачи данных с седьмого и восьмого информационных входов. При этом сумматор 3 вычисляет значение мнимой части результата F(C+D)A+(-A+B)C, а вычитатель 4 вычисляет значение дей- ствительной части результата Е (C+D)A-(A+B)D S соответствии с формулой (l). Вычисленные значения в восемнадцатом такте запоминаются в выходных внутренних регистрах сумматора 3 и вычитателя 4, а в девятнадцатом такте переписьшаются в регистры 12 и 13. На этом заканчивается четвертый, этап и полный цикл вычисления произведения двух комплексных чисел.

Формула изобретения

Устройство для умножения, содержащее первьй коммутатор, два вычитателя, сумматор, первый, второй и тре тий регистры, два блока памяти и блок деления на константу, вход которого соединен с выходом первого вычитателя, входы уменьшаемого и вычитаемого которого соединены соответственно, с выходами первого и второго регист ров, информационные входы которых соединены соответственно с выходами первого и второго блоков памяти, адресный вход nepBOi o блока памяти соединен с выходом третьего регист- pa, информационный вход которого соединен с выходом второго вычитателя, о тлич ающее с я. тем, что, с целью повьш1ения быстродейст- ВИЯ и расширения функциональных возможностей за счет выполнения операг ции умножения комплексных чисел, в него введены второй :коммутатор,, четвертый, пятый, шестой и седьмой регистры и демуяьтшшексор, информационный вход которого соединен с выходом блока деления на константу, входы действительной и мнимой частей множимого устройства соединены соответстг-- венно с первым и вторым информационными входами первого коммутатора и третьим и четвертым информационными входами второго коммутатора, первый информационный вход которого соединен с адресным входом второго блока памяти, третьим информационным входом первого коммутатора, выходом мнимой части результата устройства и выходом четвертого регистра, инфор- мационный вход которого соединен с выходом сумматора, входы первого и второго слагаемьрс которого соединены соответственно с первым и вторым выходами первого коммутатора, четвер - тый и пятый информационные входы которого соединены соответственно с входами действительной и мнимой частей множителя устройства и вторым и шестым информационными входами второ го коммутатора, пятый информационньй вход которого соединен с выходом

третьего регистра, выходом действительной части результата устройства и шестым информационным входом первого коммутатора, выход пятого регистра соединен с седьмыми информационными входами первого и: второго коммутаторов , восьмые информационные входы которых соединены соответственно с выходами шестого и седьмого регистров, информационные входы шестого, пятого и седьмого регистров соединены соответственно с первым, вторым и третьим выходами демультиплексора, первый и второй выходы второго коммутатора соединены соответственно с входами уменьшаемого и вычитаемого второго вьтитателя, управляющие входы первого и второго коммутаторов и демультиплексора соединены соответственно с первым, вторым и третьим управяющими входами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОЦЕССОР С МАКСИМАЛЬНО ВОЗМОЖНОЙ ПРОИЗВОДИТЕЛЬНОСТЬЮ ДЛЯ БЫСТРОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 2005 |

|

RU2290687C1 |

| Процессор цифровой обработки сигналов | 1990 |

|

SU1789991A1 |

| Устройство для деления | 1990 |

|

SU1711149A1 |

| Устройство для поворота вектора | 1983 |

|

SU1132285A1 |

| Устройство для быстрого преобразования Фурье | 1988 |

|

SU1524066A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1986 |

|

SU1325508A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| Арифметическое устройство для быстрого преобразования Фурье | 1982 |

|

SU1101835A1 |

| Устройство для быстрого преобразования Фурье | 1984 |

|

SU1206802A1 |

| Устройство для операций над матрицами | 1985 |

|

SU1292008A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях, в частности в устройствах для вычисления спектра Фурье. Цель изобретения - повышение быстродействия и расширение функциональных возможностей за счет выполнения операции умножения комплексных чисел. Устройство для умножения содержит коммутаторы 1,2, сумматор 3, вычитатели 4,5, блоки памяти 6,7, блок 8 деления на константу, демультиплексор 9, регистры 10-16. Алгоритм работы построен на использовании системы билинейных форм E+JF=(A+JB)(C+JD)=[(C+D).A-(A+B).D]+J[(C+D)A+(-A+B)C]

(A+B)D=1/4[(A+B+D)2-(A+B-D)2]

(C+D)A=1/4[(C+D+A)2-(C+D-A)2]

(-A+B)C=1/4[(-A+B+C)2-(-A+B-C)2] и состоит из четырех этапов. 2 ил.

| Хетагуров Я.А | |||

| и др | |||

| Основы инженерного проектирования управляющих ЦВМ | |||

| М.: Советское радио, 1972, с,123-134 | |||

| Скоропечатный станок для печатания со стеклянных пластинок | 1922 |

|

SU35A1 |

| Печь для сжигания твердых и жидких нечистот | 1920 |

|

SU17A1 |

Авторы

Даты

1989-11-15—Публикация

1987-06-11—Подача