W с

:л

fc

ND

фигЛ

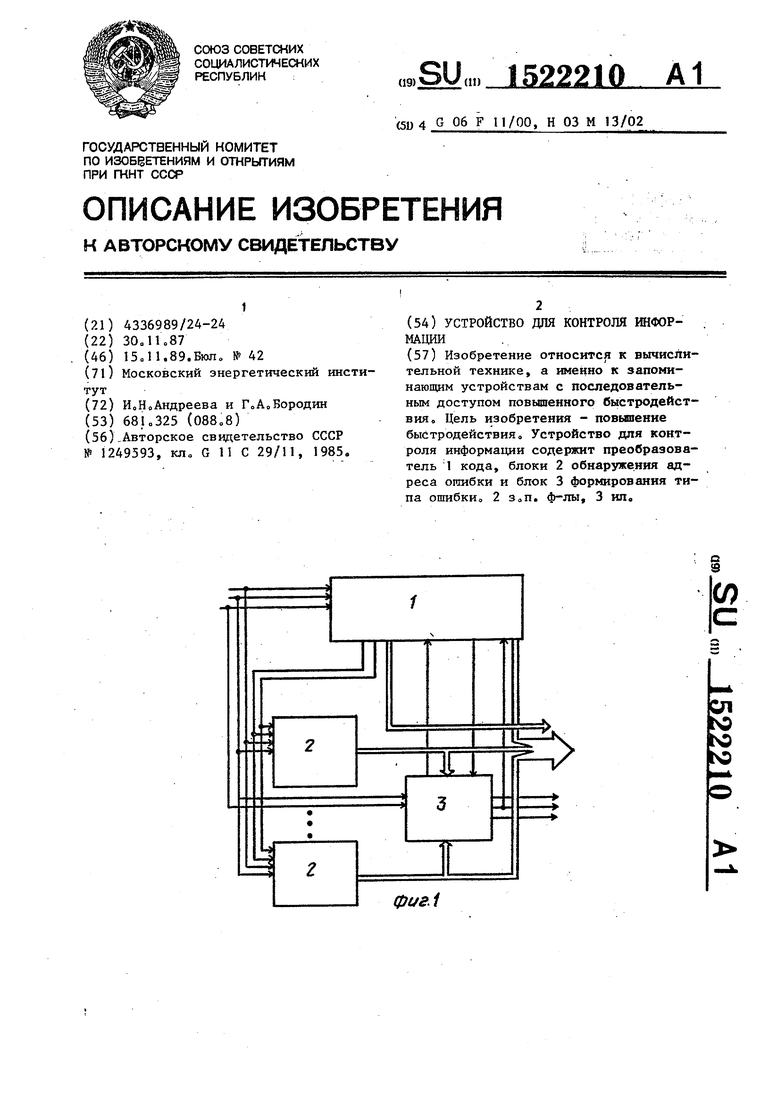

Изобретение относится к вычислительной техникеэ а именно к устройст- i вам для контроля.информации5поступаю- .щей в виде блоков в последовательной форме, например, по каналам связи или с внешних запоминающих устройств, и может быть использовано в запоми- нающих устройствах с последователь- ным доступом для повышения быстро- действия.

Цель изобретекия - повьшение быстродействия устройства„

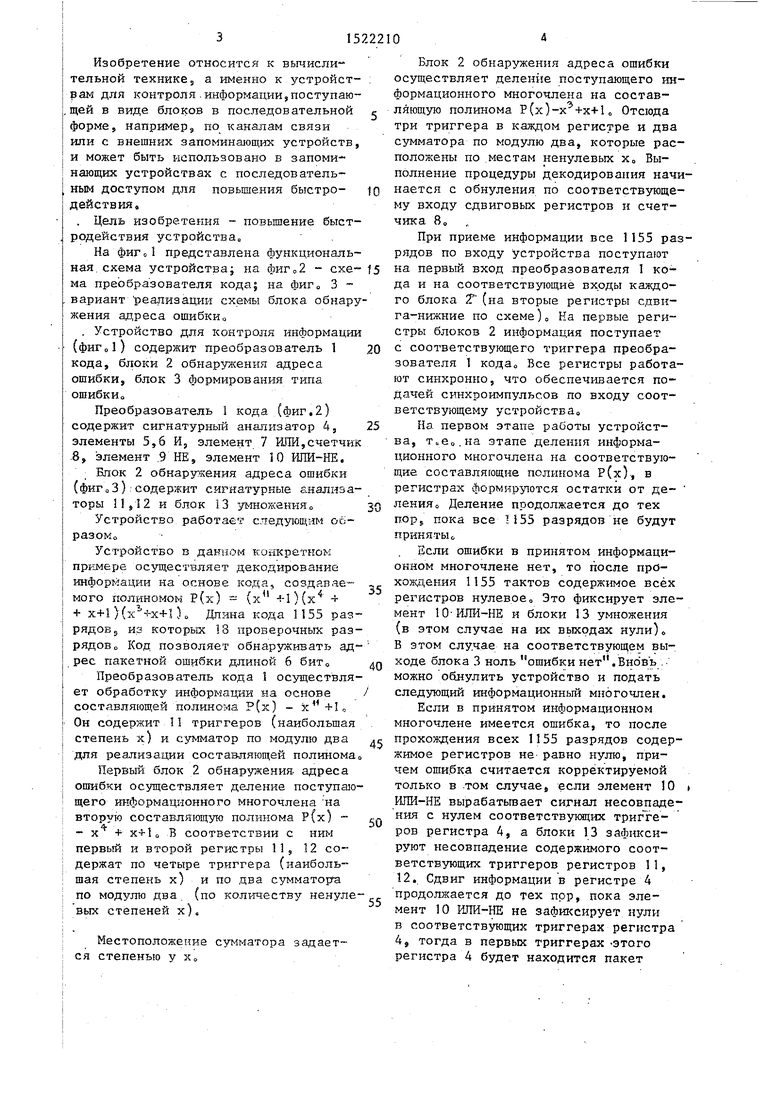

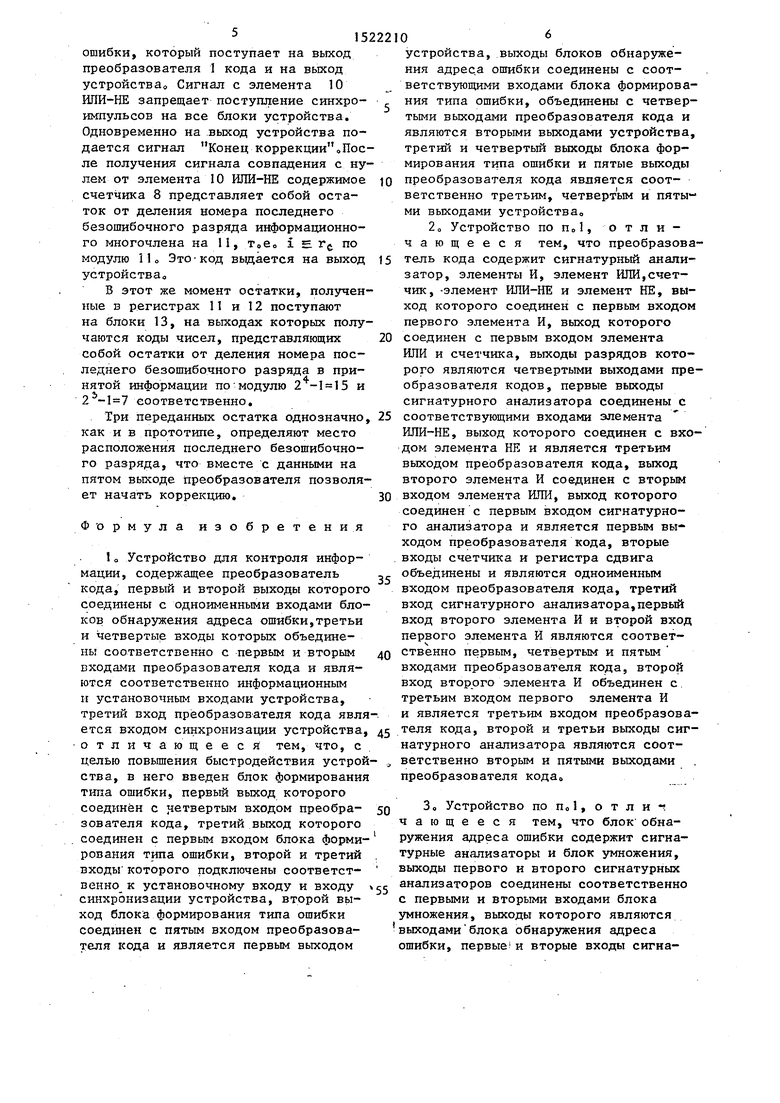

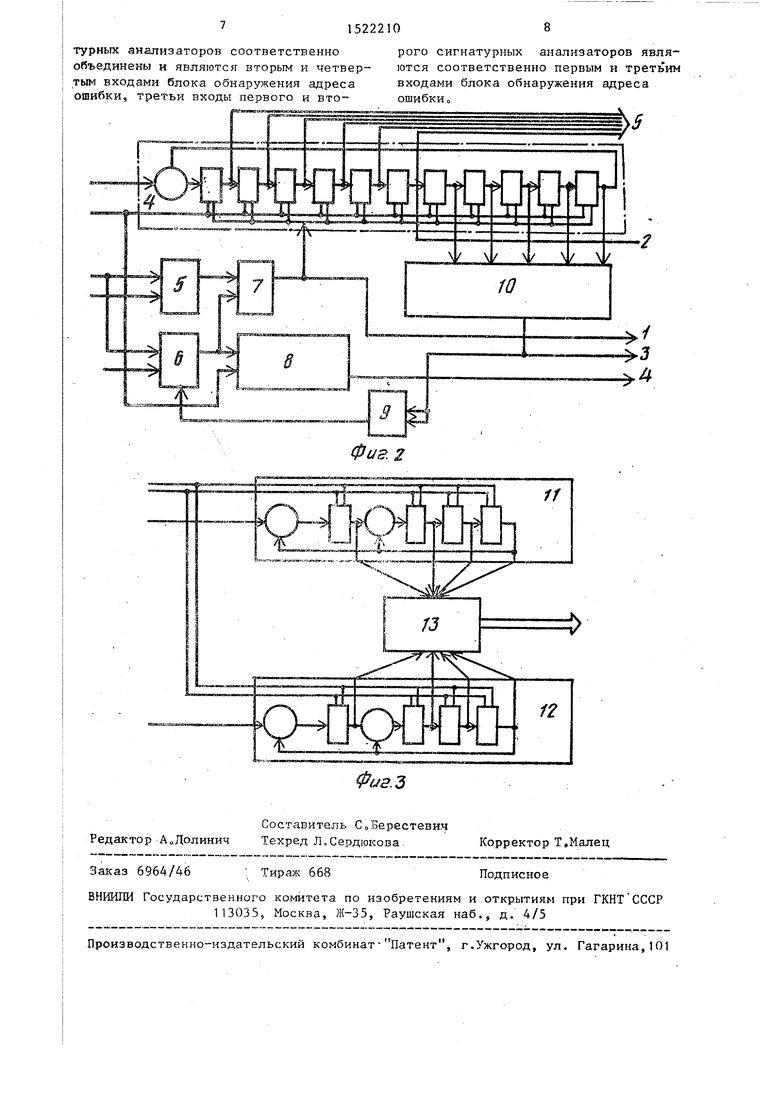

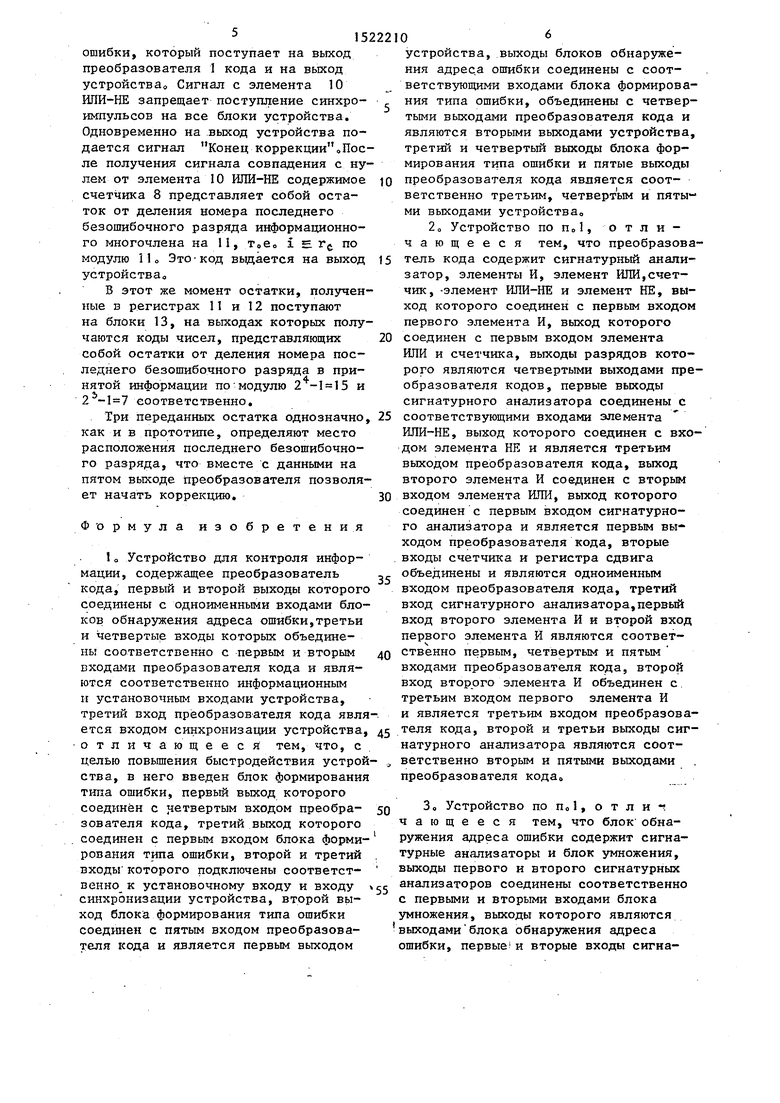

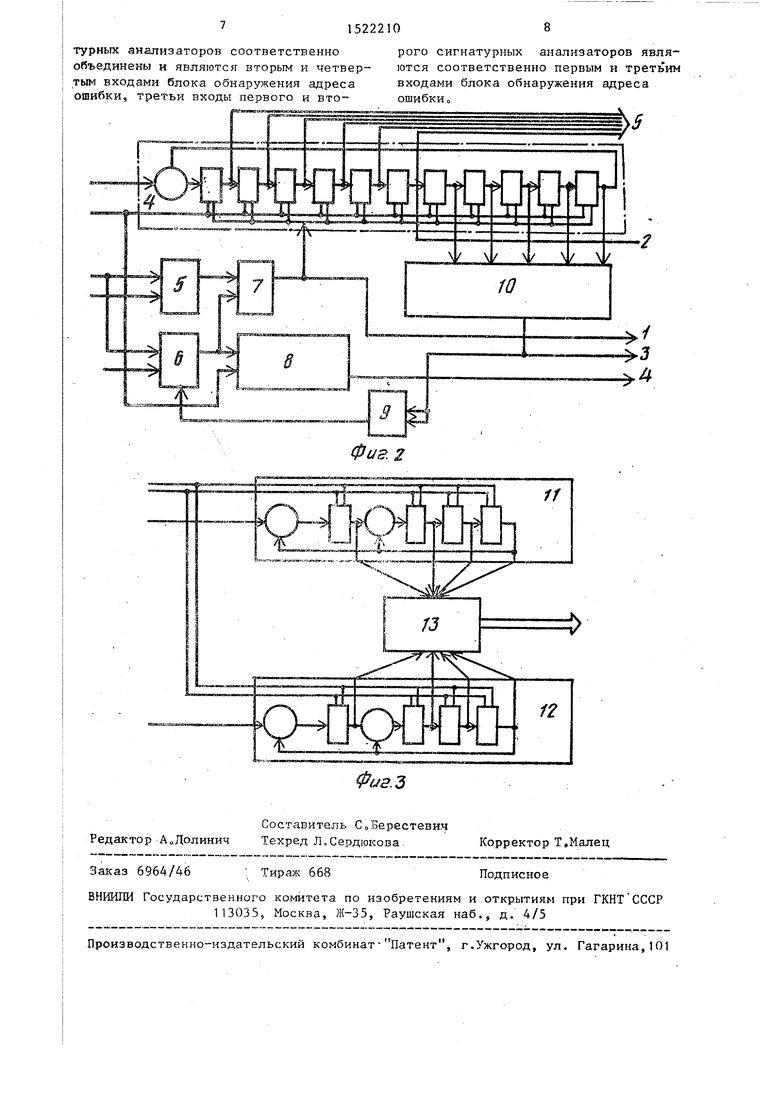

На фиг о 1 представлена функциональная, схема устройства; на фиг о 2 - схе- ма преобразователя кода; на фиг 3 вариант реализации схемы блока обнаружения адреса ошибкио

. Устройство для контроля информации (фиг„1) содержит преобразователь 1 кода, блоки 2 обнаружения адреса ошибки, блок 3 формирования типа

ОШИбКИо

Преобразователь 1 кода (фиг,2) содержит сигнатурный анализатор 4, элементы 5,6 И, элемент 7 ИЛИ,счетчик .8, элемент .9 НЕ, элемент 10 ИЛИ-НЕ.

Блок 2 обнарзтения адреса ошибки (фигоЗ) .-содержит сигнатурные анализаторы 12 и блок 13 уьшожениЯо

Устройство работает следующим оо- разомо

Устройство в данном коикрстнок примере осуществляет декодирование I информации на основе кода, создавае} МОГО полиномом Р(х) - ( -i-OCx -т

I + X+S )(х -5-х-И )р Длина кода 1155 раз рядов5 из которых 18 проверочных: раз I рядов о Код позволяет обнаруживать ад рее пакетной ошибки длиной 6 бито

Преобразователь кода 1 осуществляет обработку информации на основе составляющей полинома Р(х) - х - Он содержит 11 триггеров (наибольшая степень х) и сумматор по модулю два для реализации составляющей полинома

Первый блок 2 обнаружения, адреса ошибки осуществляет деление поступающего информационного многочлена на вторую составляющую полинома Р(х) - - + о В соответствии с ним первый и второй регистры 11, 12 со- j держат по четыре триггера (наиболь-- ; шая степень х) и по два сумматора по модулю два. (по количеству ненуле : вых степеней х).

Местоположение сумматора задает- ; ся степенью у х„

5

0

5

О

0

. дс

gg

5

55

Блок 2 обнаружения адреса ошибки осуществляет деление поступающего информационного многочлена на составляющую полинома Р(х)-х +х+1о Отсюда три триггера в каждом регистре и два сумматора по модулю два, которые расположены по местам ненулевых х Выполнение процедуры декодирования начинается с обнуления по соответствующему входу сдвиговых регистров и счетчика 8„

При приеме информации все 1155 разрядов по входу устройства поступают на первый вход преобразователя 1 кода и на соответствующие входы каждого блока 2 (на вторые регистры сдви- га-нижние по схеме)о На первые регистры блоков 2 информация поступает с соответствующего триггера преобразователя 1 кодао Все регистры работают синхронно, что обеспечивается подачей синхроимпульсов по входу соответствующему устройства

На. первом этапе работы устройства, т,во.на этапе деления информационного многочлена на соответствующие составляющие полинома Р(х)., в регистрах сЬорм ф потся остатки от де- ленияо Деление продолжается до тех пор, пока все П55 разрядов не будут принятые

Если ошибки в принятом информационном многочлене нет, то после прохождения 1155 тактов содержимое всех регистров нулевое Это фиксирует элемент 10-ИЛИ-НЕ и блоки 13 умножения (в этом случае на их выходах нули) В этом случае на соответствующем выходе блока 3 ноль ошибки нет.Вно вь . можно обнулить устройство и подать следующий информационный многочлен.

Если в принятом информационном многочлене имеется ошибка, то после прохождения всех 1155 разрядов содержимое регистров не равно , причем ошибка считается корректируемой только в .том случае, если элемент 10 ШШ-НЕ вырабатьгеает сигнал несовпадения с нулем соответствукщих ров регистра 4, а блоки 13 зафиксируют несовпадение содержимого соответствующих триггеров регистров 11, 12. Сдвиг информации в регистре 4 продолжается до тех пор, пока элемент 10 ИПИ-НЕ не зафиксирует нули в соответствующих триггерах регистра 4j тогда в первых триггерах -этого регистра 4 будет находится пакет

ошибки, который поступает на выход преобразователя I кода и на выход устройства. Сигнал с элемента 10 ИЛИ-НЕ запрещает поступление синхроимпульсов на все блоки устройства. Одновременно на выход устройства подается сигнал Конец коррекции „После получения сигнала совпадения с нулем от элемента 10 ИЛИ-НЕ содержимое счетчика 8 представляет собой остаток от деления номера последнего безошибочного разряда информационного многочлена на II, Тое i г по модулю По Это-код вьщается на выход устройствас

В этот же момент остатки, полученные в регистрах 11 и 12 поступают на блоки 13, на выходах которых получаются коды чисел, представляющих собой остатки от деления номера последнего безошибочного разряда в принятой информации по-МОдулю 2 и соответственно.

Три переданных остатка однозначно, как и в прототипе, определяют место расположения последнего безошибочного разряда, что вместе с данными на пятом выходе преобразователя позволяет начать коррекцию,

Формула изобретения

1 о Устройство для контроля информации, содержащее преобразователь кода, первый и второй выходы которого соединены с одноименными входами блоков обнаружения адреса ошибки,третьи и четвертые входы которых объединены соответственно с первым и вторым входами преобразователя кода и являются соответственно информационным и установочным входами устройства, третий вход преобразователя кода явля

5

0

5 0

5

0

устройства, выходы блоков обиа-руже- ния адрес.а ошибки соединены с соответствующими входами блока формирования типа ошибки, oбъeдra eны с четвертыми выходами преобразователя кода и являются вторыми выходами устройства, третий и четвертый выходы блока формирования типа ошибки и пятые выходы преобразователя кода является соответственно третьим, четверт ым и пятыми выходами устройства

2 о Устройство попо1, отличающееся тем, что преобразователь кода содержит сигнатурный анализатор, элементы И, элемент ИЛИ,счетчик, -элемент ИЛИ-НЕ и элемент НЕ, выход которого соединен с первым входом первого элемента И, выход которого соединен с первым входом элемента ИЛИ и счетчика, выходы разрядов которого являются четвертыми выходами преобразователя кодов, первые выходы сигнатурного анализатора соединены с соответствующими входами элемента ИЛИ-НЕ, выход которого соединен с входом элемента НЕ и является третьим выходом преобразователя кода, выход второго элемента И соединен с вторым входом элемента ИЛИ, выход которого соединен с первым входом сигнатурного анализатора и является первым выходом преобразователя кода, вторые входы счетчика и регистра сдвига объединены и являются одноименным входом преобразователя кода, третий вход сигнатурного анализатора,первый вход второго элемента И и второй вход первого элемента И являются соответственно первым, четвертым и пятым входами преобразователя кода, второй вход второго элемента И объединен с. третьим входом первого элемента И и является третьим входом преобразова

| название | год | авторы | номер документа |

|---|---|---|---|

| Декодирующее устройство | 1989 |

|

SU1644223A1 |

| Устройство для обнаружения ошибок в блоках памяти | 1987 |

|

SU1594611A1 |

| Устройство для обнаружения ошибок в блоках памяти | 1985 |

|

SU1249593A1 |

| Устройство для коррекции ошибок в блоках памяти | 1985 |

|

SU1257708A1 |

| Многоканальный сигнатурный анализатор | 1990 |

|

SU1718220A1 |

| Сигнатурный анализатор | 1986 |

|

SU1357961A1 |

| Многоканальный сигнатурный анализатор | 1989 |

|

SU1647571A1 |

| Сигнатурный анализатор | 1987 |

|

SU1499349A1 |

| Устройство для обнаружения пакетных ошибок | 1987 |

|

SU1541607A1 |

| Сигнатурный анализатор (его варианты) | 1984 |

|

SU1252784A1 |

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам с последовательным доступом повышенного быстродействия. Цель изобретения - повышение быстродействия. Устройство для контроля информации содержит преобразователь 1 кода, блоки 2 обнаружения адреса ошибки и блок 3 формирования типа ошибки. 2 з.п.ф-лы, 3 ил.

ется входом синхронизации устройства, 45 теля кода, второй и третьи выходы сиготл и чающееся тем, что, с целью повьшгения быстродействия устройства, в него введен блок формирования типа ошибки, первый выход которого соединён с 1етвертым входом преобразователя кода, третий выход которого соединен с первым входом блока формирования типа ошибки, второй и третий ВХОДЫ которого подключены соответст- венно к установочному входу и входу синхронизации устройства, второй выход блока формирования типа ошибки соединен с пятым входом преобразователя кода и является первым выходом

0

5

натурного анализатора являются соответственно вторым и пятыми выходами преобразователя кода

Зо Устройство по По 1, о т л и г чающееся тем, что блок обнаружения адреса ошибки содержит сигнатурные анализаторы и блок умножения, выходы первого и второго сигнатурных анализаторов соединены соответственно с первыми и вторыми входами блока умножения, выходы которого являются выходами блока обнаружения адреса ошибки, первые и вторые входы сигнатурных анализаторов соответственно объединены и являются вторым и четвертым входами блока обнаружения адреса ошибки, третьи входы первого и втоРедактор АоДолинич

Составитель С„Берестевин Техред Л.Сердюкова.

Заказ 6964/46

Тираж 668

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, )К-35, Раушская наб., д, 4/5

рого сигнатурных анализаторов являются соответственно первым и третьим входами блока обнаружения адреса ошибки о

Фиг 2

Фиг.Ъ

Корректор Т. Мале ц

Подписное

| Устройство для обнаружения ошибок в блоках памяти | 1985 |

|

SU1249593A1 |

Авторы

Даты

1989-11-15—Публикация

1987-11-30—Подача