Изобретение относится к вычислительной технике и может использоваться в системах тестового диагностирования.

Цель изобретения -уменьшение времени локализации неисправностей в проверяемых каналах.

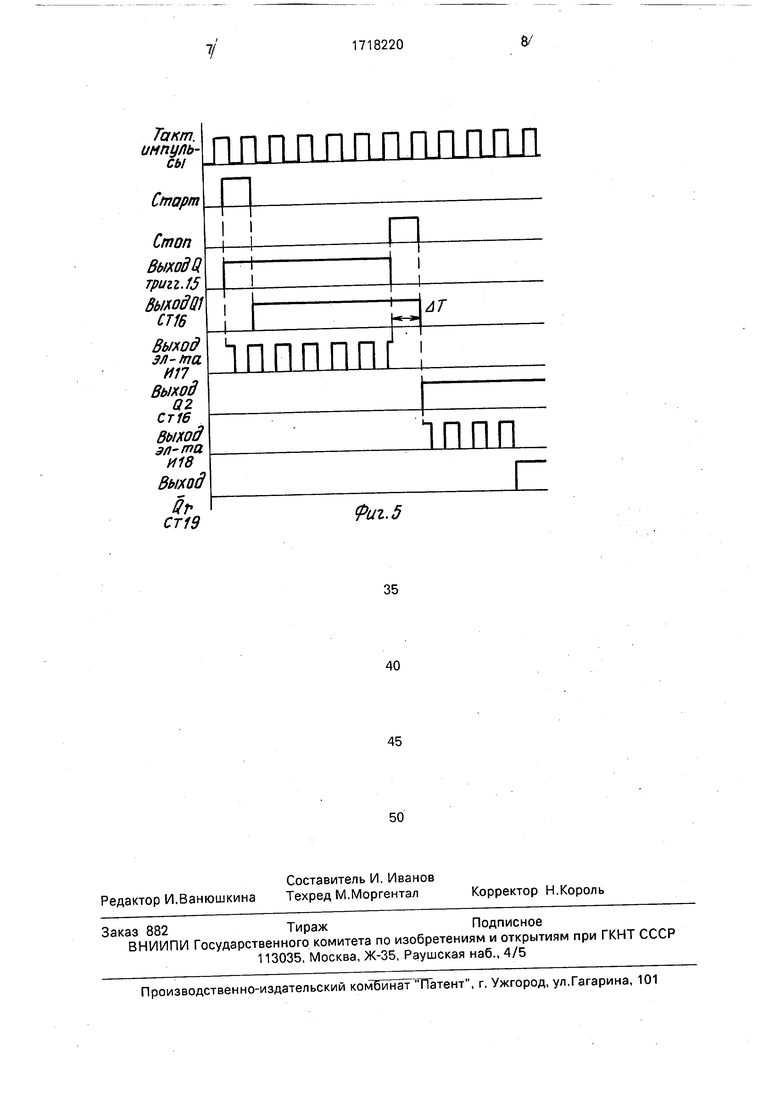

На фиг. 1 показана схема многоканального сигнатурного анализатора; на фиг. 2 - то же, перемножителя, на фиг. 3 - то же, делителя; на фиг. 4 - то же, блока управления; на фиг. 5 - временная диаграмма работы блока управления.

Многоканальный сигнатурный анализатор (фиг. 1) содержит п перемножителей 1, сумматор 2 по модулю два, формирователь 3 сигнатур, блок 4 сравнения, регистр 5 сдвига, п делителей 6, п детекторов 7 нуля и блок 8 управления. Перемножитель 1 (фиг. 2) триггеры 9.1-9,4 и сумматор ТО по модулю два, Делитель 6 (фиг. 3) содержит триггеры 11.1... 11.4 и сумматоры 12.1,12.2 по модулю два. Блок 8 управления (фиг. 4) содержит счетчик 13, элемент И 14, триггер 15, счетчик 16 и элемент И 17.

Многоканальный сигнатурный анализатор работает следующим образом.

По входам начальной установки устанавливаются в исходное состояние (в ноль) п перемножителей 1, формирователь 3, п делителей 6, блок 8 управления. Вход синхронизации многоканального сигнатурного анализатора соединяют с цепью синхронизации объекта контроля (ОК), на вход пуска/останова блока 8 попадают из ОК сигналы, позволяющие сформировать временное окно. Информационные входы, которыми являются входы п перемножителей 1, подключаются к контролируемым каналам (контактам) ОК.

Входные последовательности умножаются на соответствующие многочлены

gik(x), Q2k(x)9nk(x) при помощи п перемножителей 1. С выходов последних сигналы поступают на входы n-входового сумматора по модулю два, на выходе которого в каждый момент времени образуется сумма по модулю два значений сигналов контролируемых каналов, умноженных на соответствующие многочлены. Эта сумма по тактам синхронизации вводится в. формирователь 3, на выходах которого по завершении интервала контроля, который определяется

fe

00

ю ю о

временным окном, будет сформирована сигнатура, характеризующая текущее техническое состояние ОК. Сравнение полученной сигнатуры с эталонной происходит в блоке сравнения 4 путем ее поразрядного суммирования по модулю два с эталонной сигнатурой.

Результат сравнения поступает в параллельном коде в регистр сдвига 5 и после преобразования в последовательный код с выхода регистра 5 подается одновременно на входы п делителей 6, в которых осуществляется деление поступившего сигнала на многочлены gi(x), Q2(x), ..., gn(x), Остатки от деления, сформированные в каждом из п делителей 6, подаются на блоки детекторов 7 нуля, где и осуществляется анализ результатов контроля узла, исправные каналы будут характеризоваться нулевыми остатками от деления на соответствующие многочлены, неисправные-ненулевыми ос- татками.

QI к(х)92(х).дз(х)дп(х);

g2k(x)gi(x).gs(x)дп(х);

gnk(x)gi(x).g2(x)gn-i(x),

где дз(х) - многочлен формирователя 3.

Возможность обнаружения с помощью рассматриваемого многовходного сигна- турного анализатора канала с ошибкой обусловлена свойствами арифметических операций над конечными полями (в данном случае над подем G(F2). Блок 8 предназначен для выработки временного окна, т.е. интервала времени, в течение которого происходит сжатие тестовой последовательности в формирователе 3. Кроме того, данный блок синхронизирует п перемножителей 1 и формирователь 3, синхронизирует работу регистра 5 и п делителей 6, а также управляет процессом преобразования формата информации.

п детекторов нуля 7 предназначены для анализа остатков от дления в п делителях 6 на равенство нулю. Каждый из детекторов выполнен как многовходовый элемент ИЛИ, причем количество входов соответствует числу разрядов в регистре сдвига соответствующего делителя. Каждый выход.регистра сдвига делителя подключен к одному из входов элемента ИЛИ, поэтому на выходе последнего низкий уровень будет только в том случае, если во всех разрядах регистра записаны 0, что свидетельствует о равенстве нулю всего остатка от деления. Блок сравнения 4 выполнен на N элементах ИСКЛЮЧАЮЩЕЕ ИЛИ (где N - разрядность сигнатуры).

Формулаизобретения

1. Многоканальный сигнатурный анализатор, содержащий сумматор по модулю

два и формирователь сигнатур, информационный вход которого подключен к выходу сумматора по модулю два, отличающийся тем, что, с целью уменьшения времени локализации неисправностей в проверяемых каналах, он содержит группу из п перемножителей, блок сравнения, регистр сдвига, группу из п делителей, группу из п детекторов нуля, где п - число контролируемых каналов, блок управления, причем информационные входы п перемножителей группы являются первой группой информационных входов анализатора, выходы п перемножителей группы соединены с входами сумматора по модулю два, группа выходов формирователя сигнатур соединена с первой группой информационных входов блока сравнения, вторая группа информационных входов которого является второй группой информационных входов анализатора, группа выходов блока сравнения соединена с группой информационных входов регистра сдвига, выход которого соединен с информационными входами п делителей группы, группа информационных выходов каждого из которых соединена с группой входов соответствующего детектора нуля группы, вход сигнала Пуск/останов и синхровход блока управления являются одноименными входами анализатора, синхровходы формирователя сигнатур и п перемножителей группы объединены и подключены к первому выходу блока управления, вход параллельной загрузки регистра сдвига подключен к второму выходу блока управления, синхровходы п делителей группы и вход сдвига регистра сдвига объединены и подключены к третьему выходу блока управления, вход режима регистра сдвига подключен к четвертому выходу блока управления.

2. Анализатор по п. 1, о т л и ч а ю щ и й- с я тем, что блок управления содержит триггер, два счетчика и два элемента И, выход первого элемента И является первым выходом блока, выход триггера соединен с первым входом первого элемента И и является вторым выходом блока, выход второго элемента И соединен со счетным входом первого счетчика и является третьим выходом блока, выход первого разряда второго счетчика является четвертым выходом блока, первый вход второго элемента И объединен с вторым входом первого элемента И и образует синхровход блока, второй вход второго элемента И подключен к выходу второго разряда второго счетчика, третий вход второго элемента И подключен к инверсному выходу r-го разряда первого счетчика, синхровходы триггера и второго счет- Пуск/останов блока, где r Qlog2 +1). N чика объединены и образуют вход сигнала разрядность сигнатуры.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор (его варианты) | 1984 |

|

SU1252784A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ БЛОКОВ | 1991 |

|

RU2065202C1 |

| Сигнатурный анализатор | 1989 |

|

SU1624455A1 |

| Сигнатурный анализатор | 1983 |

|

SU1223230A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1343417A1 |

| Сигнатурный анализатор | 1984 |

|

SU1264180A1 |

| Сигнатурный анализатор | 1985 |

|

SU1256031A1 |

| МНОГОКАНАЛЬНЫЙ СИГНАТУРНЫЙ АНАЛИЗАТОР | 1996 |

|

RU2120136C1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1180902A1 |

| МНОГОКАНАЛЬНЫЙ СИГНАТУРНЫЙ АНАЛИЗАТОР | 1995 |

|

RU2087030C1 |

Изобретение относится к вычислительной технике и может быть использовано для тестового диагностирования многоканальных цифровых устройств. Цель изобретения - уменьшение времени локализации неисправностей в проверяемых каналах - достигается через разделение общей сигнатуры на составляющие, соответствующие каждому из проверяемых каналов. При этом анализатор за один цикл контроля дает возможность определить номера неисправных каналов. 1 з. п. ф-лы, 5 ил.

Фиг.З

ФигЛ

| Сигнатурный анализатор | 1981 |

|

SU1048475A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-03-07—Публикация

1990-01-22—Подача