Изобретение относится к вычислительной технике и может быть использовано в системах тестового диагностирования цифровых объектов.

Целью изобретения является повышение достоверности контроля.

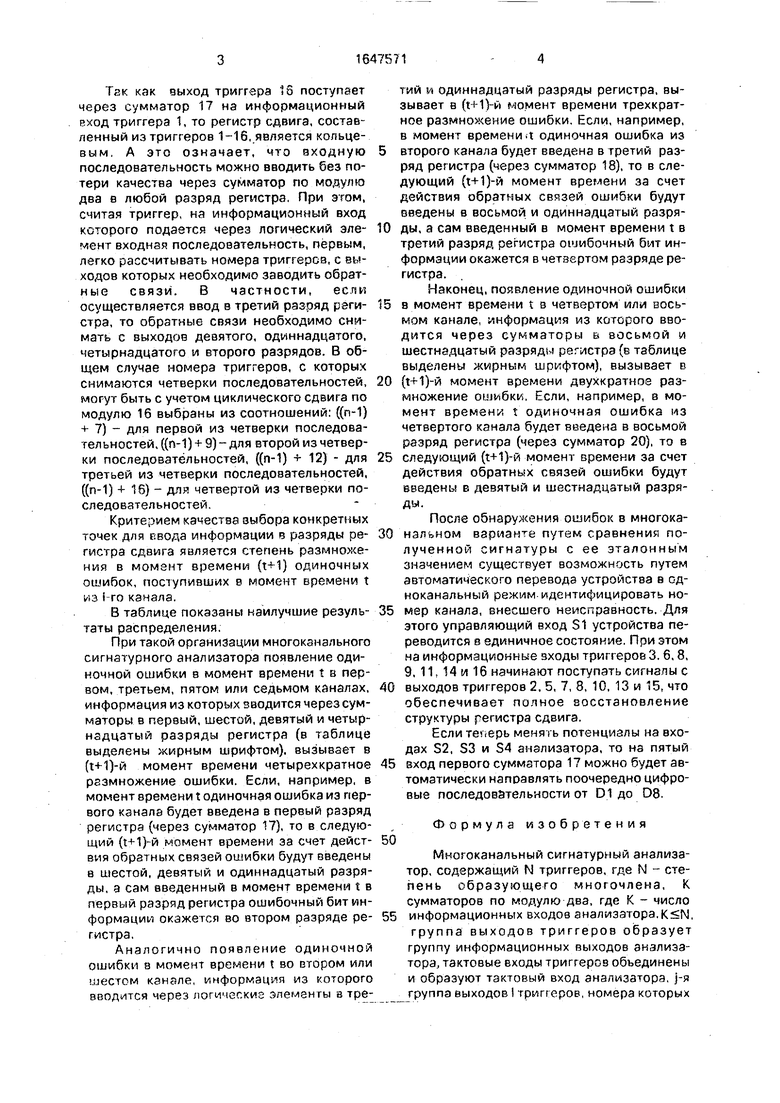

На чертеже показана схема многоканального сигнатурного анализатора.

Сигнализатор содержит триггеры 1-16, сумматоры 17-24 по модулю два, мультиплексоры 25-32. Рассматривается случай, когда N 16, К 8. Ф(х) х16 + х12 + х9 + х7 +

1, П1 1, П2 3, П3 6, П4 8, П5 9. П6 11,

л 14, пв 16, где п - номер триггера, на вход которого подается результирующая после суммирования по модулю два последовательность.

Устройство функционирует следующим образом.

Устройство переводится а многоканальный режим, для чего устанавливаются равными нулю потенциалы на входах анализатора S1, S2, S3, S4.

Восемь сумматоров 17-24 по мере ввода в устройство одновременно восьми цифровых последовательностей производят их суммирование по модулю 2 с четверкой последовательностей, заданных для каждого сумматора по следующим соображениям.

К сдвиговому регистру с обратными связями как к линейному устройству применим принцип суперпозиции, из которого следует, что реакция регистра на сумму из m входных величин равна сумме его реакций на каждую величину.в отдельности. Отсюда следует, что если входной сигнал регистра рассматривать как сумму по модулю 2 двоичных последовательностей, то полученная сигнатура будет эквивалентна сумме по модулю 2 индивидуальных сигнатур.

Известное устройство для од но канального сигнатурного анализа представляет собой линейный сдвиговый регистр с обратными связями, от 16, 12, 9 и 7-го разрядов регистра через сумматор по модулю два.

Описание регистра полиномом позволяет указать в сжатом виде, какие разряды сдвигового регистра необходимо связать с входами сумматора.

И

г

XI

сл

VI

Так как выход триггера 16 поступает через сумматор 17 на информационный РХОД триггера 1, то регистр сдвига, составленный из триггеров 1-16, является кольцевым. А это означает, что входную последовательность можно вводить без потери качества через сумматор по модулю два в любой разряд регистра, При этом, считая триггер, на информационный вход которого подается через логический элемент входная последовательность, первым, легко рассчитывать номера триггеров, с выходов которых необходимо заводить обрат- ные связи. В частности, ее пи осуществляется ввод в третий разряд регистра, то обратные связи необходимо снимать с выходов девятого, одиннадцатого, четырнадцатого и второго разрядов. В общем случае номера триггеров, с которых снимаются четверки последовательностей, могут быть с учетом циклического сдвига по модулю 16 выбраны из соотношений: ((п-1) + 7) - для первой из четверки последовательностей, ((п-1) + 9) - для второй из четверки последовательностей, ((п-1) + 12) - для третьей из четверки последовательностей, ((п-1) + 16) - для четвертой из четверки последовательностей.

Критерием качества выбора конкретных точек для ввода информации в разряды регистра сдвига является степень размножения в момент времени (t-Ч) одиночных ошибок, поступивших в момент времени t из i го канала.

В таблице показаны наилучшие результаты распределения.

При такой организации многоканального сигнатурного анализатора появление одиночной ошибки в момент времени t в первом, третьем, пятом или седьмом каналах, информация из которых вводится через сумматоры в первый, шестой, девятый и четырнадцатый разряды регистра (в таблице выделены жирным шрифтом), вызывает в (t-H)-u момент времени четырехкратное размножение ошибки. Если, например, в момент времени t одиночная ошибка из первого канала будет введена в первый разряд регистра (через сумматор 17), то в следующий (1+1)-й момент времени за счет действия обратных связей ошибки будут введены в шестой, девятый и одиннадцатый разряды, а сам введенный в момент времени t в первый разряд регистра ошибочный бит информации окажется во втором разряде регистра.

Аналогично появление одиночной ошибки в момент времени t во втором или шестом канале, информация из которого вводится через логимег.киз элементы & третий и одиннадцатый разряды регистра, вызывает в (t+D-й момент времени трехкратное размножение ошибки. Если, например, в момент времени.t одиночная ошибка из

второго канала будет введена в третий разряд регистра (через сумматор 18), то в следующий (t+IJ-й момент времени за счет действия обратных связей ошибки будут введены в восьмой и одиннадцатый разряды, а сам введенный в момент времени t в третий разряд регистра ошибочный бит информации окажется в четвертом разряде регистра.

Наконец, появление одиночной ошибки

в момент времени t в четвертом или восьмом канале, информация из которого вводится через сумматоры в восьмой и шестнадцатый разряды регистра (в таблице выделены жирным шрифтом), вызывает в

(т+1)-й момент времени двухкратное размножение ошибки. Если, например, а момент времени t одиночная ошибка из четвертого канала будет введена в восьмой разряд регистра (через сумматор 20), то в

следующий (t+IJ-й момент времени за счет действия обратных связей ошибки будут введены в девятый и шестнадцатый разряды.

После обнаружения ошибок в многоканаяьном варианте путем сравнения полученной сигнатуры с ее эталонным значением существует возможность путем автоматического перевода устройства в сд- ноканальный режим идентифицировать номер канала, внесшего неисправность. Для этого управляющий вход S1 устройства переводится в единичное состояние. При этом на информационные эходы триггеров 3.6,8, 9, 11. 14 и 16 начинают поступать сигналы с

выходов триггеров 2, 5, 7, 8, 10, 13 и 15, что обеспечивает полное восстановление структуры регистра сдвига.

Еслитеьерь менять потенциалы на входах S2, S3 и S4 анализатора, то на пятый

вход первого сумматора 17 можно будет автоматически направлять поочередно цифровые последовательности от D1 до D8.

50

Формула изобретения

Многоканальный сигнатурный анализатор, содержащий N триггеров, где N - степень образующего многочлена, К сумматоров по модулю два, где К - число 5 информационных входов анализатора., группа выходов триггеров образует группу информационных выходов анализатора, тактовые входы триггеров объединены и образуют тактовый вход анализатора, j-я группа выходов I триггеров, номера которых

определяются видом образующего многочлена, где I - число ненулевых коэффициентов образующего многочлена, j , подключены к входам с 1-го по i-й j-ro сумматора по модулю два, (1+1)-й вход каждого из которых, кроме первого, образует j-й информационный вход анализатора, выход первого сумматора по модулю два соединен с информационным входом первого триггера, отличающийся тем. что, с целью увеличения достоверности контроля, он дополнительно содержит К мультиплексоров, причем j-й информационный вход первого мультиплексора подключен к j-му информационному входу анализатора, выход перво0

5

го мультиплексора соединен с (М)-ч входом первого сумматора по модулю два, выход j-го сумматора по модулю два, кроме первого, соединен с первым информационным входом j-ro мультиплексора, выход j-ro мультиплексора, кроме первого, соединен с информационным входом nj-ro триггера, где 1 nj N,выход m-ro триггера,где , N-1. ). соединен с информационны м входом (т + 1)-го триггера, выход (nj-1)- го триггера соединен с вторым информационным входом j-ro мультиплексора, управляющие входы мультиплексоров образуют группу входов задания режима анализатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Многофункциональный модуль для устройств встроенного контроля | 1989 |

|

SU1619275A1 |

| Многоканальный сигнатурный анализатор для микропроцессорной системы | 1986 |

|

SU1374226A1 |

| Сигнатурный анализатор | 1983 |

|

SU1223230A1 |

| Многоканальный сигнатурный анализатор | 1990 |

|

SU1718220A1 |

| Сигнатурный анализатор | 1981 |

|

SU962962A1 |

| Многофункциональный модуль для устройств встроенного контроля | 1987 |

|

SU1529222A1 |

| Сигнатурный анализатор | 1989 |

|

SU1714602A1 |

| Сигнатурный анализатор | 1984 |

|

SU1193680A2 |

| Сигнатурный анализатор | 1987 |

|

SU1416997A1 |

Изобретение относится к вычислительной технике и может использоваться в системах тестового диагностирования цифровых объектов. Цель изобретения - увеличение достоверности контроля. Многоканальный сигнатурный анализатор содержит триггеры 1-16, сумматоры 17-24 по модулю два, мультиплексоры 25-32. После обнаружения ошибок в многоканальных последовательностях существует возможность идентифицировать номер канала с ошибкой. 1 ил., 1 табл.

| Электроника | |||

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| Вопросы радиоэлектроники | |||

| Серия Технология производства и оборудования | |||

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

| Прибор для массовой выработки лекал | 1921 |

|

SU118A1 |

Авторы

Даты

1991-05-07—Публикация

1989-04-07—Подача