индивидуальные канальные преобразователи. Повышение надежности и достоверности принимаемой информации в устройстве достигается благодаря тому, что данные передаются Дважды - прямым м инверсным кодами, причем широтно-модулированные сигналы, отображающие принятые коды, подаются в канальные преобразователи в режиме тестирования поочередно. При работоспособности основных узлов устройства показания выходных приборов должны соответствовать половине максимальных значений. Таким образом, тестирование проводится без использования внешних по отношению к устройству блоков и дополнительных приборов.

Указанное устройство характеризуется недостаточной надежностью из-за наличия в канальных преобразователях индивидуальных многоразрядных элементов памяти,

Наиболее близким по технической сущности к предлагаемому является многоканальный цифроаналоговый преобразователь, содержащий канальный преобразователь на индивидуальных коммутируемых источниках тока, выходы которого являются выходами устройства, блок управления, содержащий первый регистр сдвига, подключенный информационным входом к соответствующему еыходу блока приема, и блок приема, вход которого является первым входом устройства и соединен с линией связи, а выходы управления и информационный соединены с соответствующими входами блока управления, формирователь сигналов управления, выполненный на первом и втором .счетчиках, мультиплексоре.

8 известном устройстве решена задача автоматического преобразования кодов значений параметров в наборы весовых временных интервалов с использованием общего формирователи широтно-модулмрованных импульсов, а также тестирование основных узлов, что обеспечивает упрощение общих узлов устройства.

Однако в канальных преобразователях этого устройства применяются индивидуальные элементу памяти - регистры сдвига с последовательным вводом и последовательным выводом кодов, число разрядов в которых равно числу разрядов р принимаемых ходах ,, отображающих значения параметров. увеличении числа каналов преобразования объем аппаратуры индивидуальной части становится неприемлемо большим, что снижает надежность устройства в целом.

Цель изобретения - повышение надежности устройства за счет оптимального распределения функций между общей и индивидуальной частями многоканального цифроаналогового преобразователя.

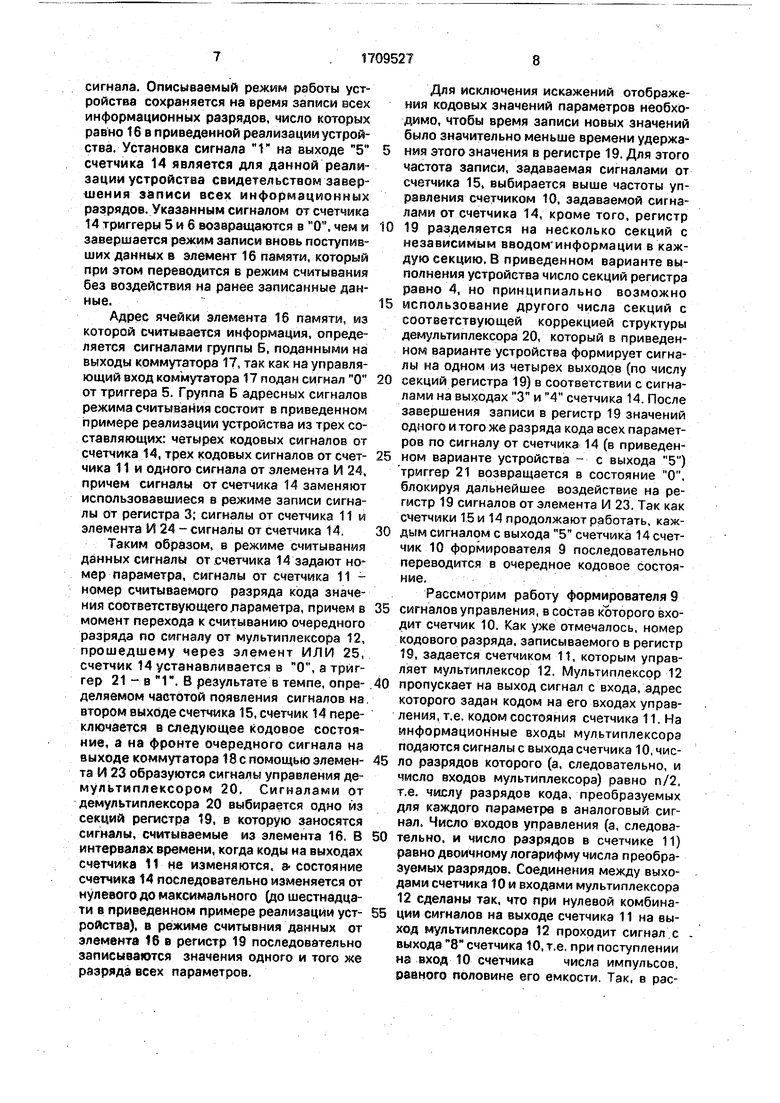

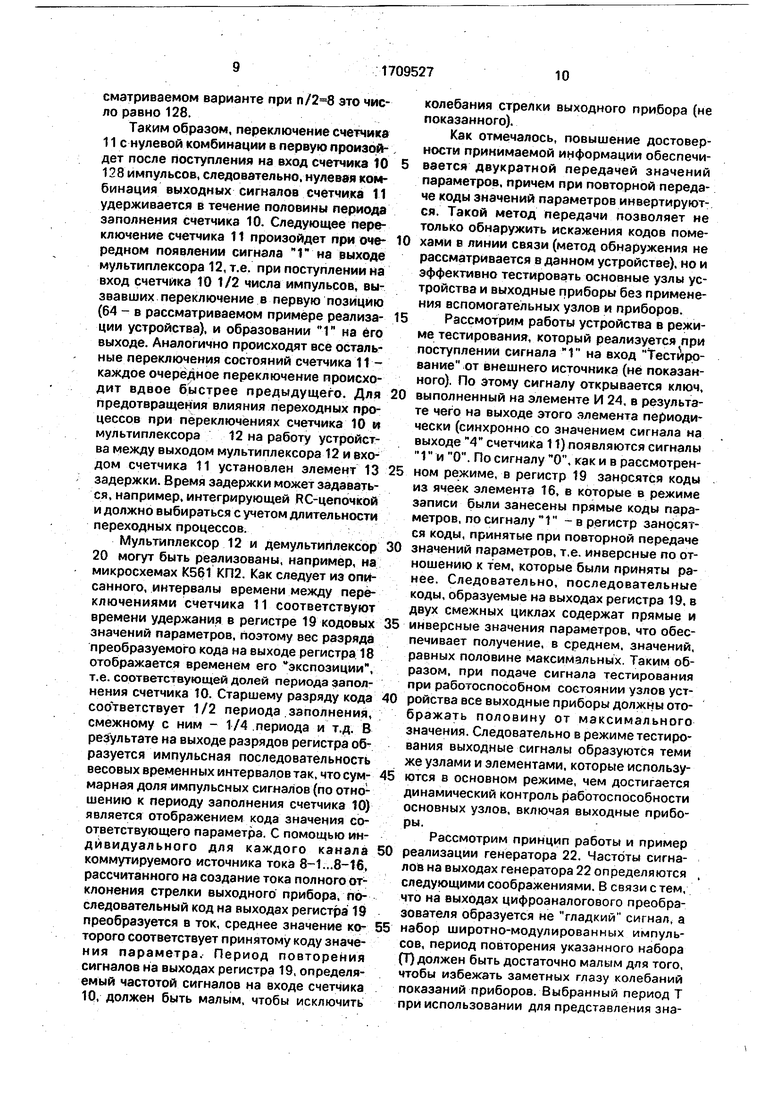

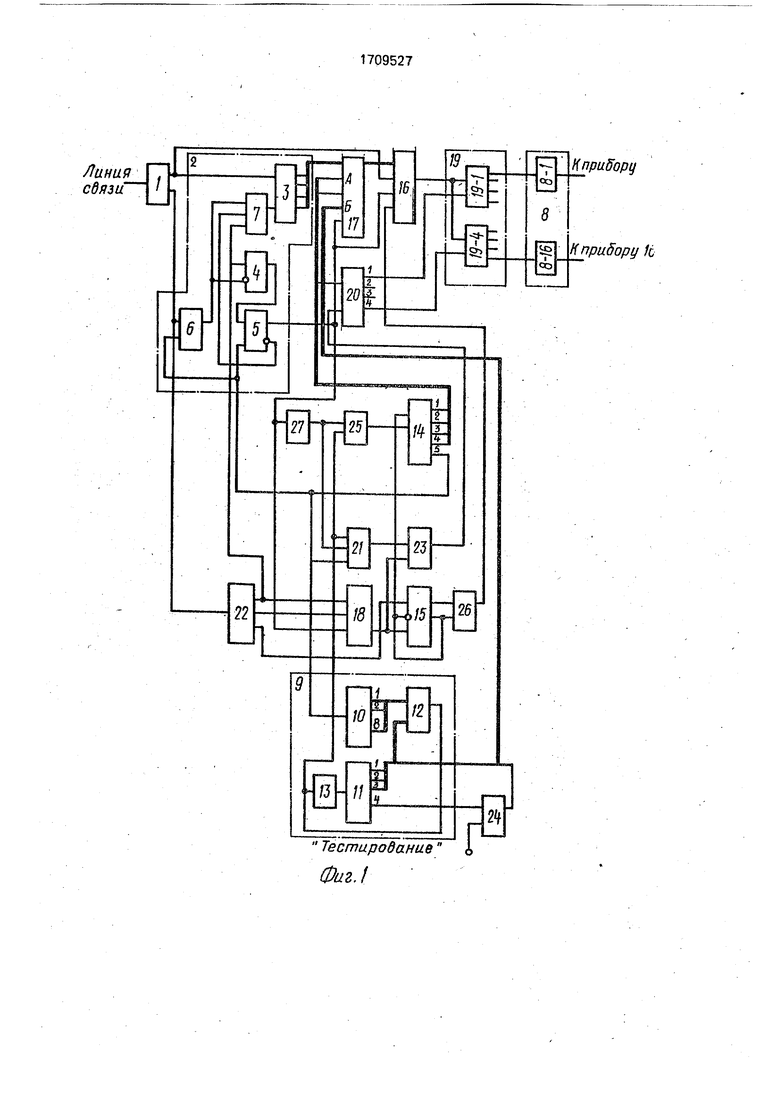

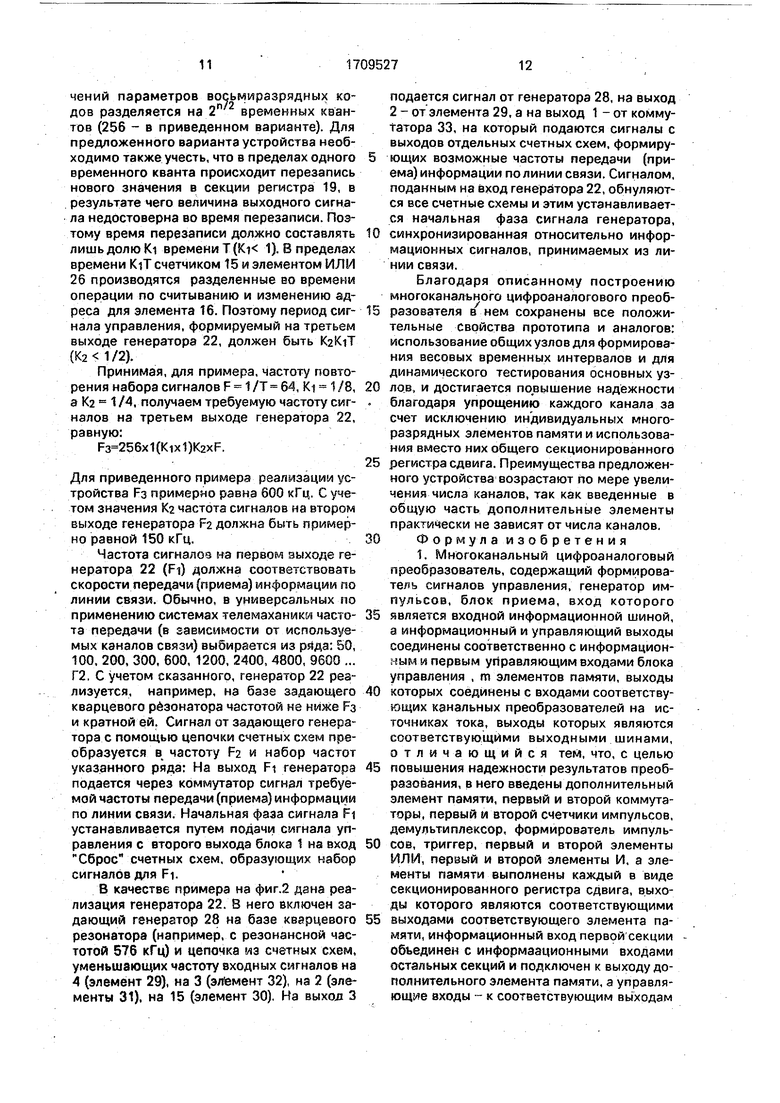

На фиг.1 показана структурная схема

устройства.

Устройство содержит блок 1 приема, вход которого является первым входом устройства и соединен с линией связи. Выходы информационный и управления блока 1

0 подключены к блоку 2 управления. Устройство включает также канальные преобразователи 8 (16 - для приведенного примера реализации устройства), выполненные на индивидуальных для каждого канала коммутируемых источниках тока 8-1,., 8-16, вь1ходы которых являются выходами К прибору 1... К прибору 16 устройства, формирователь 9 сигналов управления, первый Н и второй 15 счетчики, элемент 16 памяти, первый 17 и второй 18 коммутаторы, секционированный регистр 19 сдвига, состоящий в приведенном примере реализации устройства из секций 19-1... 19-4, демультиплексор 20 с выходами 1...4 для приведенного

5 примера реализации устройства, триггер -21, генератор 22 тактовых импульсов, первый 23 и второй 24 элементы И, причем вход элемента И 24 является входом Тестирование устройства, а также первый 25 и второй

0 26 элементы ИЛИ, формирователь 27 импульсов.

Блок 2 управления включает счетчик 4, первый 5 и второй 6 триггеры, элемент И 7 м регистр 3 сдвига.

Б Формирователь 9 сигналов управления содержит первый 10 и второй 11 счетчики, мультиплесор 12 и элемент 13 задержки.

Окружности у входов и выходов элементов являются знаком инверсии соответству0 ющих входных или выходных сигналов.

Многоканальный цифроаналоговый преобразователь работает следующим образом.

На вход блока t приема из линии связи

5 поступает последовательный код, содержащий информационную и адресную части. Информационная часть представляет переданный дважды - прямым и инверсным кодами п-разрядный двоичный код значения

0 телеметрического параметра, номер которого определяется кодом адресной части. Блок 1 выделяет начало посылки, совпадающее с началом приема адресной части. Блок 1 формирует при этом сигнал на втором,

5 управляющем выходе. Этим сигналом корректируется фаза генератора тактовых импульсов так, что фронты сигналов на первом выхода генератора 22 совпадают с серединами временных интервалов принимаемых иазрядоа кода, Однозременноустанавливается в 1 триггер 6 блока 2 управления, деблокируется счетчик 4 и элемент И 7.

Элемент И 7 пропускает на вход регистра 3 сдвига тактовые сигналы с первого выхода генератора 22, обеспечивая ввод в Р гистр адресной части принимаемого кода.

Регистры 3 и 19 могут быть реализованы, например, на микросхемах К561 и ИР2, обеспечивающих режим последовательного ввода и параллельного вывода информации.

Синхронно с вводом данных в регистр 3 тактовые импульсы генератора 22 вводятся в счетчик 4.

Счетчик 4 и другие счетчики устройства могут быть реализованы, например, на микросхемах К561 ИЕ10, на входы которых подаются соответственно тактовые импульсы, сигналы управления и сброса в О. Если-в устройстве на какой-либо счетчик рабочий сигнал управления подан постоянно или сигнал сброса в О не используется, указанные сигналы для упрощения чертежа не показываются.

На выходе счетчика 4 oбpaзyetcя сигнал 1 при завершении ввода кода номера канала в регистр 3. В приведенном примере реализации устройства число каналов принято, равным 16, поэтому регистр 3 должен быть четырехразрядным, а счетчик 4-трехразрядным. По сигналу 1 от старшего разряда счётчика 4 устанавливается в 1 триггер 5 и блокирует подачу в регистр 3 тактовых импульсов, обеспечивая сохранение в нем принятого кода номера канала.

С указанного момента начинается этап ввода кода значения параметра выбранного канала в элемент 16 памяти. Исходные условия для этапа записи формируются следующим образом. По фронту сигнала от триггера 5 образуется импульс формирователем 27, который через элемент ИЛИ 25 устанавливает в О счетчик 14, а в 1 триггер 21. Коммутатор 18 сигналом 1 от триггера 5 устанавливается на пропуск сигналов с его первого входа, т.е. с первого выхода генератора 22, на котором частота сигналов соответствует частоте коммутации сигналов в линии связи. Коммутатор 17 сигналом 1 от триггера 5 устанавливается на пропуск на выход сигналов входной группы, условно обозначенной группой А, содержащей четырехразрядный код регистра 3 и четырехразрядный (КОД счетчика 14. Элемент 16 памяти сигналом 1 по третьему входу от триггера 5 устанавливается в режим no-i следовательного поразрядного приема данных.

Коммутаторы 17 и 18 могут быть реализованы, например, на микросхемах К561

ЛС2, элемент памяти - на микросхеме К561 РУ2 с последовательным вводом и последовательным выводом до 256 бит информации.

Информационная емкость элемента 16 памяти должна быть равной произведению числа каналов на число информационных разрядов п для каждого канала. В приведенном примере реализации устройства используется двукратная передача (прямым и инверсным кодами) восьмиразрядного кода значения параметра, т.е. п 16. Повторение передачи позволяет повысить помехозащищенность устройства (реализация помехозащищенного декодера не рассматривается в предложенном устройстве), а также эффективно диагностировать работоспособность основных узлов устройства. Таким образом, требуемая емкость элемента памяти для рассматриваемого примера реализации устройства должна быть равна 16 X 16 256 бит.

Для управления элементом 16 используется генератор 22, коммутатор 18, счетчики 14 и 15.И элемент ИЛИ 26, Коммутатор установлен на пропуск на выход сигналов с первого выхода генератора 22. В начале каждой паузы между сигналами генератора 22 на выходе коммутатора 18 образуется сигнал О и счетчик 15 деблокируется, так как на его третьем входе исчезает сигнал 1 и становится чувствительным к тактовым сигналам на его первом входе. Частота этих сигналов, сформированных на третьем выходе генератора 22, значительно выше частоты сигналов на первом выходе и ограничивается сверху быстродействием используемых элементов. Первый введенный в счетчик 15 тактовый импульс формирует сигнал 1 на первом выходе и выходе элемента ИЛИ 26. Этот сигнал, поступая на четвёртый вход элемента 16, блокирует его чувствительность к адресным и информационному сигналам. В результате по адресу, заданному комбинацией сигналов групп-ы А, в элемент 16 записывается информационный сигнал, выдаваемый к описанному моменту времени блоком 1. С задержкой, равной периоду сигналу на первом входе счетчика 15, образуется сигнал 1 на втором выходе счетчика 15. При этом сигнал 1 на выходе элемента ИЛИ 26 не исчезает (т.е. по-прежнему блокируется элемент 16), но формируется сигнал перевода счетчика 14 в следующую позицию, а счетчик 15 сигНалом на его втором выходе блокируется и сохраняет установленное состояние до момента формирования сигнала 1 на выходе коммутатора 18, т.е. до начала цикла записи в элемент 16 очередного информационного сигнала. Описываемый режим работы устройства сохраняется на время записи всех информационных разрядов, число которых равно 16 в приведенной реализации устройства. Установка сигнала Г на выходе 5 счетчика 14 является для данной реализации устройства свидетельством завершения записи всех информационных разрядов. Указанным сигналом от счетчика 14 триггеры 5 и б возвращаются в О, чем и завершается режим записи вновь поступивших данных в элемент 16 памяти, который при зтом переводится в режим считывания без воздействия на ранее записанные данные. Адрес ячейки элемента 16 памяти, из которой считывается информация, определяется сигналами группы 5, поданными на выходы коммутатора 17, так как на управляющий вход коммутатора 17 подан сигнал О от триггера 5. Группа Б адресных сигналов режима считывания состоит в приведенном примере реализации устрюйства из трех составляющих: четырех кодовых сигналов от счетчика 14, трех кодовых сигналов от счетчика 11 и одного сигнала от элемента И 24, причем сигналы от счетчика 14 заменяют использовавшиеся в режиме записи сигналы от регистра 3; сигналы от счетчика 11 и элемента И 24 - сигналы от счетчика 14. Таким образом, в режиме считывания данных сигналы от .счетчика 14 задают номер параметра, сигналы от счетчика 11 номер считываемого разряда кода значения соответствующего лараметра, причем в момент перехода к считыванию очередного разряда по сигналу от мультиплексора 12, прошедшему через элемент ИЛИ 25, счетчик 14 устанавливается в О, а триггер 21 - в 1. В результате в темпе, определяемом частотой появления сигналов на втором выходе счетчика 15, счетчик 14 переключается в следующее кодовое состояние, а на фронте очередного сигнала на выходе коммутатора 18с помощью элемента И 23 образуются сигналы управления демультиплексором 20. Сигналами от демультиплексора 20 выбирается одно из секций регистра 19, в которую заносятся сигналы, считываемые из элемента 16. В интервалах времени, когда коды на выходах счетчика It не изменяются, а- состояние счетчика 14 последовательно изменяется от нулевого до максимального {до шестнадцати в приведенном примере реализации устройства), в считывния данных от элемента 16 в регистр 19 последовательно записываются значения одного и того же разряда всех параметров. Для исключения искажений отображения кодовых значений параметров необходимо, чтобы время записи новых значений было значительно меньше времени удержания этого значения в регистре 19. Для этого частота записи, задаваемая сигналами от счетчика 15, выбирается выше частоты управления счетчиком 10, задаваемой сигналами от счетчика 14, кроме того, регистр 19 разделяется на несколько секций с независимым вводоминформации в каждую секцию. В приведенном варианте выполнения устройства число секций регистра равно 4, но принципиально возможно использование другого числа секций с соответствующей коррекцией структуры демультиплексора 20, который в приведенном варианте устройства формирует сигналы на одном из четырех выходов (по числу секций регистра 19) в соответствии с сигналами на выходах 3 и 4 счетчика 14. После завершения записи в регистр 19 значений одного и того же разряда кода всех параметров по сигналу от счетчика 14 (в приведенном варианте устройства - с выхода 5) триггер 21 возвращается в состояние О, блокируя дальнейшее воздействие на регистр 19 сигналов от элемента И 23. Так как счетчики 15 и 14 продолжают работать, каж,цым сигналом с выхода 5 счетчика 14 счетчик 10 формирователя 9 последовательно переводится в очередное кодовое состояние. Рассмотрим работу формирователя 9 сигналов управления, в состав которого входит счетчик 10. Как уже отмечалось, номер кодового разряда, записываемого в регистр 19, задается счетчиком 11, которым управляет мультиплексор 12. Мультиплексор 12 пропускает на выход сигнал с входа, адрес которого задан кодом на его входах управления, т.е. кодом состояния счетчика 11. На информационные входы мультиплексора подаются сигналы с выхода счетчика 10, число разрядов которого (а, следовательно, и число входов мультиплексора) равно п/2, т.е. числу разрядов кода, преобразуемых для каждого параметре в аналоговый сигнал. Число входов управления (а, следовательно. и число разрядов в счетчике 11) равно двоичному логарифму числа преобразуемых разрядов. Соединения между выходами счетчика 10 и входами мультиплексора 12 сделаны так, что при нулевой комбинации сигналов на выходе счетчика 11 на выход мультиплексора 12 проходит сигнал,с выхода 8 счетчика 10, т.е. при поступлении на вход 10 счетчика числа импульсов. равного половине его емкости. Так, в рассматриваемом варианте при п/2-8 это число равно 128,

Таким образом, переключение счетчика 11 с нулевой комбинации в первую произойдет после поступления на вход счетчика 10 128 импульсов, следовательно, нулевая комбинация выходных сигналов счетчика 11 удерживается в течение половины периода заполнения счетчика 10. Следующее переключение счетчика 11 произойдет при очередном появлении сигнала 1 на выходе мультиплексора 12, т.е. при поступлении на вход счетчика 10 1/2 числа импульсов, вызвавших переключение в первую позицию (64 - в рассматриваемом примере реализации устройства), и образовании 1 на его выходе. Аналогично происходят все остальные переключения состояний счетчика 11 каждое очерёдное переключение происходит вдвое бь1стрее предыдущего. Для предотвращения влияния переходных процессов при переключениях счетчика 10 и мультиплексора 12 на работу устройства между выходом мультиплексора 12 и входом счетчика 11 установлен элемент 13 задержки. Время задержки может задаваться, например, интегрирующей RC-цепочкой и должно выбираться с учетом длительности переходных процессов.

Мультиплексор 12 и демультиплексор 20 могут быть реализованы, например, на микросхемах К561 КП2. Как следует из описанного, интервалы времени между переключениями счетчика 11 соответствуют времени удержания в регистре 19 кодовых значений параметров, поэтому вес разряда преобразуемого кода на выходе регистра 18 отображается временем его экспозиции, т.е. соответствующей долей периода заполнения счетчика 10. Старшему разряду кода соответствует 1/2 периода .заполнения, смежному с ним - 1/4 .периода и т.д. В результате на выходе разрядов регистра образуется импульсная последовательность весовых временных интервалов так, что суммарная доля импульсных сигналов (по отношению к периоду заполнения счетчика 10) является отображением кода значения соответствующего параметра. С помощью индивидуального для каждого канала коммутируемого источника тока 8-1...8-16, рассчитанного на создание тока полного отклонения стрелки выходного прибора, последовательный код на выходах регистра 19 преобразуется в ток, среднее значение ко торого соответствует принятому коду значения параметра. Период повторения сигналов на выходах регистра 19, определяемый частотой сигналов на входе счетчика Ю, должен быть малым, чтобы исключить

колебания стрелки выходного прибора (не показанного).

Как отмечалось, повышение достоверности принимаемой И1 формации обеспечивается двукратной передачей значений параметров, причем при повторной передаче коды значений параметров инвертируются. Такой метод передачи позволяет не только обнаружить искажения кодов помехами в линии связи (метод обнаружения не рассматривается в данном устройстве), но и эффективно тестировать основные узлы устройства и выходные приборы без применения вспомогательных узлов и приборов.

Рассмотрим работы устройства в режиме тестирования, который реализуется при поступлении сигнала 1 на вход Тестирование от внешнего источника (не показанного). По этому сигналу открывается ключ, выполненный на элементе И 24, в результате чего на выходе этого элемента периодически (синхронно со значением сигнала на выходе 4 счетчика 11) появляются сигналы 1 и О. По сигналу О, как и в рассмотренном режиме, в регистр 19 заносятся коды из ячеек элемента 16, в которые в режиме записи были занесены прямые коды параметров, по сигналу 1 - в регистр заносятся коды, принятые при повторной передаче значений параметров, т.е. инверсные по отношению к тем, которые были приняты ранее. Следовательно, последовательные коды, образуемые на выходах регистра 19, в двух смежных циклах содержат прямые и инверсные значения параметров, что обеспечивает получение, в среднем, значений, равных половине максимальных. Таким образом, при подаче сигнала тестирования при работоспособном состоянии узлов устройства все выходные приборы должны отображать половину от максимального значения. Следовательно в режиме тестирования выходные сигналы образуются теми же узлами и элементами, которые используются в основном режиме, чем достигается динамический контроль работоспособности основных узлов, включая выходные приборы.

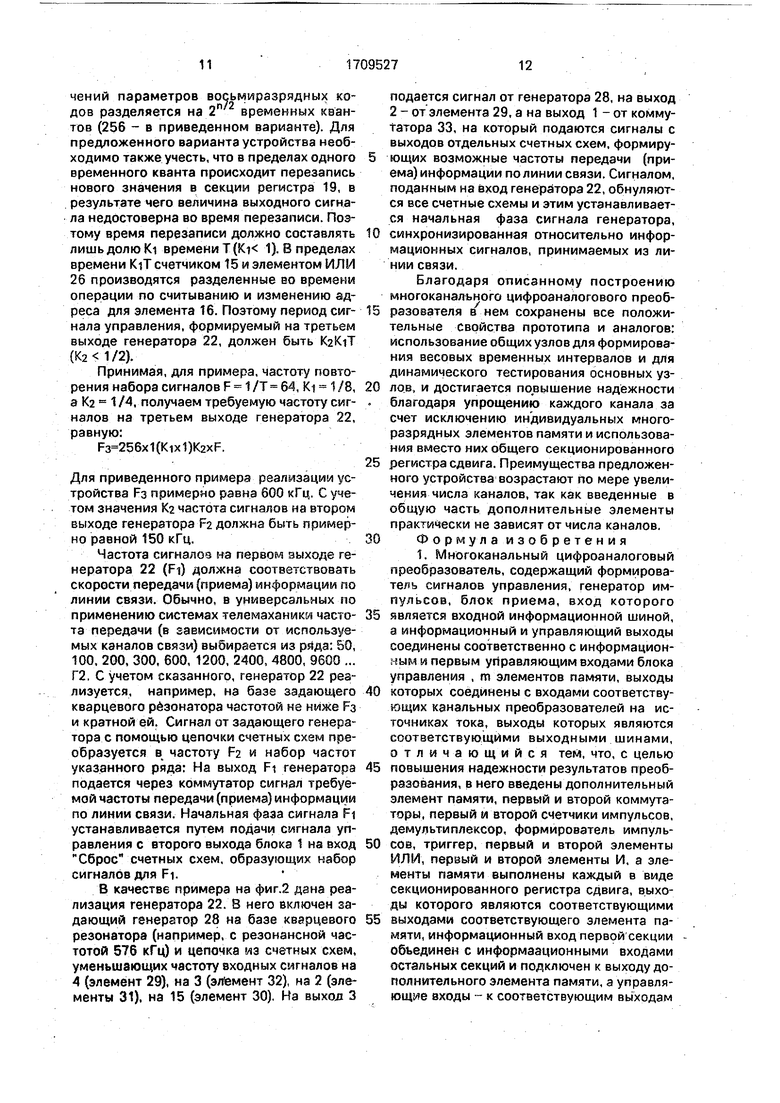

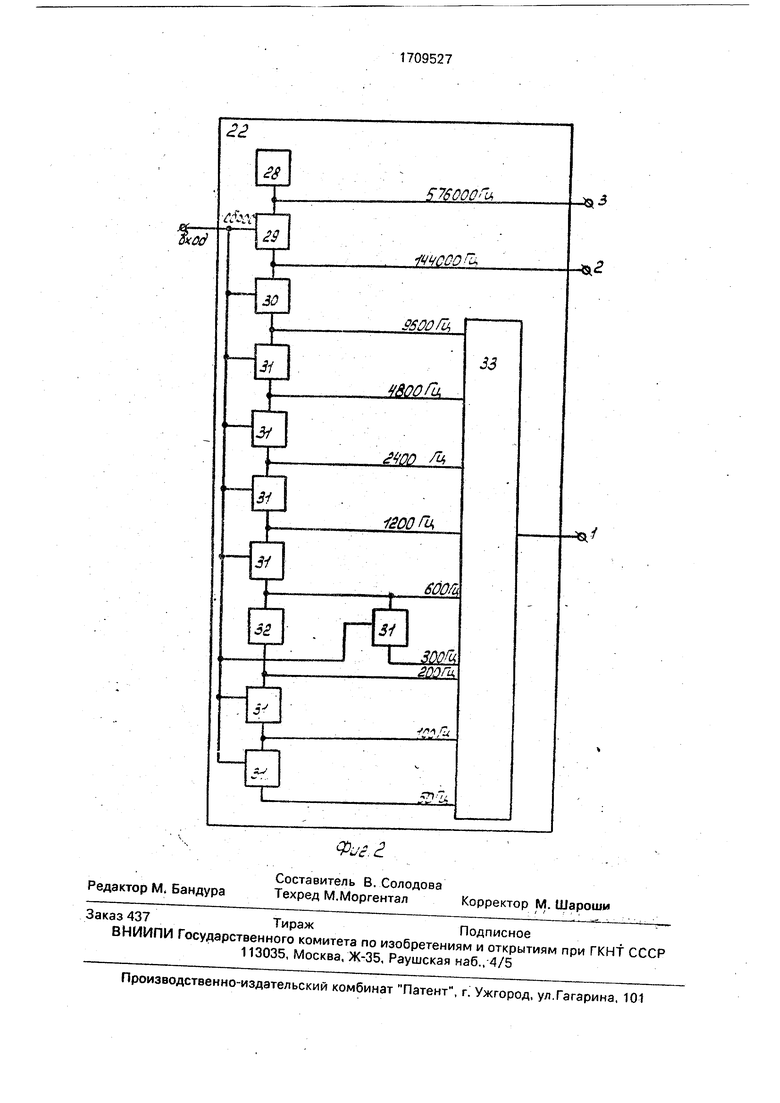

Рассмотрим принцип работы и пример реализации генератора 22. Частоты сигналов на выходах генератора 22 определяются следующими соображениями. В связи с тем, что на выходах цифроаналогового преобразователя образуется не гладкий сигнал, а набор широтно-модулированных импульсов, период повторения указанного набора (Т) должен быть достаточно малым для того, чтобы избежать заметных глазу колебаний показаний приборов. Выбранный период Т при использовании для представления значений параметров восьмиразрядных кодов разделяется на временных квантов (256 - в приведенном варианте). Для предложенного варианта устройства необходимо также учесть, что в пределах одного временного кванта происходит перезапись нового значения в секции регистра 19, в результате чего величина выходного сигнала недостоверна во время перезаписи. Поэтому время перезаписи должно составлять лишь долю Ki времени Т (Ki 1). 8 пределах времени KiT счетчиком 15 и элементом ИЛИ 26 производятся разделенные во времени операции по считыванию и изменению адреса для элемента 16. Поэтому период сигнала управления, формируемый на третьем выходе генератора 22, должен быть K2KiT (.

Принимая, для примера, частоту повторения набора сигналов F 1 /Т 64, Ki 1 /8, а К2 1/4, получаем требуемую частоту сигналов на третьем выходе генератора 22, равную:

F3 256x1(Kix1)K2xF.

Для приведенного примера реализации устройства РЗ примерно равна 600 кГц. С учетом значения К2 частота сигналов на втором выходе генератора F2 должна быть примерно равной 150 кГц.

Частота сигналоз на первом выходе генератора 22 (FI) должна соответствовать скорости передачи (приема) информации по линии связи. Обычно, в универсальных по применению системах телемаханики частота передачи (в зависимости от используемых каналов связи) выбирается из 50, 100. 200, 300. 600, 1200, 2400, 4800, 9600 ... Г2, С учетом сказанного, генератор 22 реализуется, например, на базе задающего кварцевого резонатора частотой не ниже Fa и кратной ей. Сигнал от задающего генератора с помощью цепочки счетных схем преобразуется в частоту F2 и набор частот указанного ряда; На выход FI генератора подается через коммутатор сигнал требуемой частоты передачи (приема) информации по линии связи. Начальная фаза сигнала Fi устанавливается путем подачи сигнала управления с второго выхода блока 1 на вход Сброс счетных схем, образующих набор сигналов для Fi.

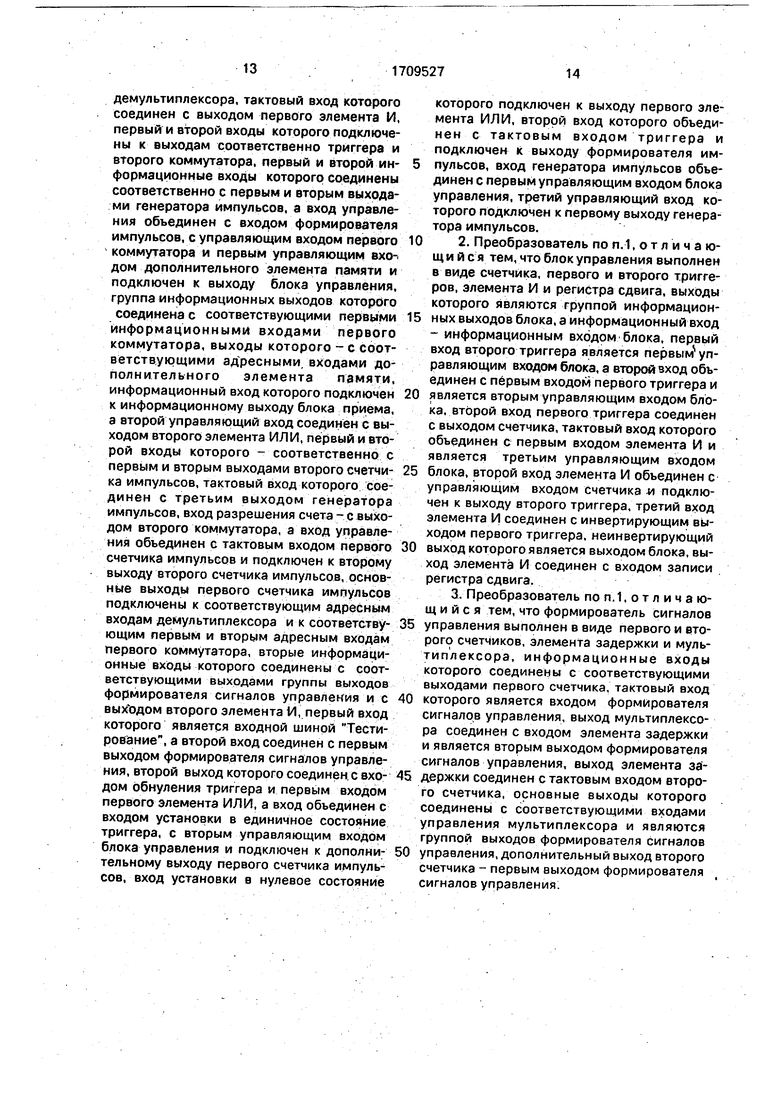

В качестве примера на фиг.2 дана реализация генератора 22. В него включен задающий генератор 28 на базе кварцевого резонатора (например, с резонансной частотой 576 кГц) и цепочка из счетных схем, уменьшающих частоту входных сигналов на 4 (элемент 29), на 3 (элемент 32), на 2 (элементы 31), на 15 (элемент 30), На выхол 3

подается сигнал от генератора 28, на выход 2 - от элемента 29, а на выход 1 - от коммутатора 33, на который подаются сигналы с выходов отдельных счетных схем, формирующих возможные частоты передачи (приема) информации по линии связи. Сигналом, поданным на вход генератора 22, обнуляются все счетные схемы и этим устанавливается начальная фаза сигнала генератора,

0 синхронизированная относительно информационных сигналов, принимаемых из линии связи.

Благодаря описанному построению многоканального цифроаналогового преобразователя в нем сохранены все положительные свойства прототипа и аналогов: использование общих узлов для формирования весовых временных интервалов и для динамического тестирования основных уз0 лав, и достигается повышение надежности благодаря упрощению каждого канала за счет исключению индивидуальных многоразрядных элементов памяти и использования вместо них общего секционированного

5 регистра сдвига. Преимущества предложенного устройства возрастают по мере увеличения числа каналов, так как введенные в общую часть дополнительные элементы практически не зависят от числа каналов.

0 Формула изобретения

1. Многоканальный цифроаналоговый преобразователь, содержащий формирователь сигналов управления, генератор импульсов, блок приема, вход которого

5 является входной информационной шиной, а информационный и управляющий выходы соединены соответственно с информационным и первым управляющим входами блока управления , m элементов памяти, выходы

0 которых соединены с входами соответствующих канальных преобразователей на источниках тока, выходы которых являются соответствующими выходными шинами, отличающийся тем, что, с целью

5 повышения надежности результатов преобразования, в него введены дополнительный элемент памяти, первый и второй коммутаторы, первый и второй сметчики импульсов, демультиплексор, формирователь импульсов, триггер, первый и второй элементы ИЛИ, первый и второй элементы И, а элементы памяти выполнены каждый в виде секционированного регистра сдвига, выходы которого являются соответствующими

5 выходами соответствующего элемента памяти, информационный вход первой секции объединен с информаационными входами остальных секций и подключен к выходу дополнительного элемента памяти, а управляющее входы - к соответствующим выходам

демультиплексора, тактовый вход которого соединен с выходом первого элемента И, первый и второй входы которого подключены к выходам соответственно триггера и второго коммутатора, первый и второй информационные входы которого соединены соответственно с первым и вторым выходами генератора импульсов, а вход управления объединен с входом формирователя импульсов, с управляющим входом первого коммутатора и первым управляющим входом дополнительного элемента памяти и подключен к выходу блока управления, группа информационных выходов которого соединена с соответствующими первыми информационными входами первого коммутатора, выходы которого - с соответствующими адресными, входами дополнительного элемента памяти, информационный вход которого подключен к информационному выходу блока приёма, а второй управляющий вход соединен с выходом второго элемента ИЛИ, первый и второй входы которого - соответственно с первым и вторым выходами второго счетчика импульсов, тактовый вход которого соединен с третьим выходом гене|ратора импульсов, вход разрешения счета- с выходом второго коммутатора, а вхОд управления объединен с тактовым входом первого счетчика импульсов и подключен к второму выходу второго счетчика импульсов, основные выходы первого счетчика импульсов подключены к соответствующим адресным входам демультиплексора и к соответствующим первым и вторым адресным входам первого коммутатора, вторые информационные вхОды которого соединены с соответствующими выходами группы выходов формирователя сигналов управлекйя и с выходом второго элемента 1/1, первый вход которого является входной шиной Тестирование, а второй вход соединен с первым выходом формирователя сигналов управления, второй выход которого соединен, с входом Обнуления триггера и первь1м входом первого элемента ИЛИ, а вход объединен с входом установки в единичное состояние триггера, с вторым управляющим входОм блока управления и подключен к дополнительному выходу первого счетчика импульсов, вход установки в нулевое состояние

которого подключен к выходу первого элемента ИЛИ, вторрй вход которого объединен с тактовым входом триггера и подключен к выходу формирователя импульсов, вход генератора импульсов объединен с первым управляющим входом блока управления, третий управляющий вход которого подключен к первому выходу генератора импульсов.

0 2. Преобразователь по п. 1, о т л и ч а ющийся тем,чтОблокуправления выполнен в виде счетчика, первого и второго триггеров, элемента И и регистра сдвига, выходы которого являются группой информационных выходов блока, а информационный вход - информационным входом блока, первый вход второго триггера является первым правляющим входом блока, а второй вход объединен с первым входом первого триггера и

0 является вторым управляющим входом блока, второй вход первого триггера соединен с выходом счетчика, тактовый вход которого объединен с первым входом элемента И и является третьим управляющим входом

5 блока, второй вход элемента И объединен с управляющим входом счетчика i подключен к выходу второго триггера, третий вход элемента И соединен с инвертирующим выходом первого триггера, неинвертирующий

0 выход которого является выходом блока, выход элемента И соединен с входом записи регистра сдвига.

3. Преобразователь по п. 1, о т л и ч а ющ и и с я тем, что формирователь сигналов

5 управления выполнен в виде первого и второго счетчиков, элемента задержки и мультиплексора, информационные входы которого соединены с соответствующими выходами первого счетчика, тактовый вход

0 которого является входом формирователя сигналов управления, выход мультиплексора соединен с входом элемента задержки и является вторым выходом формирователя сигналов управления, выход элемента задержки соединен с тактовым входом второго счетчика, основные выходы которого соединены с соответствующими входами управления мультиплексора и являются группой выходов формирователя сигналов

0 управления, дополнительный выход второго счетчика - первым выходом формирователя , сигналов управления:

ЛиииЯ связи

Knpuffopy

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный цифро-аналоговый преобразователь | 1984 |

|

SU1233284A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130865A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1381506A1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Передающее устройство адаптивной телеизмерительной системы | 1989 |

|

SU1679517A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1553980A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

Изобретение относится к автоматике и может быть использовано в телеметрических системах для распределения и преобразования в аналоговые сигналы принимаемой цифровой !информации, Щель изобретения - повышение надежности результатов преобразования. Многоканальный ЦАП содержит п элементов памяти и п канальных преобразователей, блок управ- ления^ формирователь сигналов управления, генератор импульсов, а также коммутаторы, счетчики импульсов, триггеры и логические элементы. В общей части коды значений параметров преобразуются в ши- ротно-модулированные периодические импульсные последовательности так, что отношение суммарной длительности всех импульсов к периоду повторения импульсных последовательностей отображает соответствующее кодовое значение. Благодаря тому что на канальные источники тока из общего регистра одновременно выводятся одинаковые по весу кода разряды для всех каналов, существенно упрощается аппаратура индивидуальных канальных преобразователей. При этом за счет поочередной записи в регистр прямых и инверсных последовательностей в режиме тестирования без использования внешних узлов и дополнительных приборов проверяется работоспособность устройства. Представлены конкретные реализации основных блоков устройства. 2 з.п. ф-лы, 2 ил.feИзобретение относится к aBTOMaTtfKe и телемеханике, в частности к таким системам телемеханики, в которых телеметрическая информация, принимаемая из линий связи в виде кодов, должна воспроизводиться аналоговыми приборами.'^Известно многоканальное- устройство для ретрансляции сигналов, содержащее! блок приема, подключенный входом'к линии связи, а выходом - к канальным преобразователям, содержащим индивидуальные преобразователи кодов в ши- ротно-модулированные сигналы, которыезатем-преобразуются в токовые сигналы, средние значения которых соответствуют принятым кодовым сигналам.За счет промежуточного преобразования кода в широтно-модулированные сигналы достигается упрощение аппаратуры.Однако в известном устройстве не обеспечивается тестирование основных узлов и, следовательно, недостаточны надежность и достоверность приема информации.Известно также устройство для приема и воспроизведения телеизмерений, содержащее блоки приема, управления, памяти иXJО Юся юXI

К прибор у /с

| Устройство для приема и воспроизведения телеизмерений | 1986 |

|

SU1377888A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-01-30—Публикация

1989-10-19—Подача