фигЛ

Изобретение относится к импульсной технике и может использоваться в трактах деления частоты, например, в вычислительной технике, цифровых срштезаторах частот

Цель изобретения повышение быстродействия при одновременном снижении потребления энергии, за счет исключения паразитной емкости D-входа триггера и исключения вытекающего тока D-входа данного триггера путег подключения его к источнику логической 1. .

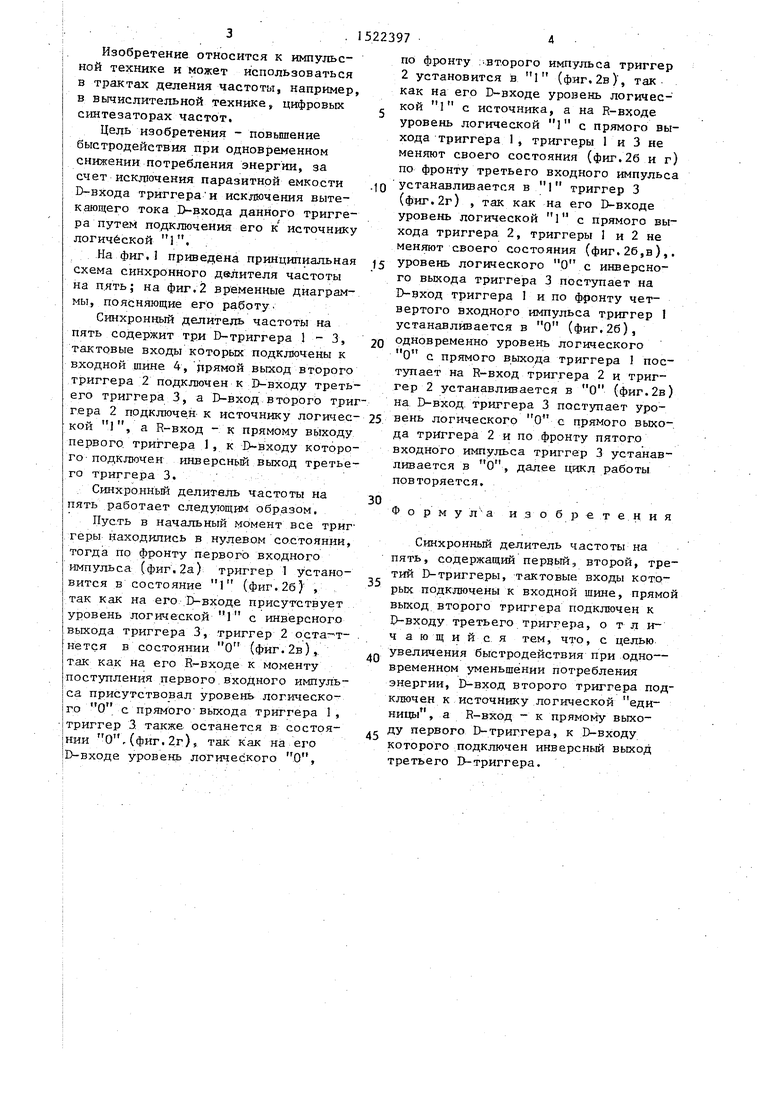

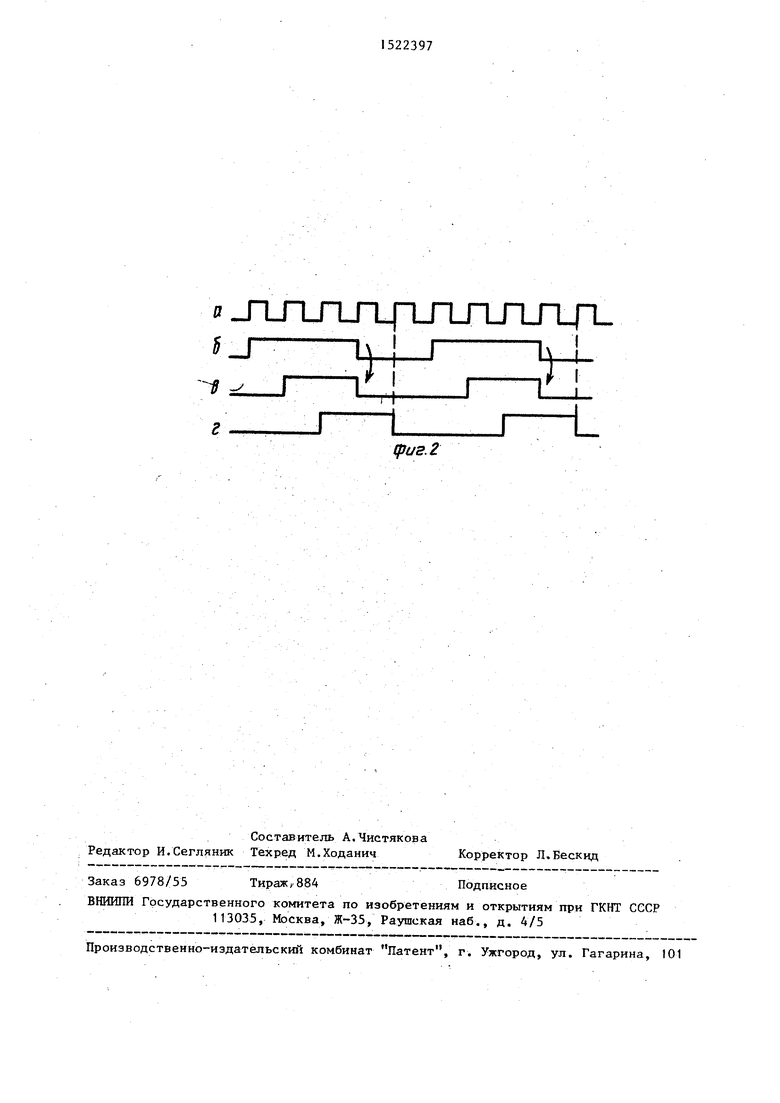

На фиг.I приведена принципиальная схема синхронного делителя частоты на п.ять; на фиг.2 временные диаграммы, поясняющие его работу.

Синхронный делителз частоты на пять содержит три D-триггера 1 - 3, тактовые входы которых подключены к входной шине 4, прямой выход второго триггера 2 подключен к D-входу третьего триггера 3, а D-вход.второго тригера 2 подключен к источнику логичес кой 1, а R-вход - к прямому выходу первого, триггера 1 , к 1 -входу которого подключен инверсньй выход третьего триггера 3,

Синхронньй делитель частоты на пять работает следзлощим образом.

Пусть в начальный момент все триг геры находютись в нулевом состоянии, тогда по фронту первого входного импульса (фиг.2а) триггер 1 установится в состояние 1 (фиг.2б) , так как на его D-входе присутствует уровень логической 1 с инверсного вьгхода триггера 3, триггер 2 оста- Т- нется в состоянии О (фиг.2в), так как на его R -входа к моменту поступления первого.входного импульса присутствовал уровень логическо- 1го О с прямого выхода триггера 1, триггер 3. также останется в состоя- |нии О,(фиг.2г)t так как на его lD-входе уровень логического О,

10

15

20

25

пО фронту : второго импульса триггер 2 установится в I (фиг. 2в), так как на его D-входе уровень логической I с источника, а на R-входе уровень логической I с прямого выхода триггера 1, триггеры I и 3 не меняют своего состояния (фиг.26 и г) по фронту третьего входного импульса устанавливается в 1 триггер 3 (фиг.2г) , так как на его D-входе уровень логической 1 с прямого выхода триггера 2, триггеры 1 и 2 не меняют своего состояния (фиг.26,в),, уровень логического О с инверсного выхода триггера 3 поступает на D-вход триггера I и по фронту четвертого входного импульса триггер 1 устанавливается в О (фиг.2б), одновременно уровень логического О с прямого выхода триггера 1 поступает на Н-вход триггера 2 и триггер 2 устанавливается в О (фиг.2в) на D-вход триггера 3 поступает уровень логического О с прямого выхода триггера 2 и по фронту пятого входного импульса триггер 3 устанавливается в О, повторяется.

далее цикл работы

Ф о р м у л а изобретения

Синхронный делитель частоты на пять, содержащий первый., второй, третий D-триггеры, тактовые входы которых подключены к входной щине, прямой выход второго триггера подключен к D-входу третьего триггера, о т л и- ч а ю щ и и с я тем, что, с целью увеличения быстродействия при одно- временном уменьшении потребления энергии, D-вход второго триггера подключен к источнику логической единицы, а Н.-вход - к прямому выходу первого D-триггера, к D-входу которого подключен инверсный выход третьего D-триггера.

а

JlJlJnJTfTJlJl

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсный частотно-фазовый детектор | 1984 |

|

SU1221710A2 |

| Синхронный делитель частоты на двенадцать | 1985 |

|

SU1298902A1 |

| Формирователь разностной частоты импульсных последовательностей | 1984 |

|

SU1265985A1 |

| Делитель частоты | 1987 |

|

SU1533001A1 |

| Кольцевой делитель частоты по модулю 2 @ -1 | 1982 |

|

SU1133665A1 |

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1124424A1 |

| Делитель частоты следования импульсов | 1985 |

|

SU1243128A1 |

| Формирователь разностной частоты импульсных последовательностей | 1985 |

|

SU1307567A1 |

| Делитель частоты следования импульсов | 1985 |

|

SU1243131A1 |

| Счетчик по модулю 5 | 1987 |

|

SU1480119A1 |

Изобретение относится к импульсной технике и может быть использовано в трактах деления частоты. Цель изобретения - повышение быстродействия при одновременном снижении потребления энергии, за счет исключения паразитной емкости D-входа триггера 2 и исключения вытекающего тока D-входа данного триггера - достигается путем подключения D-входа данного триггера к источнику логической "единицы" и образования новых функциональных связей. 2 ил.

| Делитель частоты с коэффициентом пересчета 2 -1 | 1979 |

|

SU784007A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-11-15—Публикация

1987-11-16—Подача