ВихоЗ

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство аналого-цифрового преобразования | 1987 |

|

SU1559405A2 |

| Устройство автоматической гамма-коррекции телевизионного сигнала | 1986 |

|

SU1345375A1 |

| КОГЕРЕНТНЫЙ АВТОКОМПЕНСАТОР ПОМЕХ ДЛЯ МНОГОКАНАЛЬНЫХ ИМПУЛЬСНО-ДОПЛЕРОВСКИХ БОРТОВЫХ РАДИОЛОКАЦИОННЫХ СТАНЦИЙ | 2008 |

|

RU2374661C1 |

| Устройство аналого-цифрового преобразования | 1988 |

|

SU1501268A2 |

| Цифровой корректор временных искажений телевизионных сигналов системы СЕКАМ для видеомагнитофонов | 1984 |

|

SU1277428A1 |

| Устройство компенсации сигнала дефектов киноленты | 1987 |

|

SU1494247A1 |

| Устройство для бинарного квантования телевизионного видеосигнала | 1983 |

|

SU1129745A1 |

| Устройство коррекции телевизионного сигнала | 1988 |

|

SU1628224A1 |

| Устройство для приема дискретной информации | 1987 |

|

SU1501298A1 |

| Линейное устройство коррекции межсимвольной интерференции | 1984 |

|

SU1256213A1 |

Изобретение относится к технике связи. Цель изобретения - повышение точности компенсации. Устройство содержит АЦП 1, перемножители 2, 4 и 7, формирователь 3 корректирующего сигнала, сумматор 5, запоминающее устройство 6 на строку, а также синхрогенератор 8 и блок управления 9. Цель достигается введением перемножителей 4 и 7 и сумматора 5, с помощью которых происходит накопление сигнала коррекции от строки к строке, увеличивающее отношение сигнал/шум. 2 ил.

Ipufl

Изобретение относится к промьш - ленности средств связи и может быть использовано при построении устройств Koj-шенсации сигнала неравномерности освещенности и чувствительности однострочных приборов с зарядовой связью (ПЭС) в телекинопроекционных системах

Целью изобретения является повышение -ТОЧНОСТИ компенсации.

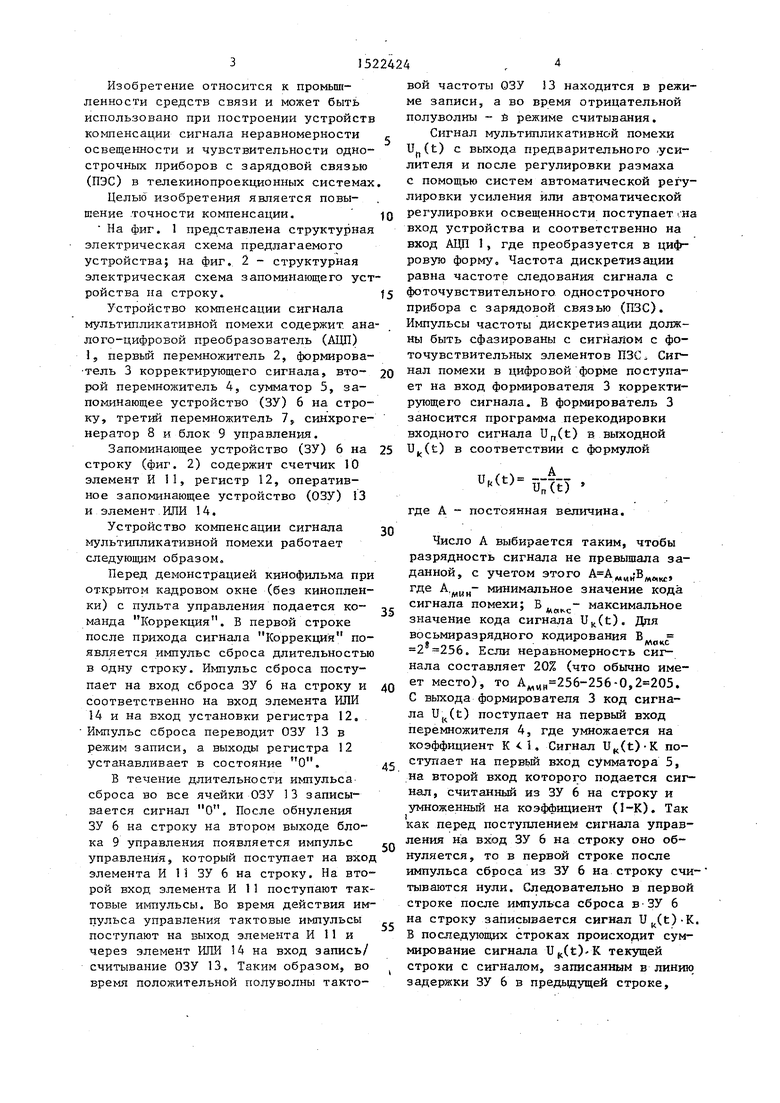

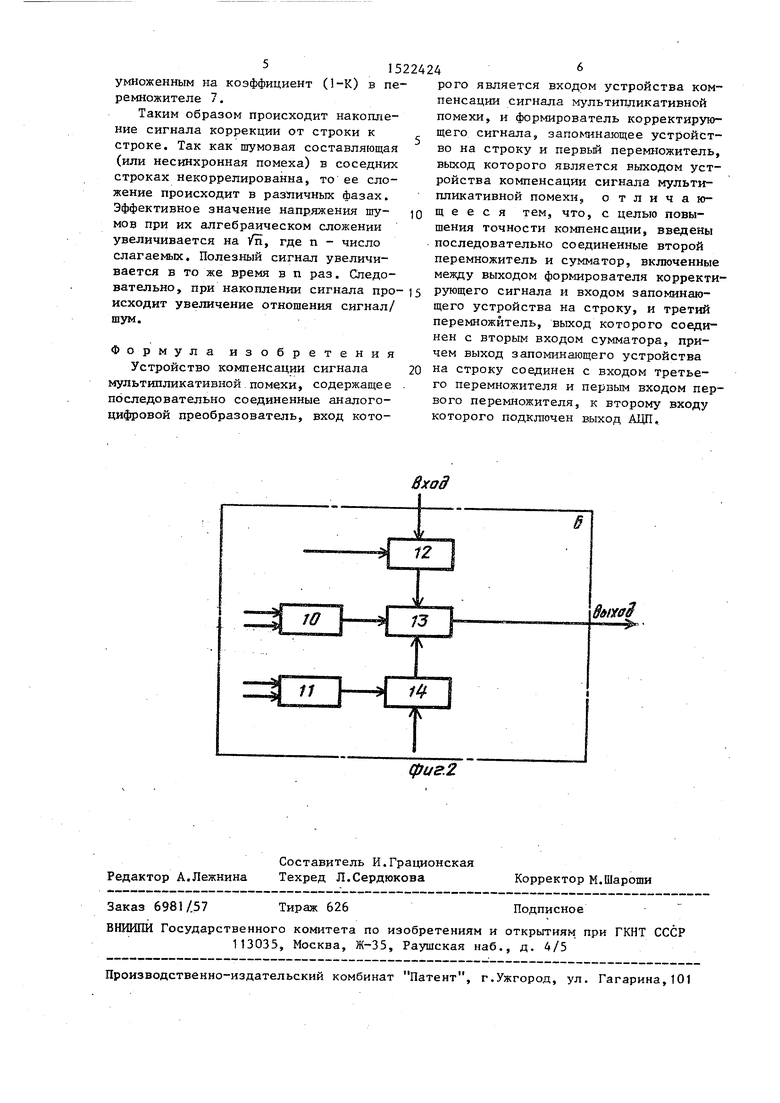

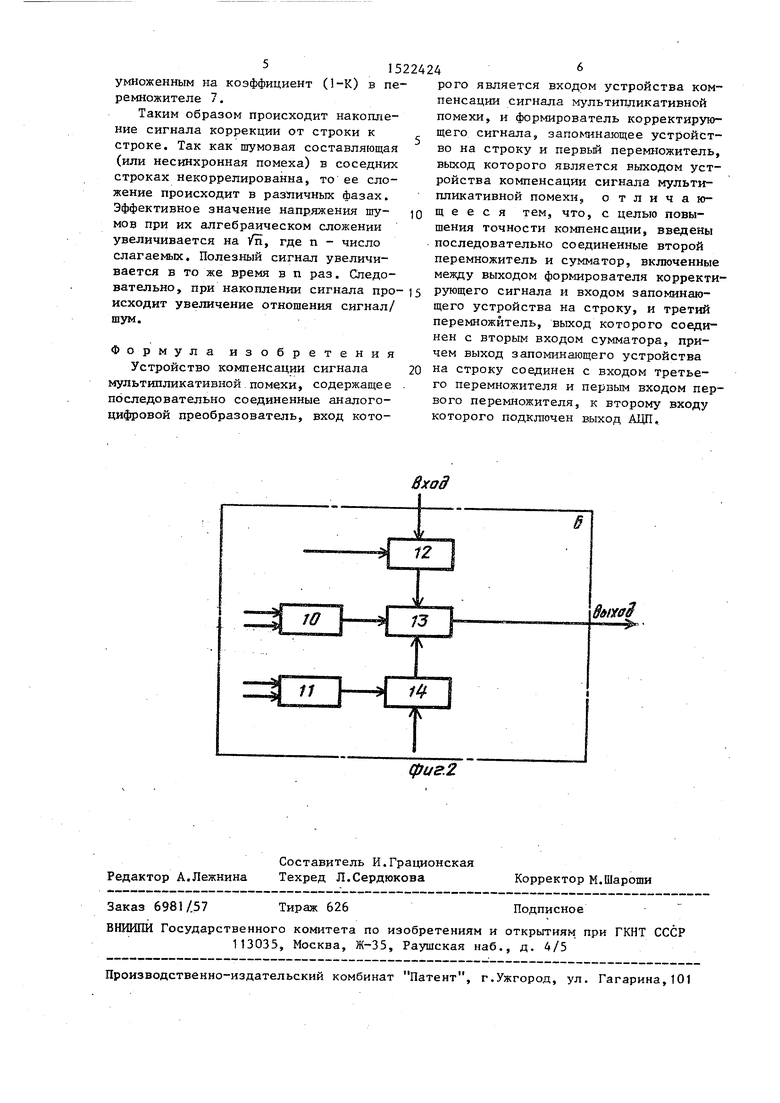

На фиг. 1 представлена структурная электрическая схема предлагаемого устройства; на фиг, 2 - структурная электрическая схема запоминающего устройства па строку.

Устройство компенсации сигнала мультипликативной помехи содержит, аналого-цифровой преобразователь (АЦП) , первый перемножитель 2, формирова- тель 3 корректирующего сигнала, второй перемножитель 4, сумматор 5, запоминающее устройство (ЗУ) 6 на строку, третий перемножитель 7, синкроге- нератор 8 и блок 9 управления.

Запоминающее устройство (ЗУ) 6 на строку (фиг. 2) содержит счетчик 10 элемент И 11, регистр 12, оперативное запоминающее устройство (ОЗУ) 13 и элемент ИЛИ 14.

Устройство компенсации сигнала мультипликативной помехи работает следующим образом.

Перед демонстрацией кинофильма при открытом кадровом окне (без кинопленки) с пульта управления подается команда Коррекция. В первой строке после прихода сигнала Коррекция появляется импульс сброса длительностью в одну строку. Импульс сброса поступает на вход сброса ЗУ 6 на строку и соответственно на вход элемента ИЛИ 14 и на вход установки регистра 12. Импульс сброса переводит ОЗУ 13 в режим записи, а выходы регистра 12 устанавливает в состояние О.

В течение длительности импульса- сброса во все ячейки ОЗУ 13 записывается сигнал О. После обнуления ЗУ 6 на строку на втором выходе блока 9 управления появляется импульс управления, который поступает на вхо элемента И 11 ЗУ 6 на строку. На второй вход элемента И 11 поступают тактовые импульсы. Во время действия импульса управления тактовые импульсы поступают на выход элемента И 11 и через элемент ИЛИ 14 на вход запись/ считывание ОЗУ 13, Таким образом, во время положительной полуволны такто

вой частоты ОЗУ 3 находится в режиме записи, а во время отрицательной полуволны - и режиме считывания.

Сигнал мультипликативной помехи U(t) с выхода предварительного усилителя и после регулировки размаха с помощью систем автоматической регулировки усиления или автоматической регулировки освещенности поступает она вход устройства и соответственно на вход АЦП 1, где преобразуется в цифровую форму. Частота дискретизации равна частоте следования сигнала с фоточувствительного однострочного прибора с зарядовой связью (ПЗС). Импульсы частоты дискретизации должны быть сфазированы с сигналом с фоточувствительных элементов ПЗС Сигнал помехи в цифровой форме поступает на вход формирователя 3 корректирующего сигнала. В формирователь 3 заносится программа перекодировки входного сигнала Ur,(t) а выходной U(t) в соответствии с формулой

0

5

0

5

0

U.(t)

U,(t) где А - постоянная вел1 Гчина.

Число А выбирается таким, чтобы разрядность сигнала не превышала заданной, с учетом этого А Ам„„-В,

да - минкода

мпкс максимальное

минимальное значение сигнала помехи;

значение кода сигнала U(t). Для восьмиразрядного кодирования В 2 256. Если неравномерность сигнала составляет 20% (что обычно имеет место), то А „„ 256-256-0,.

С вьпсода формирователя 3 код сигнала Uj(t) поступает на первый вход перемножителя 4, где умножается на коэффициент К 1, Сигнал U(t)-K поступает на первый вход сумматора 5, на второй вход которого подается сигнал, считанный из ЗУ 6 на строку и зшноженньш на коэффициент (1-К). Так как перед поступлением сигнала управления на вход ЗУ 6 на строку оно обнуляется, то в первой строке после импульса сброса из ЗУ 6 на строку счи- тываются нули. Следовательно в первой строке после импульса сброса в ЗУ 6 на строку записывается сигнал U(t)-K. В последующих строках происходит суммирование сигнала U(t) K текущей строки с сигналом, записанным в линию задержки ЗУ 6 в предьвдущей строке.

умноженным на коэффициент (1-К) в перемножителе 7.

Таким образом происходит накопление сигнала коррекции от строки к строке. Так как шумовая составляющая (или несинхронная помеха) в соседних строках некоррелированна, то ее сложение происходит в различных фазах. Эффективное значение напряжения ту- мов при их алгебраическом сложении увеличивается на fa., где п - число слагаемых. Полезный сигнал увеличивается в то же время в п раз. Следовательно, при накоплении сигнала происходит увеличение отношения сигнал/ шум.

Формула изобретения

Устройство компенсации сигнала мультипликативной помехи, содержащее последовательно соединенные аналого- цифровой преобразователь, вход кото си-ч

рого является входом устройства компенсации сигнала мультипликативной помехи, и формирователь корректирующего сигнала, зaпo шнaющee устройство на строку и первьй перемножитель, вькод которого является выходом устройства компенсации сигнала мультипликативной помехи, о т л и ч а ю- щ е е с я тем, что, с целью повышения точности компенсации, введены последовательно соединенные второй перемножитель и сумматор, включенные между выходом формирователя корректирующего сигнала и входом запоминающего устройства на строку, и третий перемножйтель, выход которого соединен с вторым входом сумматора, причем выход запоминающего устройства на строку соединен с входом третьего перемножителя и первым входом первого перемножителя, к второму входу которого подключен выход АВД,

12

;j

1

| Документация ССД COLO TE/ECINE, FDL-60 service manul, sufion 4, фиг.6. |

Авторы

Даты

1989-11-15—Публикация

1987-07-13—Подача