(54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный преобразователь напряжения в код | 1977 |

|

SU677099A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1524178A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1589395A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1983 |

|

SU1130856A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU945978A1 |

| Устройство аналого-цифрового преобразования | 1979 |

|

SU773926A1 |

| ТАНКОВЫЙ БАЛЛИСТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 1987 |

|

RU2226715C2 |

| Аналого-цифровой преобразователь | 1980 |

|

SU884127A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1320901A1 |

| Устройство для регистрации сигналов | 1982 |

|

SU1278741A1 |

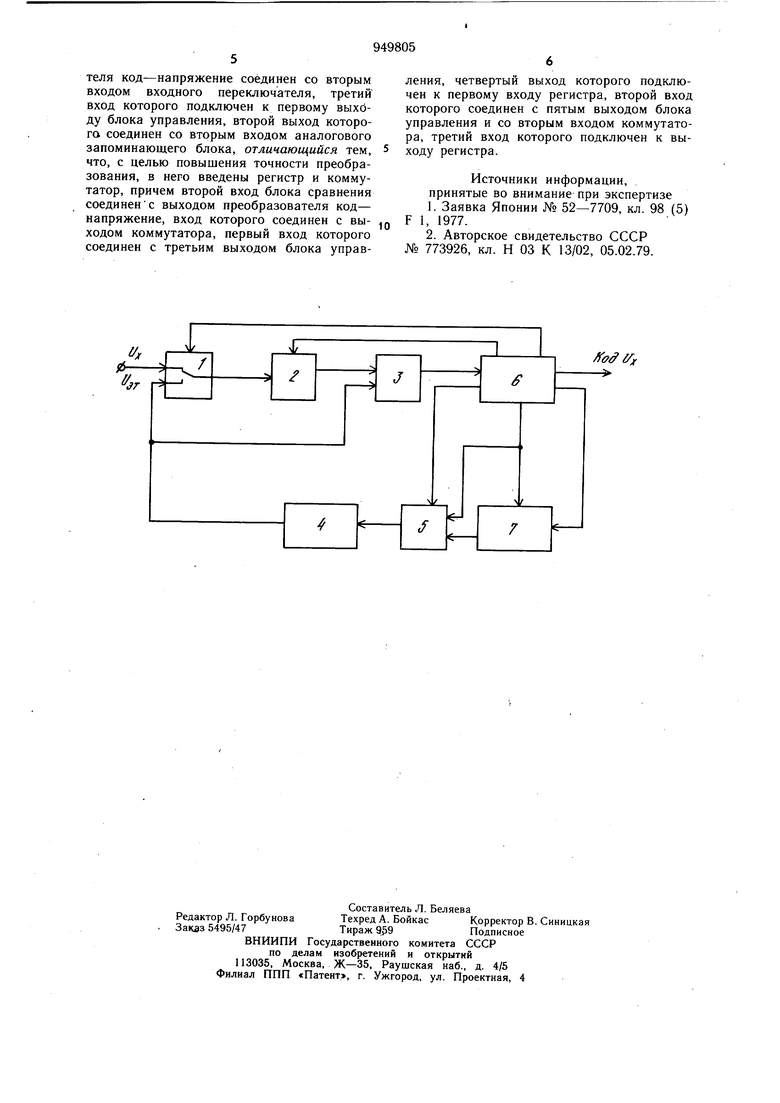

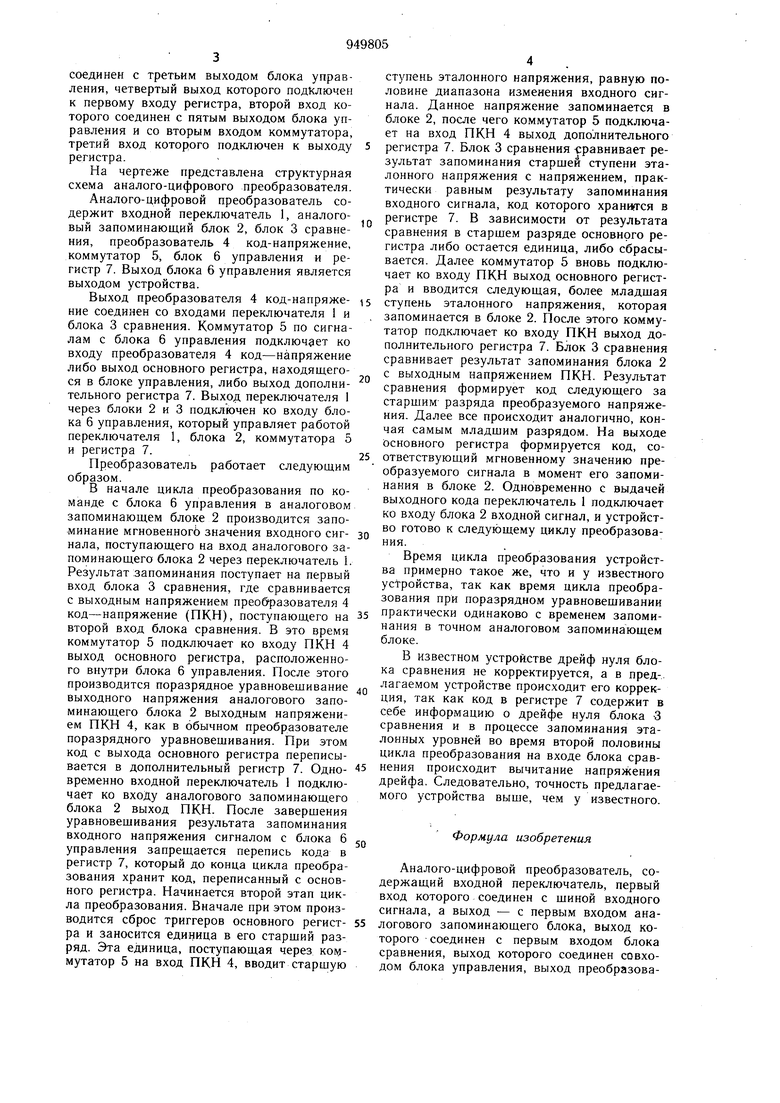

Изобретение относится к электроизмерительной и вычислительной технике, а также к системам передачи информации. Известен аналого-цифровой преобразователь, погрешность буферного блока которого корректируется не полностью, а импульсная помеха, возникающая при его выключении, полностью входит в погрешность преобразователя, т.е. эталонное напряжение не запоминается в нем 1. Известно также устройство аналого-цифрового преобразования, содержащее входной переключатель, первый вход которого соединен с шиной входного сигнала, второй вход через цифроаналоговый преобразователь соединен с первым выходом блока управления, а третий вход - со вторым выходом блока управления, вход которого соединен с выходом блока сравнения, первый вход первого аналогового запоминающего блока соединен с выходом входного переключателя, второй вход - с третьим выходом блока управления, а выход соединен с первым входом второго аналогового запоминающего блока и с первым входом блока сравнения, второй вход которого соединен с выходом второго аналогового запоминающего блока, второй вход которого соединен с четвертым выходом блока управления 2. Недостатком известного устройства является то, что дрейф нуля сравнивающего блока полным весом входит в погрешность преобразования. Цель изобретения - повышение точности преобразования. Поставленная цель достигается тем, что в аналого-цифровой преобразователь, содержащий входной переключатель, первый вход которого соединен с шиной входного сигнала, а выход - с первым входом аналогового запоминающегоблока, выход которого соединен с первым входом блока сравнения, выход которого соединен со входом блока управления, выход преобразователя код-напряжение соединен со вторым входом входного переключателя, третий вход которого подключен к первому выходу блока управления, второй выход которого соединен со вторым входом аналогового запоминающего блока, введены регистр и коммутатор, причем второй вход блока сравнения соединен с выходом преобразователя код - напряжение, вход которого соединен с выходом коммутатора, первый вход которого соединен с третьим выходом блока управления, четвертый выход которого подключен к первому входу регистра, второй вход которого соединен с пятым выходом блока управления и со вторым входом коммутатора, третий вход которого подключен к выходу регистра. На чертеже представлена структурная схема аналого-цифрового преобразователя. Аналого-цифровой преобразователь содержит входной переключатель 1, аналоговый запоминающий блок 2, блок 3 сравнения, преобразователь 4 код-напряжение, коммутатор 5, блок б управления и регистр 7. Выход блока 6 управления является выходом устройства. Выход преобразователя 4 код-напряжение соединен со входами переключателя 1 и блока 3 сравнения. Коммутатор 5 по сигналам с блока 6 управления подключает ко входу преобразователя 4 код-напряжение либо выход основного регистра, находящегося в блоке управления, либо выход дополнительного регистра 7. Выход переключателя 1 через блоки 2 и 3 подключен ко входу блока 6 управления, который управляет работой переключателя 1, блока 2, коммутатора 5 и регистра 7. Преобразователь работает следующим образом. В начале цикла преобразования по команде с блока 6 управления в аналоговом запоминающем блоке 2 производится запоминание мгновенногб значения входного сигнала, поступающего на вход аналогового запоминающего блока 2 через переключатель 1. Результат запоминания поступает на первый вход блока 3 сравнения, где сравнивается с выходным напряжением преобразователя 4 код-напряжение (ПКН), поступающего на второй вход блока сравнения. В это время коммутатор 5 подключает ко входу ПКН 4 выход основного регистра, расположенного внутри блока б управления. После этого производится поразрядное уравновещивание выходного напряжения аналогового запоминающего блока 2 выходным напряжением ПКН 4, как в обычном преобразователе поразрядного уравновещивания. При этом код с выхода основного регистра переписывается в дополнительный регистр 7. Одновременно входной переключатель 1 подключает ко входу аналогового запоминающего блока 2 выход ПКН. После завершения уравновещивания результата запоминания входного напряжения сигналом с блока б управления запрещается перепись кода в регистр 7, который до конца цикла преобразования хранит код, переписанный с основного регистра. Начинается второй этап цикла преобразования. Вначале при этом производится сброс триггеров основного регистра и заносится единица в его старщий разряд. Эта единица, поступающая через коммутатор 5 на вход ПКН 4, вводит старшую ступень эталонного напряжения, равную половине диапазона изменения входного сигнала. Данное напряжение запоминается в блоке 2, после чего коммутатор 5 подключает на вход ПКН 4 выход дополнительного регистра 7. Блок 3 сравнения сравнивает результат запоминания старшей ступени эталонного напряжения с напряжением, практически равным результату запоминания входного сигнала, код которого храндася в регистре 7. В зависимости от результата сравнения в старщем разряде основного регистра либо остается единица, либо сбрасывается. Далее коммутатор 5 вновь подключает ко входу ПКН выход основного регистра и вводится следующая, более младщая ступень эталонного напряжения, которая запоминается в блоке 2. После этого коммутатор подключает ко входу ПКН выход дополнительного регистра 7. Блок 3 сравнения сравнивает результат запоминания блока 2 с выходным напряжением ПКН. Результат сравнения формирует код следующего за старщим разряда преобразуемого напряжения. Далее все происходит аналогично, кончая самым младшим разрядом. На выходе основного регистра формируется код, соответствующий мгновенному значению преобразуемого сигнала в момент его запоминания в блоке 2. Одновременно с выдачей выходного кода переключатель 1 подключает ко входу блока 2 входной сигнал, и устройство готово к следующему циклу преобразования. Время цикла преобразования устройства примерно такое же, что и у известного устройства, так как время цикла преобразования при поразрядном уравновещивании практически одинаково с временем запоминания в точном аналоговом запоминающем блоке. В известном устройстве дрейф нуля блока сравнения не корректируется, а в пред-. лагаемом устройстве происходит его коррекция, так как код в регистре 7 содержит в себе информацию о дрейфе нуля блока -3 сравнения и в процессе запоминания эталонных уровней во время второй половины цикла преобразования на входе блока сравнения происходит вычитание напряжения дрейфа. Следовательно, точность предлагаемого устройства выше, чем у известного. Формула изобретения Аналого-цифровой преобразователь, содержащий входной переключатель, первый вход которого соединен с шиной входного сигнала, а выход - с первым входом аналогового запоминающего блока, выход которого соединен с первым входом блока сравнения, выход которого соединен совходом блока управления, выход преобразователя код-напряжение соединен со вторым входом входного переключателя, третий вход которого подключен к первому выходу блока управления, второй выход которого соединен со вторым входом аналогового запоминающего блока, отличающийся тем, что, с целью повышения точности преобразования, в него введены регистр и коммутатор, причем второй вход блока сравнения соединенс выходом преобразователя код- напряжение, вход которого соединен с выходом коммутатора, первый вход которого соединен с третьим выходом блока управления, четвертый выход которого подключен к первому входу регистра, второй вход которого соединен с пятым выходом блока управления и со вторым входом коммутатора, третий вход которого подключен к выходу регистра.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-08-07—Публикация

1980-04-14—Подача