1

(21)4164324/24-09

(22)18.12.87

(46) 23.11.89. Бнш. № 43

(72) И.М.Котиков и О.Н.Порохов

(53) 621.394.662(088.8)

(56) Авторское свидетельство СССР

№ 1341726, кл. Н 04 J 3/06, 1983.

(54) УСТРОЙСТВО КОДОВОЙ СИНХРОНИЗАЦИИ

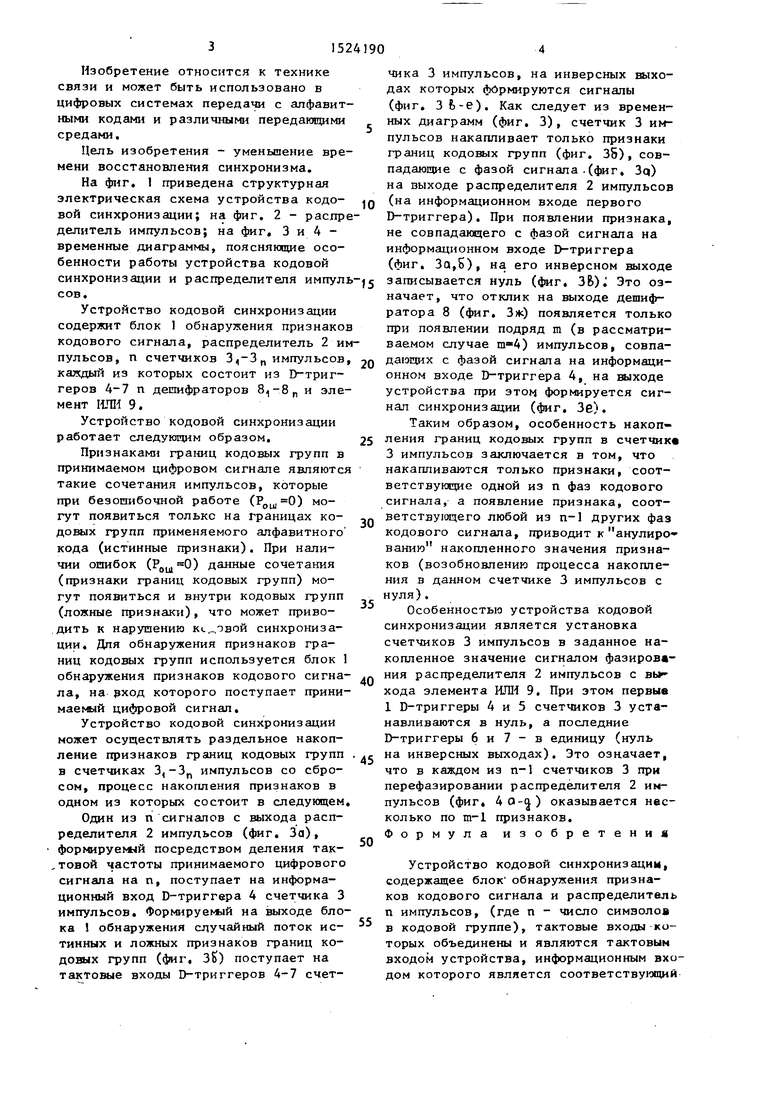

(-57) Изобретение относится к технике связи и может быть использовано в цифровых системах передачи с алфавитными кодами и различными передающими средами. Цель изобретения - уменьшение времени восстановления синхронизма. Устройство содержит блок 1 обнаружения признаков кодового сигнала, распределитель 2 импульсов, п счетчиков 3,-3пимпульсов, каждый из которых состоит из D-триггеров 4-7, п дешифраторов 8,-8„, В устройство введен элемент ИЛИ 9, включенный между выходами дешифраторов 8 п-1.иепей и управляющим входом распределителя 2. Для обнаружения признаков границ кодовых групп используется блок 1, на вход которого поступает принимаемый цифровой сигнал. Основной особенностью устройства является осуществление раздельного накопления признаков границ кодовых групп в счетчиках импульсов со сбросом. Второй особенностью устройства является установка счетчиков 3 в заданное накопленное значение сигналом фазирования распределителя 2 с выхода элемента ИЛИ .9. 4 ил.

с «

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство блочной синхронизации | 1983 |

|

SU1341726A1 |

| Цифровая радиорелейная система передачи | 1987 |

|

SU1478357A1 |

| Устройство кодовой синхронизации | 1985 |

|

SU1328941A1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С МЯГКИМИ РЕШЕНИЯМИ | 2010 |

|

RU2428801C1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С ИНТЕГРИРОВАННЫМИ МЯГКИМИ И ЖЕСТКИМИ РЕШЕНИЯМИ | 2011 |

|

RU2450464C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| Устройство цикловой синхронизации | 1981 |

|

SU949832A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ НА ОСНОВЕ МАТРИЧНОЙ ОБРАБОТКИ КАНОНИЧЕСКОЙ РЕКУРРЕНТНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ, СФОРМИРОВАННОЙ МОДУЛЬНЫМ ГЕНЕРАТОРОМ | 2024 |

|

RU2831303C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОДОВЫХ КОМБИНАЦИЙ | 1992 |

|

RU2129338C1 |

Изобретение относится к технике связи и может быть использовано в цифровых системах передачи с алфавитными кодами и различными передающими средами. Цель изобретения - уменьшение времени восстановления синхронизма. Устройство содержит блок 1 обнаружения признаков кодового сигнала, распределитель 2 импульсов, N счетчиков 31-3N импульсов, каждый из которых состоит из D-триггеров 4-7, N дешифраторов 81-8N. В устройство введен элемент ИЛИ 9, включенный между выходами дешифраторов 8 N-1 цепей и управляющим входом распределителя 2. Для обнаружения признаков границ кодовых групп используется блок 1, на вход которого поступает принимаемый цифровой сигнал. Основной особенностью устройства является осуществление раздельного накопления признаков границ кодовых групп в счетчиках 31-3N импульсов со сбросом. Второй особенностью устройства является установка счетчиков 3 в заданное накопленное значение сигналом фазирования распределителя 2 с выхода элемента ИЛИ 9. 4 ил.

Фи.1

Изобретение относится к технике связи и может быть использовано в цифровых системах передачи с алфавитными кодами и различными передающими средами.

Цель изобретения - уменьшение времени восстановления синхронизма.

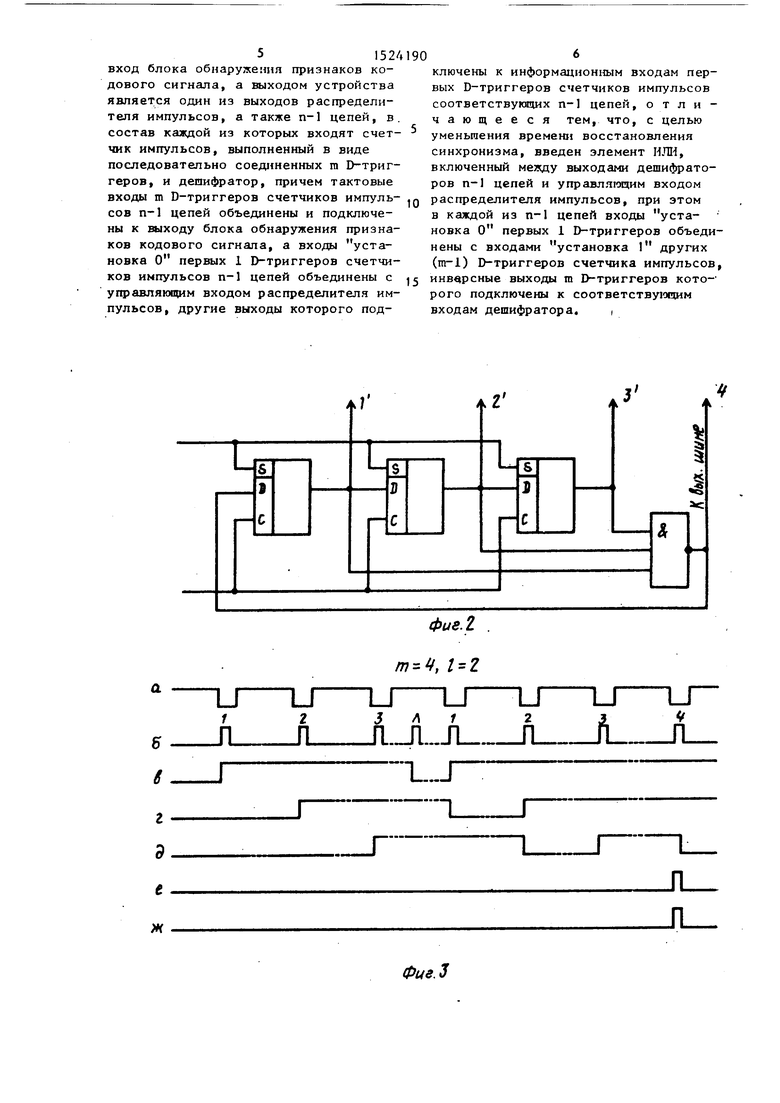

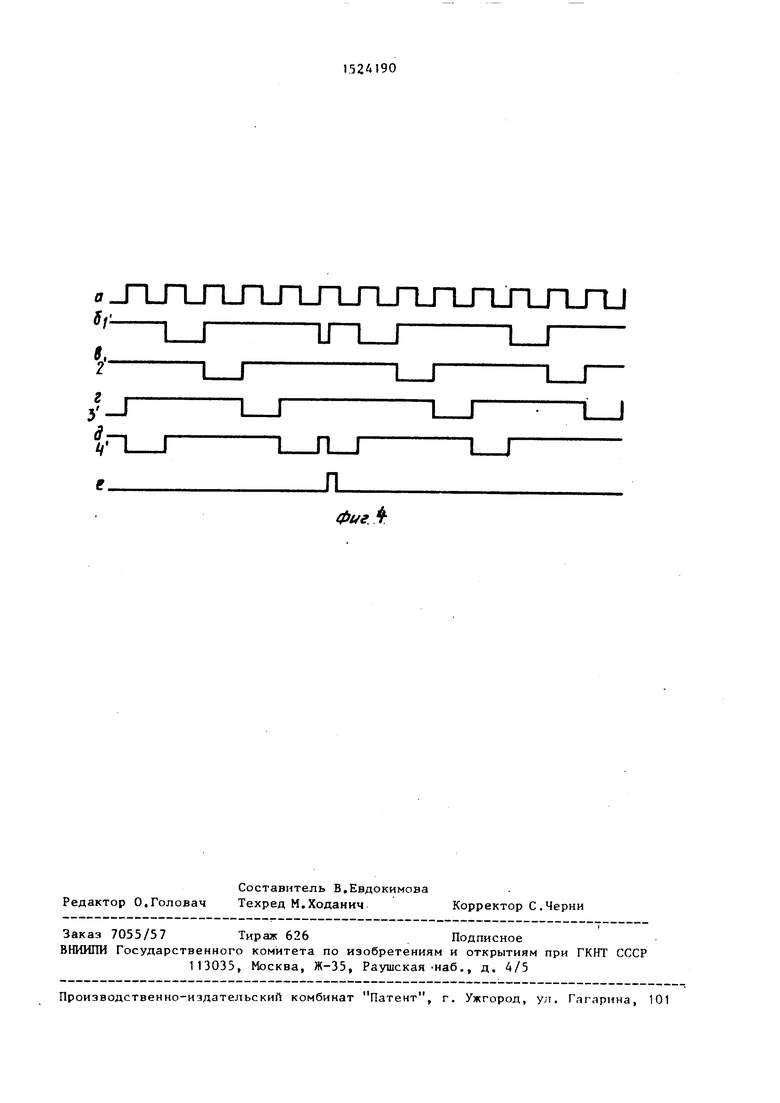

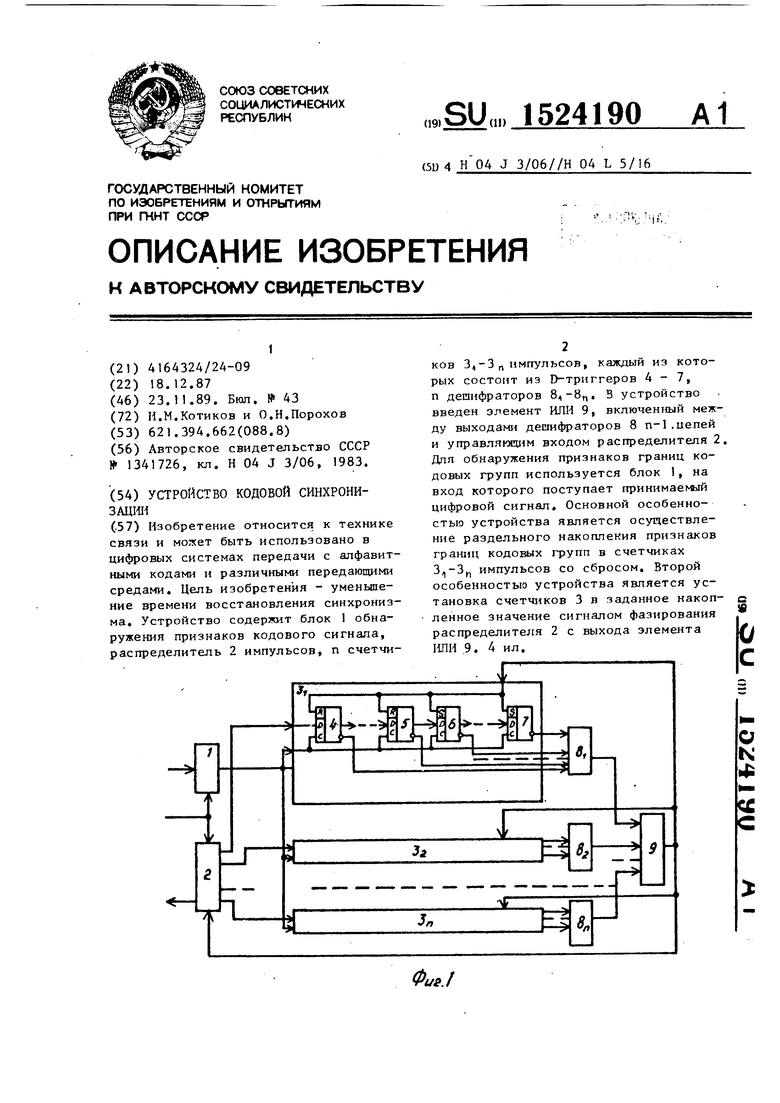

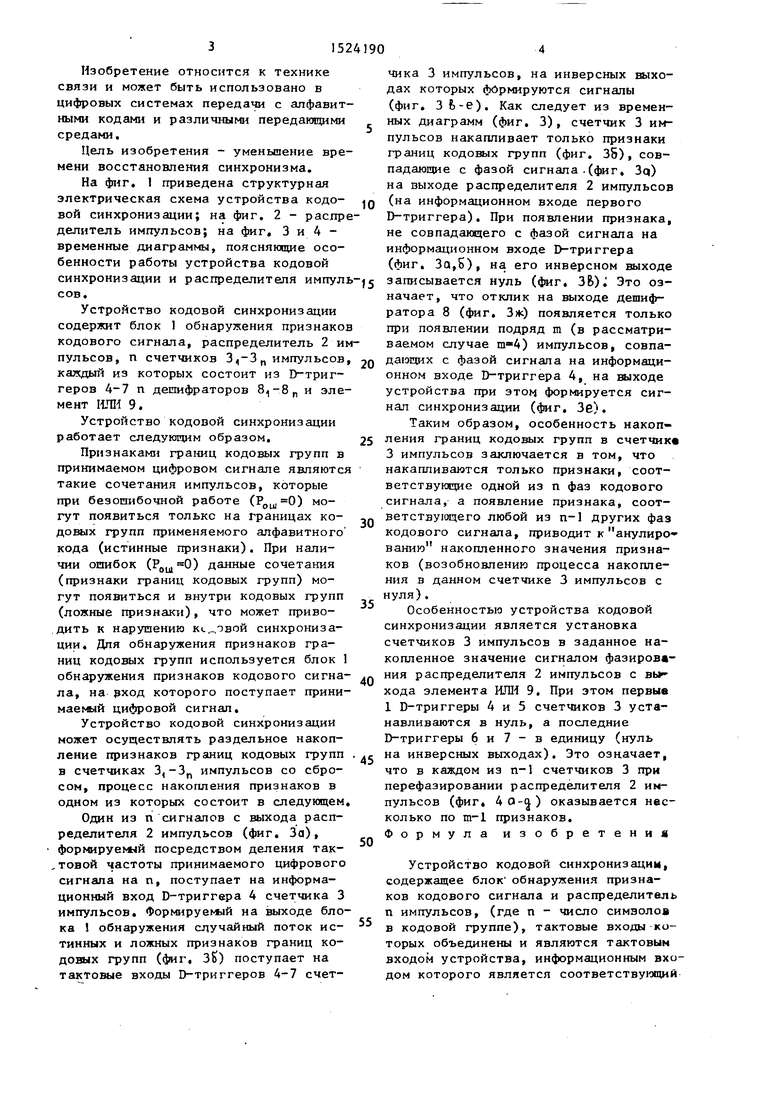

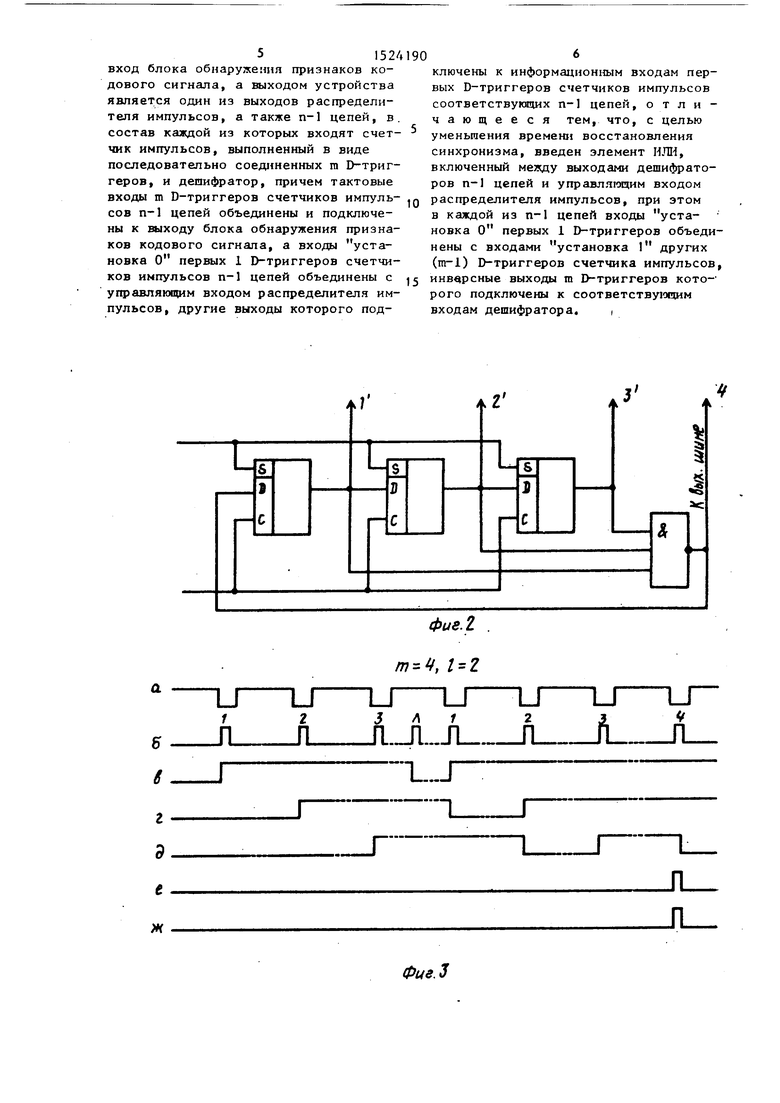

На фиг, 1 приведена структурная электрическая схема устройства кодо- вой синхронизации; на фиг. 2 - распределитель импульсов; на фиг, 3 и 4 - временные диаграммы, поясняющие особенности работы устройства кодовой синхронизации и распределителя импуль сов.

Устройство кодовой синхронизации содержит блок 1 обнаружения признаков кодового сигнала, распределитель 2 импульсов, п счетчиков 3,-3 „ импульсов, калдьш из которых состоит из D-триг- геров 4-7 п дешифраторов 8,-8 и элемент И-ТИ 9,

Устройство кодовой синхронизации работает следующим образом.

Признаками границ кодовых групп в принимаемом цифровом сигнале являются такие сочетания импульсов, которые при безошибочной работе (Роц,0) могут появиться только на границах ко

довых групп применяемого алфавитного кода (истинные признаки). При наличии ошибок () данные сочетания (признаки границ кодовых групп) могут появиться и внутри кодовых групп (ложные признаки), что может приво.дить к нарушению К1.,-,овой синхронизации. Для обнаружения признаков границ кодовых групп используется блок 1 обнаружения признаков кодового сигна- ла, на эход которого поступает прини- мае1«лй цифровой сигнал.

Устройство кодовой синхронизации может осуществлять раздельное накопление признаков границ кодовых групп в счетчиках 3,-3 импульсов со сбросом, процесс накопления признаков в одном из которых состоит в следующем

Один из п сигналов с выхода распределителя 2 импульсов (фиг. За)f формируемой посредством деления так,ТОБОЙ частоты принимаемого цифрового сигнгша на п, поступает на информационный вход D-триггера 4 счетчика 3 импульсов. Формируемой на выходе блока 1 обнаружения случайный поток ис тинных и ложных признаков границ кодовых групп (фиг, 3S) поступает на тактовые входы D-триггеров 4-7 счет

,

Q

0

5

0

Q

,

0

5

чика 3 импульсов, на инверсных выходах которых формируются сигналы (фиг, 3 fe-e). Как следует из временных диаграмм (фиг, 3), счетчик 3 импульсов накапливает только признаки границ кодовых групп (фиг. 35), совпадающие с фазой сигнала .(фиг, 3q) на выходе распределителя 2 импульсов (на информационном входе первого D-триггера). При появлении признака, не совпадающего с фазой сигнала на информационном входе D-триггера (фиг. 3a,S), на его инверсном выходе записывается нуль (фиг, ЗЬ) Это означает, что отклик на выходе дешифратора 8 (фиг, появляется только при появлении подряд m (в рассматриваемом случае ) импульсов, совпадающих с фазой сигнала на информационном входе D-триггера 4, на выходе устройства при этом формируется сигнал синхронизации (фиг, Зе).

Таким образом, особенность накопления границ кодовых групп в счетчик 3 импульсов заключается в том, что накапливаются только признаки, соответствующие одной из п фаз кодового сигнала, а появление признака, соответствующего любой из п-1 других фаз кодового сигнала, приводит к анулиро ванига накопленного значения признаков (возобновлению процесса накоппе- ния в данном счетчике 3 импульсов с нуля).

Особенностью устройства кодовой синхронизации является установка счетчиков 3 импульсов в заданное накопленное значение сигналом фазирования распределителя 2 импульсов с вы хода элемента liJIM 9. При этом первые 1 D-триггеры 4 и 5 счетчиков 3 устанавливаются в нуль, а последние D-триггеры 6 и 7 - в единицу (нуль на инверсных выходах). Это означает, что в каждом из п-1 счетчиков 3 при перефазировании распределителя 2 импульсов (фиг, 4о-) оказывается несколько по т-1 признаков. Формула изобретении

Устройство кодовой синхронизации, содержащее блок обнаружения признаков кодового сигнала и распределитель п импульсов, (где п - число символов в кодовой группе), тактовые входы которых объединены и являются тактовым входом устройства, информационным входом которого является соответству101ций

51524

вход блока обнаружения признаков кодового сигнала, а выходом устройства является один из выходов распределителя импульсов, а также п-1 цепей, в. состав каждой из которых входят счетчик импульсов, выполненный в виде последовательно соединенных га D-триг- геров, и дешифратор, причем тактовые входы m D-триггеров счетчиков импульсов п-1 цепей объединены и подключены к выходу блока обнаружения признаков кодового сигнала, а входы установка О первых 1 D-триггеров счетчиков импульсов п-1 цепей объединены с управлякмцим входом распределителя импульсов, другие выходы которого подж

6

ключены к информационным входам первых D-триггеров счетчиков импульсов соответствующих п-1 цепей, отличающееся тем, что, с целью уменьшения времени восстановления синхронизма, введен элемент ИЛИ, включенный между выходами дешифраторов п-1 цепей и управляющим входом

распределителя импульсов, при этом в каждой из п-1 цепей входы установка О первых 1 D-триггеров объединены с входами установка 1 других (m-i) D-триггеров счетчика импульсов,

инверсные выходы m D-триггеров которого подключены к соответствуюршм входам дешифратора. i

ж2

J

L

Фи8.2 .

,

JL

Фие.З

а JlJHJlJlJnjlJlJTJnjarLrLnJ LJU-1 J

в.

2

l-TLJ П

Фиг

Авторы

Даты

1989-11-23—Публикация

1987-12-18—Подача