(Л

с

СП

ts: ел

СП) ;0 СО

до

:тигается за счет введения реверсивного счетчика 9, дешифраторов 10, 111 элементов И 12, 13, сумматора 14

по модулю два, К-1 коммутаторов 6, К-1 сдвиговьпс регистров 7. 2 ил., 2 табл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| Генератор квазирегулярных последовательностей импульсов | 1979 |

|

SU866717A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1437907A1 |

| Генератор квазирегулярных импульсов | 1980 |

|

SU890547A1 |

| Устройство для приема дискретной информации | 1987 |

|

SU1501298A1 |

| Генератор псевдослучайной М-последовательности | 1985 |

|

SU1264317A2 |

| Устройство для ортогонального преобразования цифровых сигналов по функциям Хаара | 1983 |

|

SU1116435A1 |

| Дифференцирующе-сглаживающее устройство | 1975 |

|

SU610115A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| Устройство поиска шумоподобного сигнала | 1988 |

|

SU1540020A1 |

Изобретение относится к устройствам, генерирующим ортогональные многозначные кодовые последовательности, и предназначено для расширения класса решаемых задач за счет возможности построения кодов, составляющих ортогональную матрицу с символами из множества вычетов по простому нечетному модулю. Цель изобретения - расширение класса решаемых задач за счет способности генерирования многозначных ортогональных кодовых последовательностей. Устройство содержит первый 1 и второй 2 генераторы М - последовательности, дешифратор 3, одновибратор 4, элемент И 5, группу из К коммутаторов 6, группу из К сдвиговых регистров 7, делитель 8 частоты, реверсивный счетчик 9, дешифраторы 10, 11, элементы И 12, 13, сумматор 14 по модулю два. Цель достигается за счет введения реверсивного счетчика 9, дешифраторов 10, 11, элементов И 12, 13, сумматора 14 по модулю два, К-1 коммутаторов 6, К-1 сдвиговых регистров 7. 2 ил., 2 табл.

Изобретение относится к устройст- вам, формирующим системы ортогональные сигналов, и может быть использо- варо в системах связи.

Цель изобретения - расширение класса решаемых задач за счет обес- печения способности генерирования многозначных ортогональных кодовых последовательностей.

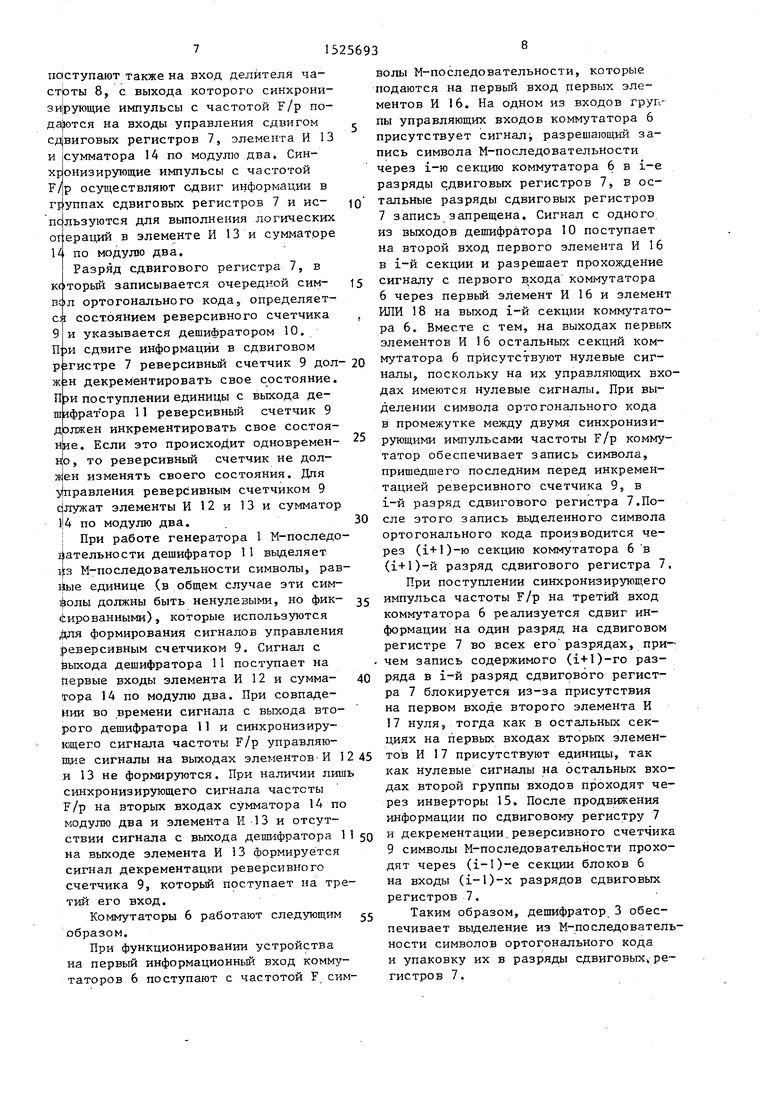

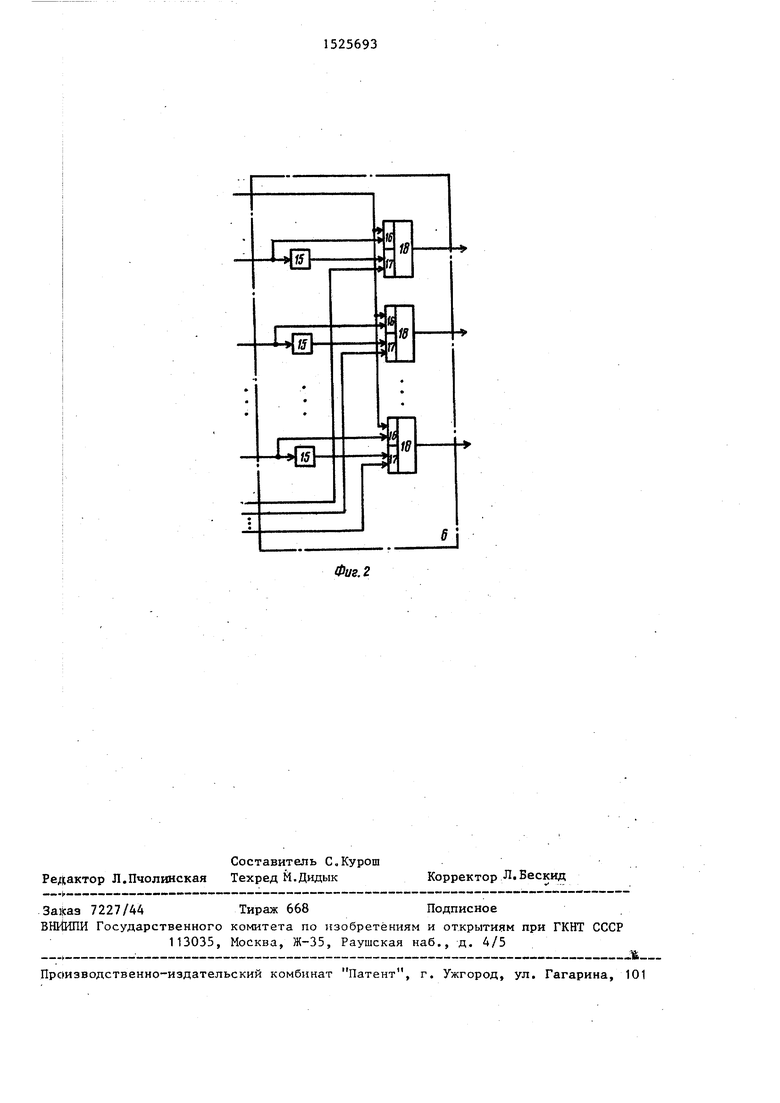

На фиг, 1 представлена структурна схЬма устройства; на фиг, 2 - струк- тузная схема коммутатора.

Генератор ортогональных кодов со- деЬжит первьй 1 и второй 2 генераторы 3,

М-последовательности,, дешифратор одновибратор 4, элемент И 5,

25

13

гр1шпу из к коммутаторов 6, группу из К сдвиговых регистров 7, делитель 8 частоты, реверсивный счетчик 9, депифраторы 10 и 11, элементы И 12 и

и сумматор 14 по модулю два.

Коммутатор 6 может состоять из группы инверторов 15 .и соответствующих этим инверторам групп спаренных элементов И 16 и 17, каждой паре которых соответствует элемент ИЛИ 18,

Устройство работает следующим об- рг(зом.

В исходном состоянии разряды ге- нб(раторов 1 и 2 через первый и втоi .

рс1й входы начальной загрузки устройства занесены р-ичныё коды для гене- раттии идентичных М-последовательнос- тей, а также установлено начальное состояние реверсивного счетчика 9 че р4з третий вход начальной загрузки устройства, обеспечивающее упаковку вьйеленньж символов строк матрицы бе пропусков и наложений в сдвиговый регистр.

Работа устройства начинается с по на вход синхронизации устройств синхронизирующих импульсов, откуда ойи поступгиот на вход делителя 8 и взЮд управления сдвигом сдвиговых регистров 7 и через элемент И 5 проходят на управляюц ие входы генераторов 1 и 2 М-последовательности, при на выходах генераторов 1 и 2

0

0

5

0

5

0

5

порождаются р-ичные М-последовательности,

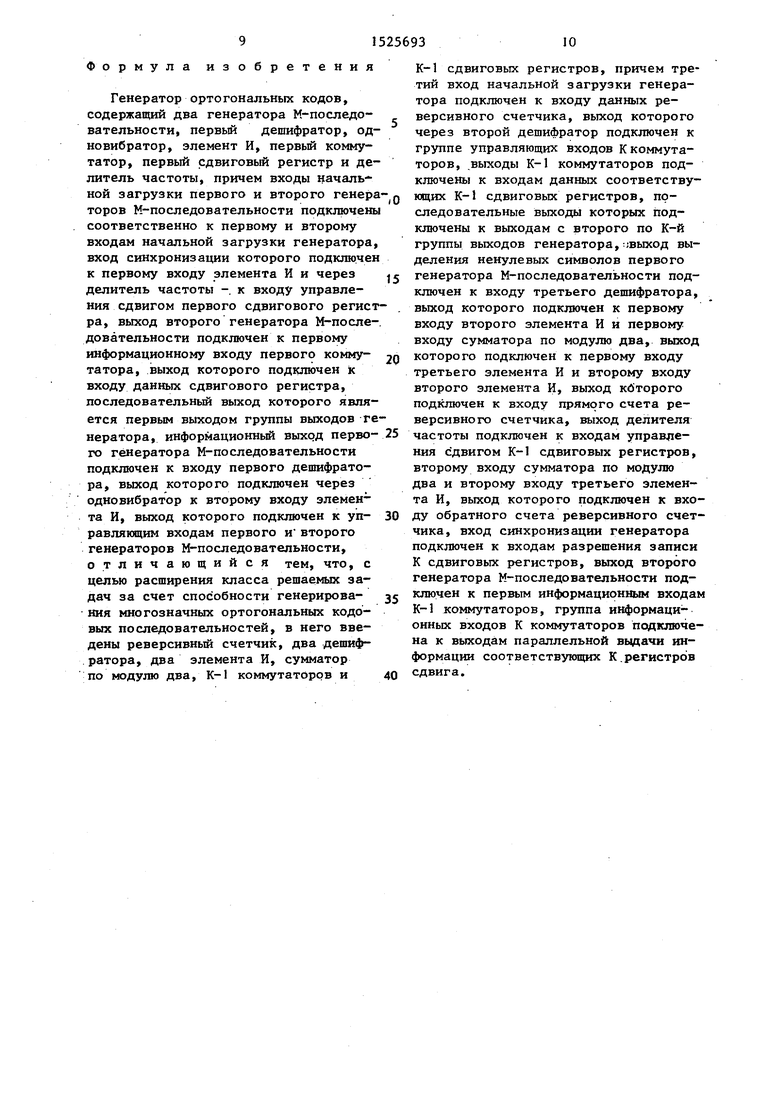

Так, ДJJЯ многочлена третьей степени X ® X ® 2, где Ф означает сумму по модулю три, образуется М-последо- вательность 10020212210222001012112011, Из этой М-последовательности, посту- . пающей с первого выхода первого генератора 1 М-последовательности, с помощью дешифратора 11 выделяются единичные символы 11 - 11-1-1111, которые используются как для управления реверсивным счетчиком 9,, так и для выделения символов ортогонального кода из М-последовательности, генерируемой генератором 2. Пусть с выхода генератора 2 М-последовательности следует циклический сдвиг М-последовательности 021221022200101211201 И 002. Тогда из нее должны быть выделены символы, которые состоят из тех же порядковых номеров, что и единицы в М-последовательности, порождаемой

генератором 1, т.е, О-г-0-2 1-211-02, и упакованы в сдвиговом регистре 7 в код 002121102, символы которого должны быть выданы с выхода устройства с частотой F/p.

Аналогично должно происходить вы- . деление и символов.других строк матрицы из циклических сдвигов М-последовательности, что представлено (в табл, 1 и 2),

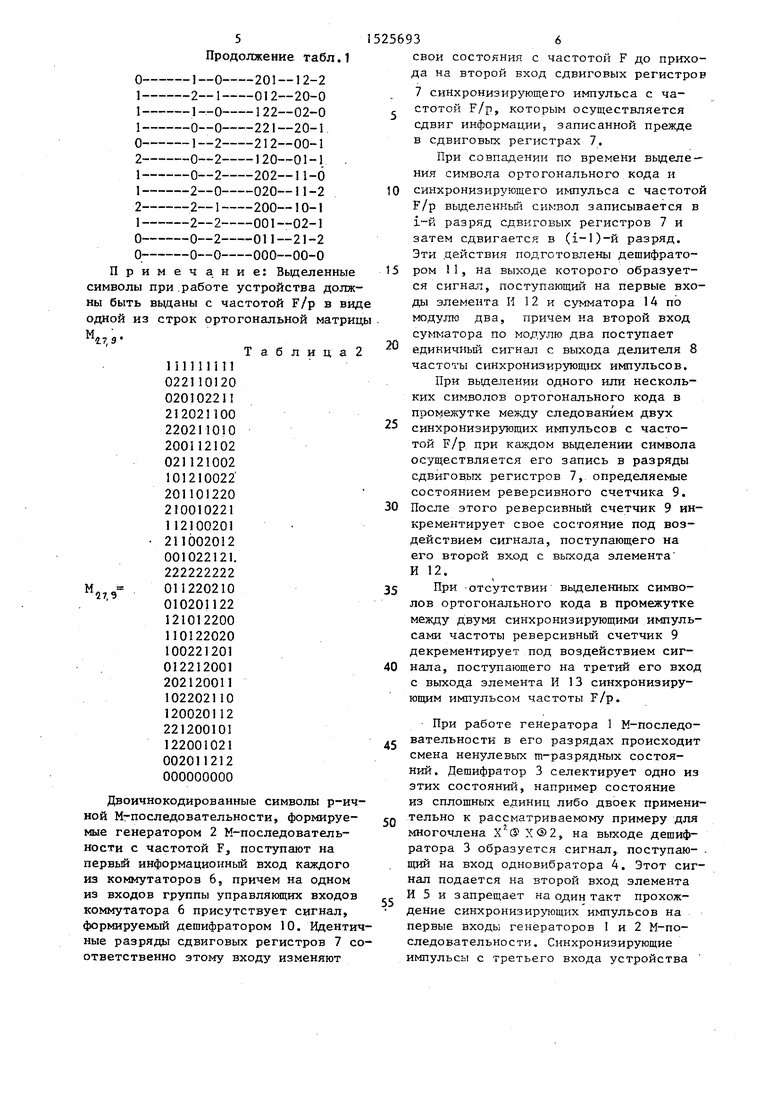

Таблица 11 - 1111 - 11-1

О2-2-110-12-0

О2-О--102-21-1

21 2--021-10 6

22-0 -211-01-6

2о-О1Г2--16-2 .

О2-1--121-00-2

1о- 1210-02-2

20-1101-22-0

2-1-0010-22-1

1 2100-20-1

2-1 - 1-002-01-2

М о-0-1022-12-1

,9 22-2222-22-2

О1 - 1-220-21-0,

Продолжение табл.1

О1-0201 - 12-2

2-1012-20-0

11 о122-02-0

IО-О221-20-1.

О1-2212-00-1

20-2120-01-1 .

10-2202-11-6

12-0020-11-2

22- 1200- 10-1

12-2001 -02-1

О0-2011-21-2

ОО-О000-00-0

Примечание: Вьщелейные имволы при .работе устройства должы быть вьщаны с частотой F/p в виде дной из строк ортогональной матрицы

7,Э.

Т а б Л И Ц а 2 111111111 022110120 020102211 212021100 220211010 200112102 021121002 101210022 201101220 210010221 112100201 211002012 001022121. 222222222

М

27,9

011220210 010201122 121012200 110122020 100221201 012212001 202120011 102202110 120020112 221200101 122001021 002011212 000000000

Двоичнокодированные символы р-ич ной М-последовательности, формируемые генератором 2 М-последовательности с частотой F, поступают на первьй информационньй вход каждого из коммутаторов 6, причем на одном из входов группы управляющих входов коммутатора 6 присутствует сигнал, формируемый дешифратором 10. Идентиные разряды сдвиговых регистров 7 сответственно этому входу изменяют

256936

свои состояния с частотой F до прихода на второй вход сдвиговых регистров

7 синхронизирующего импульса с ча- стотой F./P, которым осуществляется сдвиг информации, записанной прежде в сдвиговых регистрах 7.

При совпадении по времени выделения символа ортогонального кода и

10 синхронизирующего и шульса с частотой F/P выделенньй символ записывается в разряд сдвиговых регистров 7 и затем сдвигается в (1-1)-й разряд. Эти .действия подготовлены дешифрато15 ром И, на выходе которого образуется сигнал, поступающий на первые входы элемента Н 12 и сумматора 14 по модулю два, причем на второй вход сум атора по модулю два поступает

единичный сигнал с выхода делителя 8 частоты синхронизирующих импульсов.

При выделении одного или нескольких символов ортогонального кода в промежутке между следованием двух

25 синхронизирующих импульсов с частотой F/P при каждом выделении символа осуществляется его запись в разряды сдвиговых регистров 7, определяемые состоянием реверсивного счетчика 9.

30 После этого реверсивный счетчик 9 ин- крементирует свое состояние под воздействием сигнала, поступающего на его второй вход с выхода элемента И 12.

35 При отсутствии выделенньш символов ортогонального кода в промежутке между двумя синхронизирующими импульсами частоты реверсивный счетчик 9 декрементирует под воздействием сиг40 нала, поступающего на третий его вход с выхода элемента И 13 синхронизирующим импульсом частоты F/p.

При работе генератора 1 М-последо- дс вательности в его разрядах происходит смена ненулевых т-разрядных состояний. Дешифратор 3 селектирует одно из этих состояний, например состояние из сплошных единиц либо двоек примени- CQ тельно к рассматриваемому примеру для многочлена Х®2, на выходе дешифратора 3 образуется сигнал, поступаю- . щий на вход одновибратора 4. Этот сигнал подается на второй вход элемента И 5 и запрещает на один такт прохождение синхронизирующих иьшульсов на первые входы генераторов 1 и 2 М-последовательности. Синхронизирующие импульсы с третьего входа устройства

поступают также на вход делителя ча- стрты 8, с выхода которого синхрони- зи|рующие импульсы с частотой F/p по- на входы управления сдвигом сд{виговых регистров 7, элемента И 13 и сумматора 14 по модулю два. Синхронизирующие импульсы с частотой F/P осуществляют сдвиг информации в группах сдвиговых регистров 7 и ис- пользуются для выполнения логических огераций в элементе И 13 и сумматоре 14 по модулю два.

Разряд сдвигового регистра 7, в кс торый записывается очередной сим- ВС1Л ортогонального кода, определяется состоянием реверсивного счетчика 9 и указывается дешифратором 10. П;эи сдвиге информации в сдвиговом р ггистре 7 реверсивньй счетчик 9 дол- жгн декрементировать свое состояние. При поступлении единицы с выхода де- шнфрат ора 11 реверсивный счетчик 9 дЬлжен инкрементировать свое состоя- н|ие. Если это происходит одновремен- , то реверсивный счетчик не дол- jKJeH изменять своего состояния. Для у|правления реверсивным счетчиком 9 с|лужат элементы И 12 и 13 и сумматор 114 по модулю два.

При работе генератора 1 М-последо х ательнссти дешифратор 11 вьоделяет М-последовательности символы, рав 1|1ые единице .(в общем случае эти сим- фолы должны быть ненулевыми, но фик- (Ьированными), которые используются |щя формирования сигналов управления реверсивным счетчиком 9. Сигнал с выхода дешифратора 11 поступает на Первые входы элемента И 12 и сумма- tropa 14 по модулю два. При совпадении во времени сигнала с выхода второго дешифратора 11 и синхронизирующего сигнала частоты F/p управляющие сигналы на выходах элементов И 1 и 13 не формируются. При наличии лиш синхронизирующего сигнала частоты F/P на вторых входах сумматора 14 по модулю два и элемента И -13 и отсутствии сигнала с выхода дешифратора 1 на выходе элемента И 13 формируется сигнал декрементащш реверсивного счетчика 9, которьй поступает на третий его вход.

Коммутаторы 6 работают следующим образом.

При функционировании устройства на первый информационный вход комку- таторов 6 поступают с частотой F сим5

5 , 0 0

5 0 45 50

55

волы М-последовательности, которые подаются на первый вход первых элементов И 16. На одном из входов группы управляющих входов коммутатора 6 присутствует сигналу разрешающий запись символа М-последовательности через i-ю секцию коммутатора 6 в i-e разряды сдвиговых регистров 7, в остальные разряды сдвиговых регистров 7 запись запрещена. Сигнал с одного из выходов дешифратора 10 поступает на второй вход первого элемента И 16 в i-й секции и разрешает прохождение сигналу с первого выхода коммутатора 6 через первьй элемент И 16 и элемент ИЛИ 18 на выход i-й секции коммутатора 6. Вместе с тем, на выходах первых элементов И 16 остальных секций коммутатора 6 присутствуют нулевые сигналы, поскольку на их управляющих входах имеются нулевые сигналы. При выделении символа ортогонального кода в промежутке между двумя синхронизирующими импульсами частоты F/p коммутатор обеспечивает запись символа, пришедшего последним перед инкремен- тацией реверсивного счетчика 9, в i-й разряд сдвигового регистра 7.После этого запись выделенного символа ортогонального кода производится через (i+l)-ю секцию коммутатора 6 в (i+l)-й разряд сдвигового регистра 7,

При поступлении синхронизирующего импульса частоты F/p на третий вход коммутатора 6 реализуется сдвиг информации на один разряд на сдвиговом регистре 7 во всех его разрядах, причем запись содержимого (i+l)-ro разряда в i-й разряд сдвигового регистра 7 блокируется из-за присутствия на первом входе второго элемента И 17 нуля, тогда как в остальных секциях на первых входах вторых элементов И 17 присутствуют единшда, так как нулевые сигналы на остальных входах второй группы входов проходят через инверторы 15. После продвижения информации по сдвиговому регистру 7 и декрементации.реверсивного счетчика 9 символы М-последовательности проходят через (i-l)-e секции блоков 6 на входы (i-l)-x разрядов сдвиговых регистров 7.

Таким образом, дешифратор 3 обеспечивает выделение из М-последовательности символов ортогонального кода и упаковку их в разряды сдвиговых.регистров 7.

Формула изобретения

Генератор ортогональных кодов, содержащий два генератора М-последо- вательности, первый дешифратор, одно вибратор, элемент И, первый коммутатор, первый сдвиговый регистр и делитель частоты, причем входы начальной загрузки первого и второго генера торов М-последовательности подключены соответственно к первому и второму входам начальной загрузки генератора, вход синхронизации которого подключен к первому входу элемента И и через делитель частоты -. к входу управления сдвигом первого сдвигового регистра, выход второго генератора М-последовательности подключен к первому информационному входу первого комму- татора, выход которого подключен к входу данных сдвигового регистра, последовательный выход которого является первым выходом группы выходов генератора, информационньй выход перво- го генератора М-последовательности подключен к входу первого дешифратора, выход которого подключен через одновибратор к второму входу элемента И, выход которого подключен к уп- равляющим входам первого и второго генераторов М-последовательности, отличающийся тем, что, с целью расширения класса решаемых задач за счет способности генерирова- ния многозначных ортогональных кодовых последовательностей, в него введены реверсивный счетчик, два дешифратора, два элемента И, сумматор по модулю два, К-1 коммутаторов и

К-1 сдвиговых регистров, причем третий вход начальной загрузки генератора подключен к входу данных реверсивного счетчика, выход которого через второй дешифратор подключен к группе управляющих входов К коммутаторов, выходы К-1 коммутаторов подключены к входам данных соответствующих К-1 сдвиговых регистров, последовательные выходы которых подключены к выходам с второго по К-й группы выходов генератора, :;выход выделения ненулевых символов первого генератора М-последовательности подключен к входу третьего дешифратора, выход которого подключен к первому входу второго элемента И и первому входу сумматора по модулю два, выход которого подключен к первому входу третьего элемента И и второму входу второго элемента И, выход кбторого подключен к входу прямого счета реверсивного счетчика, выход делителя частоты подключен к входам управле ния сдвигом К-1 сдвиговых регистров, второму входу сумматора по модулю два и второму входу третьего элемента И, выход которого подключен к входу обратного счета реверсивного счетчика, вход синхронизации генератора подключен к входам разрешения записи К сдвиговых регистров, выход второго генератора М-последовательности подключен к первым информационным входа К-1 коммутаторов, группа информационных входов К коммутаторов подключена к выходам параллельной вцдачи информации соответствующих К.регистров сдвига.

| Генератор последовательности р-чисел Фибоначчи | 1986 |

|

SU1324019A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ БИОРТОГОНАЛЬНЫХКОДОВ | 1971 |

|

SU425368A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| , | |||

Авторы

Даты

1989-11-30—Публикация

1987-12-01—Подача