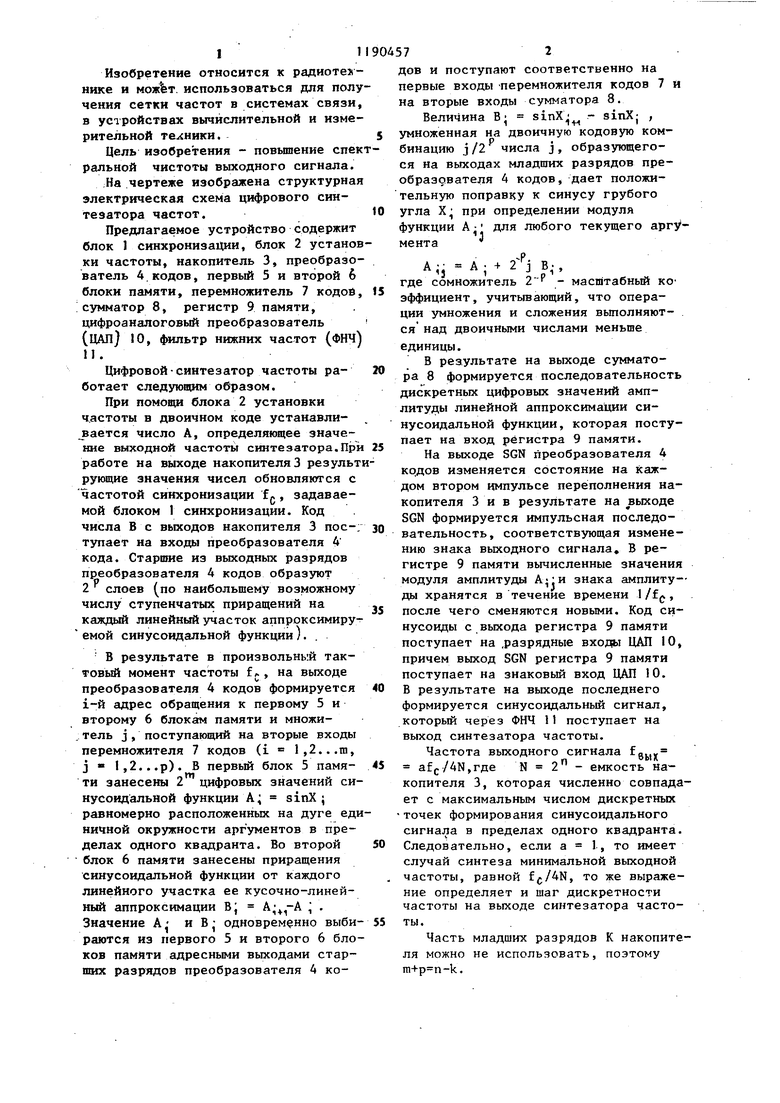

Изобретение относится к радиотех нике и . использоваться для пол чения сетки частот в системах связи в устройствах вычислительной и изме рительной техники. Цель изобретения - повышение спе ральной чистоты выходного сигнала. На чертеже изображена структурна электрическая схема цифрового синтезатора частот. Предлагаемое устройство содержит блок 1 синхронизации, блок 2 устано ки частоты, накопитель 3, преобразо ватель 4 кодов, первый 5 и второй 6 блоки памяти, перемножитель 7 кодой ;сумматор 8, регистр 9 памяти, цифроаналоговый преобразователь (ЦАП) 10, фильтр нижних частот (ФНЧ П. Цифровой-синтезатор частоты работает следующим образом. При помощи блока 2 установки ч.астоты в двоичном коде устанавли ается число А, определяющее значение выходной частоты синтезатора.Пр работе на выходе накопителя 3 результ рующие значения чисел обновляются с частотой синхронизации f, задаваемой блоком 1 синхронизации. Код числа В с выходов накопителя 3 посTjmaeT на входы преобразователя 4 кода. Старшие из выходных разрядов преобразователя Д кодов образуют 2 слоев (по наибольшему возможному числу ступенчатых приращений на каждый линейный участок аппроксимируемой синусоидальной функции). . В результате в произвольный тактовый момент частоты f, на выходе преобразователя 4 кодов формируется i-й адрес обращения к первому 5 и второму 6 блокам памяти и множи. тель j, поступающий на вторые входы перемножителя 7 кодов (i l,2...m, j I,2...p). В первый блок 5 памяти занесетл 2 цифровых значений синусоидальной функции А; sinX ; равномерно расположенных на дуге еди ничной окружности аргументов в пределах одного квадранта. Во второй блок 6 памяти занесены приращения синусоидальной функции от каждого линейного участка ее кусочно-линейный аппроксимации В| ; . Значение А и В одновременно выбираются из первого 5 и второго 6 блоков памяти адресными выходами старших разрядов преобразователя 4 кодов и поступают соответственно на первые входы перемножителя кодов 7 на вторые входы сумматора 8. sinX - sinXj Величина В; умноженная на двоичную кодовую комбинацию j /2 числа j , образующегося на выходах младщих разрядов преобразователя 4 кодов, дает положительную поправку к синусу грубого угла X; при определении модуля функции А для любого текущего аргументаА- А;. 2 В., где сомножитель - масштабный ко эффициент, учитывающий, что операции умножения и сложения вьшолняют- . ся над двоичными числами меньше единицы. В результате на выходе сумматора 8 формируется последовательность дискретных цифровых значений амплитуды линейной аппроксимации синусоидальной функции, которая поступает на вход регистра 9 памяти. На выходе SGN преобразователя 4 кодов изменяется состояние на каждом втором импульсе переполнения накопителя 3 и в результате на ыходе SGN формируется импульсная последовательность, соответствующая изменению знака выходного сигнала, В регистре 9 памяти вычисленные значения модуля амплитуды А-:и знака амплиту-ды хранятся в течение времени 1 /(%, после чего сменяются новыми. Код синусоиды с выхода регистра 9 памяти поступает на .разрядные входы ЦАП 10, причем выход SGN регистра 9 памяти поступает на знаковый вход ЦАП 10. В результате на выходе последнего формируется синусоидальный сигнал, который через ФНЧ П поступает на выход синтезатора частоты. Частота выходного сигнала Еду af(./4N,гдe N 2 - емкость накопителя 3, которая численно совпадает с максимальным числом дискретных точек формирования синусоидального сигнала в пределах одного квадранта. Следовательно, если а 1, то имеет случай синтеза минимальной выходной частоты, равной ff/4N, то же выражение определяет и шаг дискретности частоты на выходе синтезатора частоты. Часть младших разрядов К накопителя можно не использовать, поэтому . Максимальная погрешность отклонения каждого линейного участка (из 2 возможных от синусоиды в пределах одного квадранта выражается зависимостью. Д1- sin 0,5(х,-., o,5(sin Xj. + sinXp Л1 8in(X; + -jW,)- 0,(x;+ -|йтг) sinX; . Наибольшее значение максимальной погрешности u макс. на линейном учас ке при Э/2 и определяется из выражения - JRf Лмакс. - cos - :;-3-(l-cos ) Значение погрешности & макс, зави сит только от числа линейных участко .на четверть периода и например, при ш 5 (32 линейных участка & макс. 0,00031, что соответствует одиннадцати точным разрядам вьписления значений синусоиды. В реальных синтез.аторах частот погрешность вычисления синусоиды дополнительно увеличивается за счет ограничения разрядной сетки входящих в него блоков, поэтому в предлагаемом устройстве при m 5 (3,8) достига;ется 10 (6,1б) точных разрядов вычисления синусоиды, а в известном всего лишь 7 (5,10) точных разрядов . В предлагаемом цифровом синтезаторе частот точность вычисления синусоиды возрастает на два двоичных разряда, при увеличении ш на единицу. За счет линейной аппроксимации синусоиды, как огибающей, на которой расположены дискретные значения функции A,j (в результате образуется обобщенная линейно-ступенчатая аппроксимация), по сравнению с известным устройством при одних и тех же аппаратурных затратах, существенно повышается спектральная чистота (точность цифрового вычисления синусоиды) выходного сигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор частоты | 1986 |

|

SU1374398A2 |

| Цифровой синтезатор частот | 1979 |

|

SU813677A1 |

| Цифровой синтезатор частот | 1978 |

|

SU813675A1 |

| Цифровой синтезатор частоты | 1987 |

|

SU1429285A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 1991 |

|

RU2020728C1 |

| Цифровой синтезатор частот | 1984 |

|

SU1210198A1 |

| Цифровой генератор периодических функций | 1987 |

|

SU1441372A1 |

| Цифровой синтезатор изменяющейся частоты | 1988 |

|

SU1525861A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ФАЗОМОДУЛИРОВАННЫХ СИГНАЛОВ | 2001 |

|

RU2204196C2 |

| ЦИФРОВОЙ СИНТЕЗАТОР ИЗМЕНЯЮЩЕЙСЯ ЧАСТОТЫ | 2021 |

|

RU2765264C1 |

ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ, содержащий последовательно соединенные блок установки частоты, накопитель и преобразователь кодов, выходы старших разрядов которого подключены к соответствующим адресным входам первого и второго блоков памяти, перемножитель кодов, первая группа входов которого подключена к соответствующем выходам второго блока памяти, последовательно соединенные регистр памяти, цифроаналоговый преобразователь и фильтр нижних частот, блок синхронизации,выход которого подключен к управляющим входам накопителя и регистра памяти, а выход знакового разряда преобразователя кодов подключён к входу знакового разряда регистра памяти, отличающийся тем, что, с целью повышения спектральной чистоты выходного сигнала, введен сз мматор, при этом выходы перемножителя кодов соединены поразрядно с первой групi. (Л пой входов сумматора, выходы которо- го соединены с соответствующими поразрядными входами регистра памяти, вторая группа входов сумматора соединена поразрядно с соответствующими выходами первого блока памяти, при этом выходы младших разрядов преобразователя кодов подключены к соответствующим входам второй группы входов перемножителя кодов. ;о о 41 СЛ

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифровой синтезатор частот | 1979 |

|

SU813677A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-11-07—Публикация

1983-05-05—Подача