(Л

ел to ел

а ел

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах контроля за технологическими процессами.

Цель изобретения - раолирение функциональных: возможностей за счет обеспечения временного контроля процессов.

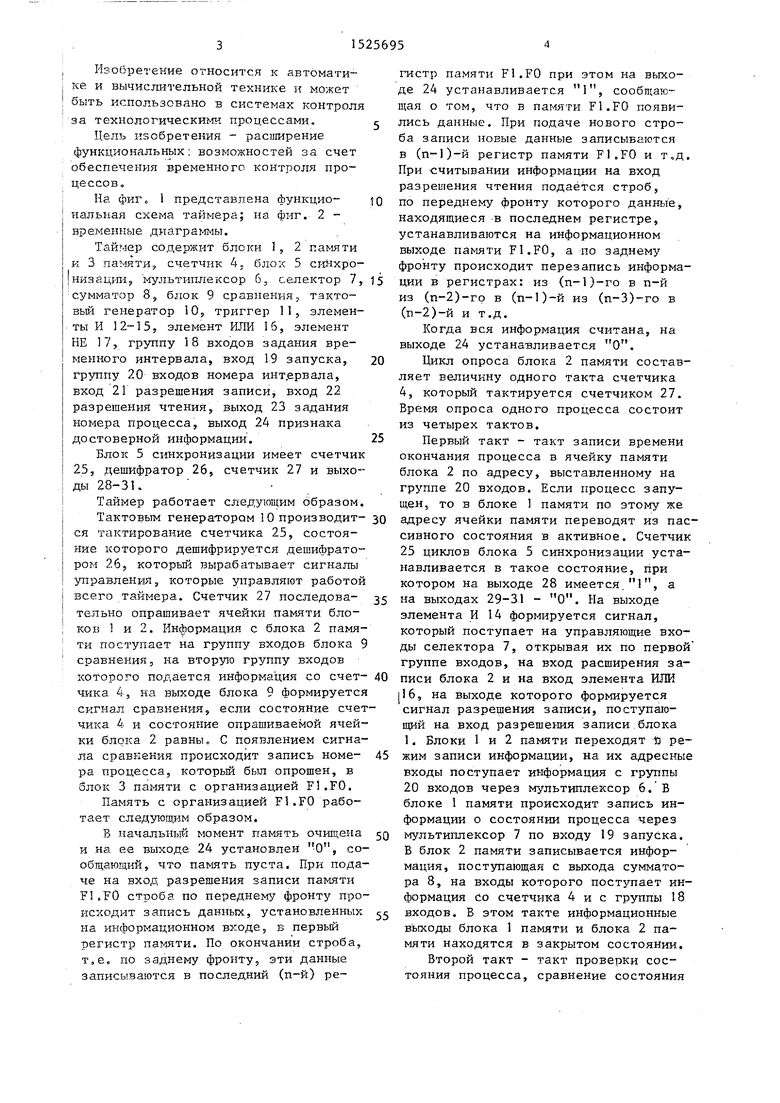

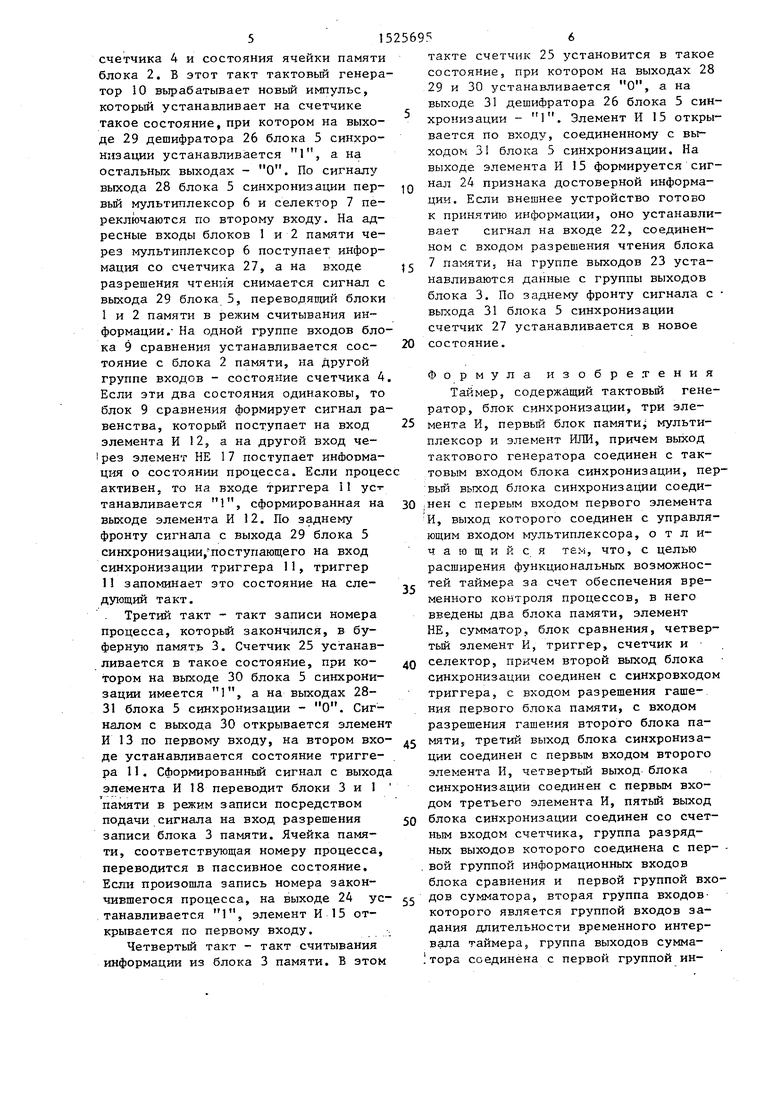

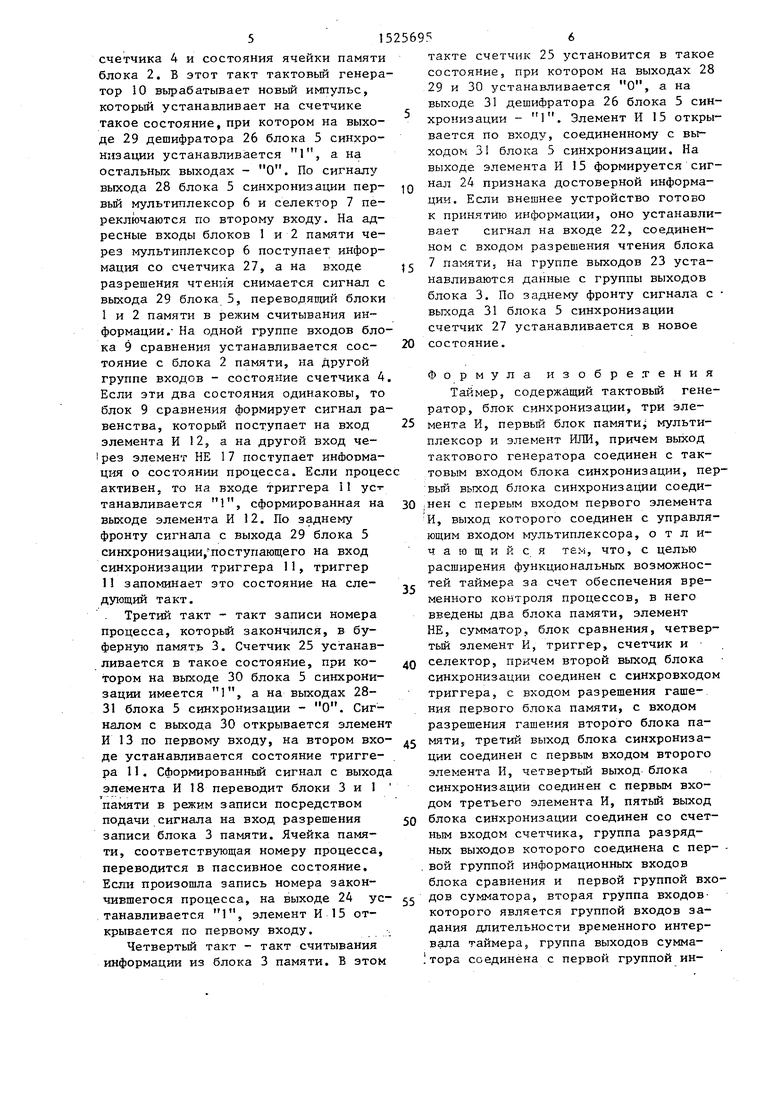

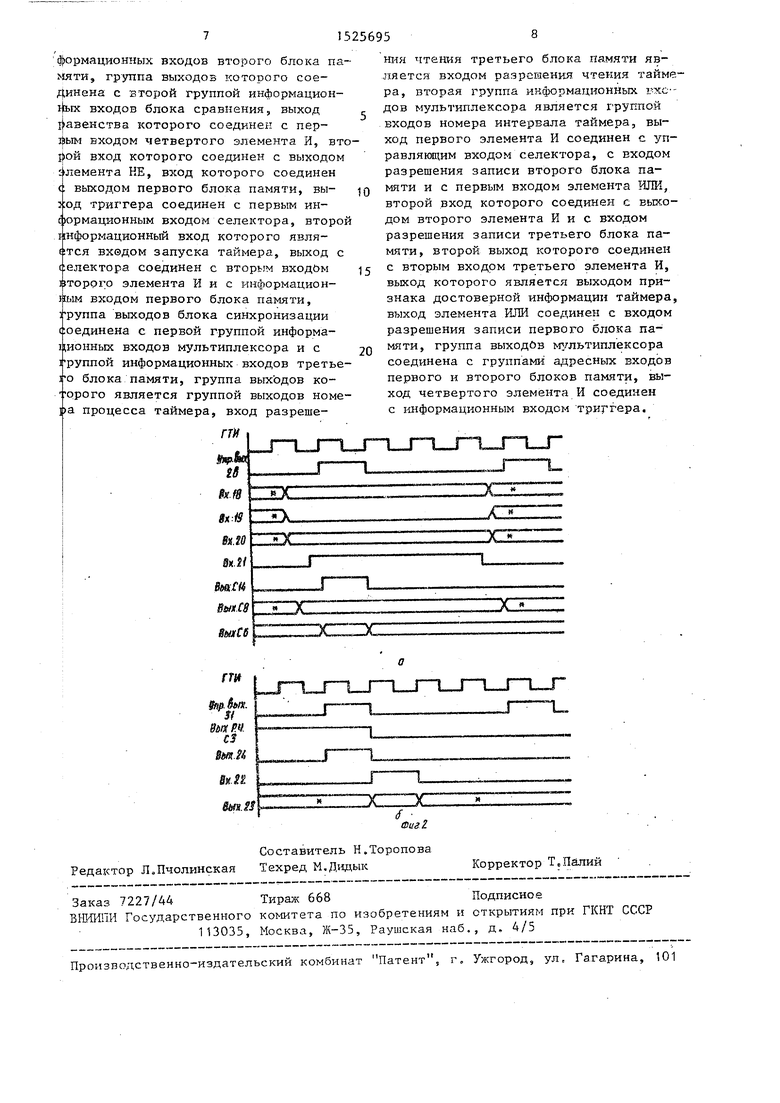

На фиг. 1 представлена функцио- налышя схема таймера; на фиг. 2 - временные диагра1-1мы.

Таймер содержит блоки 1, 2 памяти и 3 памяти., счетчик 4. блок 5 синхро- низацш-,, мультиплексор 6, селектор 7, сумматор 8, блок 9 сравнения, такто- вьм генератор 10, триггер 11, элементы И 12-15, элемент ИЛИ 16, элемент НЕ 17, группу 18 входов задания временного интервала, вход 19 запуска, группу 20 входов номера инт.ервала, вход 21 разрешения записи, вход 22 разрешения чтения, выход 23 задания номера процесса, выход 24 признака достоверной информации.

Блок 5 синхронизации имеет счетчик 25, дешифратор 26, счетчик 27 и выходы 28-3.

Таймер работает следующим образом. Тактовым генераторам 0 производит- ся тактирование счетчика 25, состояние которого дешифрируется дешифратором 26, который вырабатывает сигналы управления, которые управляют работой всего таймера. Счетчик 27 последова- тельно опрашивает ячейки памяти блоков 1 и 2. Информация с блока 2 памяти поступает на группу входов блока 9 сравнения, на вторую группу входов которого подается информация со счет- чика 4, на выходе блока 9 формируется сигнал сравнения, если состояние счетчика 4 и состояние опрашиваемой ячейки блока 2 равньь С появлением сигнала сравнения происходит запись номе- ра процесса, который был опрошен, в блок 3 памяти с организацией F1.FO.

Память с организацией F1.FO работает следующим образом.

В начальньй момент память очищена и на ее выходе 24 установлен -О, сообщающий, что память пуста. При подаче на вход разрешения записи памяти Fl,FO строба по переднему фронту происходит запись данных, установленных на информационном входе, в первьй регистр памяти. По окончании строба, т,е. по заднему фронту, эти данные записываются в последний (п-й) регистр памяти F1.FO при этом на выходе 24 устанавливается 1, сообп1аю- щая о том, что в памяти F1.FO появились данные. При подаче нового строба записи новые данные записываются в (п-1)-й регистр памяти F1.FO и т,д При считывании информации на вход разрешения чтения подаётся строб, по переднему фронту которого данные, находящиеся в последнем регистре, устанавливаются на информационном выходе памяти F1.FO, а по заднему фронту происходит перезапись информации в регистрах: из (n-l)-ro в п-й из (п-2)-гр в (п-1)-й из (п-З)-го в (п-2)-й и т.д.

Когда вся информация считана, на выходе 24 устанавливается О.

Цикл опроса блока 2 памяти составляет величину одного такта счетчика 4, который тактируется счетчиком 27. Время опроса одного процесса состоит из четырех тактов.

Первый такт - такт записи времени окончания процесса в ячейку памяти блока 2 по адресу, выставленному на группе 20 входов. Если процесс запущен, то в блоке 1 памяти по этому же адресу ячейки памяти переводят из пассивного состояния в активное. Счетчик 25 циклов блока 5 синхронизации устанавливается в такое состояние, при котором на выходе 28 имеется., а на выходах 29-3 - О. На выходе элемента И 14 формируется сигнал, который поступает на управляющие входы селектора 7, открывая их по первой группе входов, на вход расширения записи блока 2 и на вход элемента ИЛИ 116, на выходе которого формируется сигнал разрешения записи, поступшо- на вход разрешеьшя записи блока . Блоки 1 и 2 памяти переходят Ю режим записи информации, на их адресны входы поступает информация с группы 20 входов через мультиплексор 6. В блоке 1 памяти происходит запись информации о состоянии процесса через мультиплексор 7 по входу 19 запуска. В блок 2 памяти записывается информация, поступающая с выхода сумматора В, на входы которого поступает информация Со счетчика 4 и с группы 18 входов. В этом такте информационные вькоды блока 1 памяти и блока 2 памяти находятся в закрытом состоянии. Второй такт - такт проверки состояния процесса, сравнение состояния

счетчика 4 и состояния ячейки памяти блока 2. В этот такт тактовьш генератор 10 вьфабатывает новый импульс, который устанавливает на счетчике такое состояние, при котором на выходе 29 дешифратора 26 блока 5 синхронизации устанавливается 1, а на остальных выходах - О, По сигналу выхода 28 блока 5 синхронизации пер- вьш мультиплексор 6 и селектор 7 переключаются по второму входу. На адресные входы блоков 1 и 2 памяти через мультиплексор 6 поступает информация со счетчика 27, а на входе разрешения чтения снимается сигнал с выхода 29 блока 5, переводяпщй блоки

Iи 2 памяти в режим считывания информации .- На одной группе входов блока 9 сравнения устанавливается состояние с блока 2 памяти, на другой группе входов - состояние счетчика 4 Если эти два состояния одинаковы, то блок 9 сравнения формирует сигнал равенства, которьй поступает на вход элемента И 12, а на другой вход чеI рез элемент НЕ 17 поступает информация о состоянии процесса. Если проце активен, то на входе триггера 11 ус танавливается 1, сформированная на выходе элемента И 12. По заднему фронту сигнала с выхода 29 блока 5 синхронизации/поступающего на вход синхронизации триггера 11, триггер

IIзапоминает это состояние на следующий такт.

Третий такт - такт записи номера процесса, который закончился, в буферную память 3. Счетчик 25 устанавливается в такое состояние, при котором на выходе 30 блока 5 синхронизации имеется 1, а на выходах 28- 31 блока 5 синхронизации - О. Сигналом с выхода 30 открывается элемент И 13 по первому входу, на втором входе устанавливается состояние триггера 11. Сформированньм сигнал с выхода элемента И 18 переводит блоки 3 и 1 памяти в режим записи посредством подачи сигнала на вход разрешения записи блока 3 памяти. Ячейка памяти, соответствующая номеру процесса, переводится в пассивное состояние. Если произошла запись номера закончившегося процесса, на выходе 24 устанавливается 1, элемент И 15 открывается по первому входу.

Четвертьй такт - такт считывания информации из блока 3 памяти. В этом

0

5

0

5

0

5

0

5

0

5

такте счетчик 25 установится в такое состояние, при котором на выходах 28 29 и 30 устанавливается О, а на выходе 31 дешифратора 26 блока 5 синхронизации - 1. Элемент И 15 открывается по входу, соединенному с выходом 3 блока 5 синхронизации. На выходе элемента И 15 формируется сигнал 24 признака достоверной информации. Если внешнее устройство готово к принятию информации, оно устанавливает сигнал на входе 22, соединенном с входом разрешения чтения блока 7 памяти, на группе выходов 23 устанавливаются данные с группы выходов блока 3. По заднему фронту сигнала с 31 блока 5 синхронизации счетчик 27 устанавливается в новое состояние.

Формула изобретения

Таймер, содержащий тактовый генератор, блок синхронизации, три элемента И, первый блок памяти мультиплексор и элемент ИЛИ, причем выход тактового генератора соединен с тактовым входом блока синхронизации, пер- вьй выход блока синхронизации соеди- .нен с первым входом первого элемента и, выход которого соединен с управляющим входом мультиплексора, отличающийся тем, что, с целью расширения функциональных возможностей таймера за счет обеспечения временного контроля процессов, в него введены два блока памяти, элемент НЕ, сумматор, блок сравнения, четвертый элемент И, триггер, счетчик и селектор, причем второй выход блока синхронизации соединен с синхровходом триггера, с входом разрешения гашения первого блока памяти, с входом разрешения гашения второго блока памяти, третий выход блока синхронизации соединен с первым входом второго элемента И, четвертый выход блока синхронизации соединен с первым входом третьего элемента И, пятьш выход блока синхронизации соединен со счетным входом счетчика, группа разрядных выходов которого соединена с пер- - вой группой информационных входов блока сравнения и первой группой входов сумматора, вторая группа входов- которого является группой входов задания длительности временного интервала таймера, группа выходов сумма- 1 тора соединена с первой группой ин

| название | год | авторы | номер документа |

|---|---|---|---|

| Таймер | 1985 |

|

SU1357939A1 |

| Логический анализатор | 1989 |

|

SU1730627A1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| Устройство для сопряжения ЦВМ с внешним устройством | 1989 |

|

SU1661779A1 |

| Таймер | 1987 |

|

SU1444738A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Логический анализатор | 1988 |

|

SU1654822A1 |

| Программируемое устройство для вычисления логических функций | 1987 |

|

SU1444744A1 |

| Устройство для отладки многопроцессорных систем | 1988 |

|

SU1644145A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

Изобретение относится к автоматике и вычислительной технике, в частности может быть использовано в системах контроля за технологическими процессами. Отличительной особенностью таймера является то, что он позволяет контролировать временные процессы, протекающие одновременно. Отсчет времени для каждого процесса происходит независимо. Целью изобретения является расширение функциональных возможностей за счет обеспечения временного контроля процессов. Поставленная цель достигается введением блоков 1, 3 памяти, счетчика 4, селектора 7, сумматора 8, блока 9 сравнения, триггера 11, элемента И 15, элемента НЕ 17. 2 ил.

пг

| Программно-временное устройство | 1981 |

|

SU1003025A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Таймер | 1985 |

|

SU1357939A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-11-30—Публикация

1987-06-01—Подача