фиг.1

1информации блоком 2 управления, вы- |полненным на микропроцессоре, при переключении на резервный источник 7 питания и исключении тем самым сбойных ситуаций в микропроцессорной системе при перерывах питания основного источника 6 питания о Устройство содержит блок 1 памяти, блок 2 управ- :ления, ключ 4, переключатель 9 и до- :полнителькый переключатель 10, -двух- I канальный интегрирующий блок 8, ком- InapaTop 26, селекторы переднего 18

и заднего 11 фронтов, триггеры прерывания 13 и запрета записи 21, элементы ИЛИ 16, 22с, При снижении питающего напряжения основного источника 6 устройство подключает к резервному .источнику 7 не только блок 1 памяти, но и блок 2 управления на время обработки прерывания, после чего он отключается от резервного источника 6 о Это позволяет исключить сбойные ситуации при перерывах питания 2- ил„

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ИЗМЕРЕНИЯ ПАРАМЕТРОВ ТЕЛЕВИЗИОННЫХ ОПТИЧЕСКИХ СИСТЕМ | 1991 |

|

RU2010448C1 |

| Устройство контролируемого пункта | 1983 |

|

SU1211784A1 |

| Устройство для ввода дискретных сигналов | 1988 |

|

SU1522221A1 |

| Устройство для диагностики дизельного двигателя внутреннего сгорания | 1981 |

|

SU1002879A2 |

| Цифровой измеритель RLC-параметров | 1986 |

|

SU1337820A1 |

| Устройство для блокировки и перезапуска ЭВМ при сбоях питания | 1987 |

|

SU1464161A1 |

| Устройство для передачи информации с транспортного средства на контрольный пункт | 1973 |

|

SU482340A1 |

| Емкостно-электронный преобразователь перемещения | 1989 |

|

SU1721434A1 |

| Многоканальное регистрирующее устройство | 1988 |

|

SU1698899A1 |

| Устройство для цифровой магнитной записи-воспроизведения | 1987 |

|

SU1481847A1 |

Изобретение относится к системе защиты информации, хранящейся в энергонезависимой памяти, и может быть использовано в вычислительной технике, в микропроцессорных системах. Суть изобретения заключается в предотвращении потери обрабатываемой информации блоком 2 управления, выполненном на микропроцессоре, при переключении на резервный источник 7 питания и исключении тем самым сбойных ситуаций в микропроцессорной системе при перерывах питания основного источника 6 питания. Устройство содержит блок 1 памяти, блок управления 2, ключ 4, переключатель 9 и дополнительный переключатель 10, двухканальный интегрирующий блок 8, компаратор 26, селекторы переднего 18 и заднего 11 фронтов, триггеры прерывания 13 и запрета записи 21, элементы ИЛИ 16, 22. При снижении питающего напряжения основного источника 6 устройство подключает к резервному источнику 7 не только блок памяти 1, но и блок управления 2 на время обработки прерывания, после чего он отключается от резервного источника 6. Это позволяет исключить сбойные ситуации при перерывах питания. 2 ил.

Изобретение относится к системе защиты информации, хранящейся в энергонезависимой памяти, и Может быть использовано в вычислительной технике, технике связи, контрольно-измерительной технике в микропроцессорных системах, требующих сохранения информации при отключении основного источника питающего напряжения„

, Цель изобретения - повьппение надежности устройства за счет исключения потерь информации при переключении на резервное питание

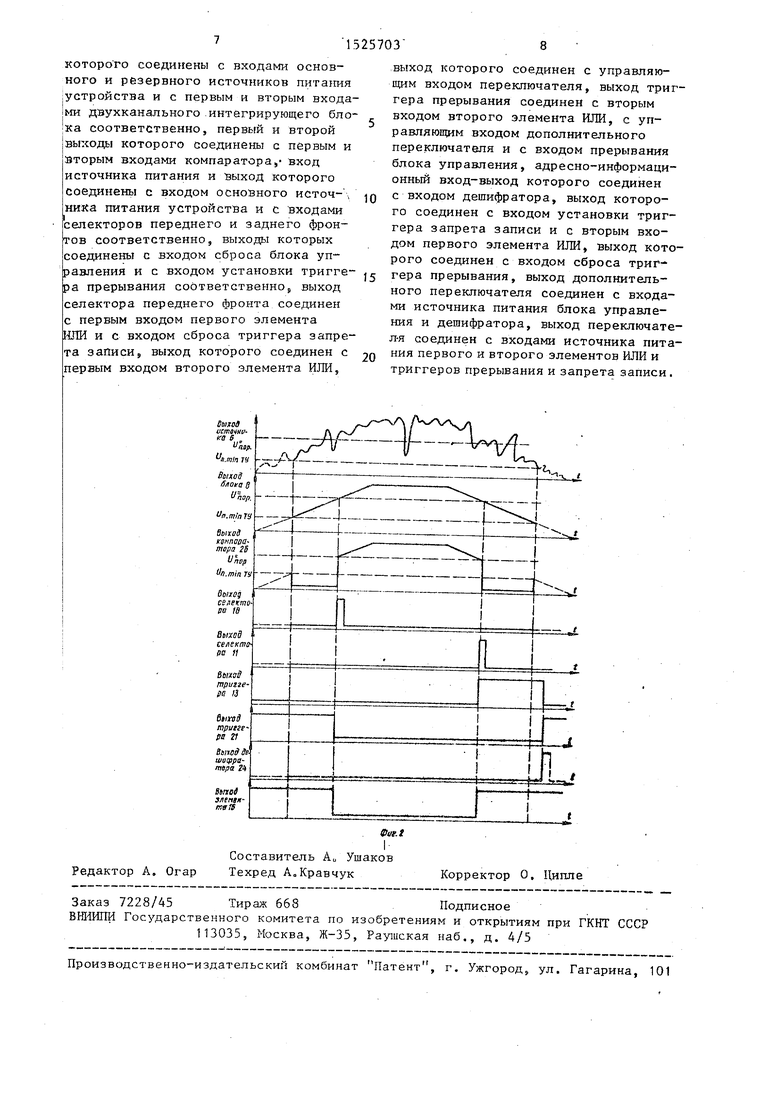

На фиго приведена функциональная схема устройства; на фиГо2 - временные диаграммы его работы,

Устройство содержит (фиг) блок 1 памяти, блок 2 управления, выпол- ненный на микропроцессоре, выход 3 Запись-чтение, ключ 4, вход 5 Запись-чтение, основной 6 и резервный 7 источники питания, двухканальный интегрирующий блок 8, переключатель 9, дополнительный переключатель 10, селектор 11 заднего фронта, вход 12 установки триггера 13 прерывания, управляющий вход 14, вход 15 прерывания, элемент ИЛИ 16, управляющий вход 17, селектор 18 переднего фронта, входы 19 и 20 сброса, триггер 21 запрета записи, элемент ИЛИ 22, вход 23 сброса, дешифратор 24, упра ЛЯЮ25ИЙ вход 25, компаратор 26 и входы 27 и 28.

Устройство работает следующим образом.

В исходном состоянии, когда осно ной источник 6 выключен, блок 1 подключен к резервному источнику 7 через переключатель 9

0

5

0

5

0

- Триггер 13 прерывания выключен, триггер 21 запрета записи включен и сигнал с его выхода выключает ключ 4, запрещая запись информации в блок 1, Кроме того, сигнал с выхода тригге- .ра 21 через элемент ИЛИ 16 поступает на управляющий вход 17 переключателя 9, подключая резервный источник 7 к бло1|:у 1, ключу 4, триггерам 13 и 21 и элементам ИЛИ 16 и 22,

При повьшении напряжения питания основного источника 6 (фиг,2) в определенный момент (порог срабатывания U задается напряжением резервного источника 7) срабатывает компаратор 26 и по переднему фронту сигнала (перепад из О в 1) срабатывает селектор Ч 8, Сигнал с селектора 18 выключает триггер 13 прерывания, триггер 21 запрета записи и устанавливает блок 2 в режим сброса

При выключении триггера 21 запрета записи включается кпюч 4, разрешая запись в блок 1 по сигналам блока 2, и через элемент ИЛИ 16 переключается переключатель 9, подсоединяя входы источника питания блока I, ключа 4, триггеров 13 и 21, элементов ИЛИ 16 и 22 к основному источнику 6 ,

При этом устройство, читая соответствующую информацию из блока 1 , восстанавливает содержимое рабочих регистров блока 2 (обрабатываемую ранее информацию), анализируя, был ли факт выключения основного источника 6, и, руководствуясь этим, соответствующим образом, подготавливается к работе с блоком 1.

В рабочем состоянии устройство находится до тех пор, пока напряжение на выходе блока 8 не уменьшаетт- ся ниже заданного порога В этом случае выключается компаратор 26, по заднему фронту сигнала с выхода которого (переход из 1 в О) срабатывает селектор 11, сигнал с которого включает триггер 13 прерывания о

Сигнал с выхода триггера 13 прерывания, поступая на вход 14 дополнительного переютючателя 10, подключает входы источника питания дешифратора 24 и блока 2 к резервному источнику 7 (переключает дополнительный переключатель 10 - это дает возможность работать блоку 2 и дешифратору 24 при напряжении питания ниже минимального значения по ТУ на эти микросхемы), поступая на вход 15 прерывания, переводит блок 2 в режим прерывания, поступая через элемент ИЛИ 16 на управляющий вход 17 переключателя 9, подключает вход источника питания блока 1 к выходу резервного источника 7. Блок 2 осуществляет обработку программы прерывания, заносит обрабатываемую информацию из рабочих регистров блока 2, а также информацию о факте выключения основного источника 6 в блок 1 и в конце программы обработки прерывания формирует на соответствующих выходах (например, адресных и управляющих) команду, включающую дешифратор 24, Сигнал с выхода дешифратора 24, посту- пая через элемент ИЛИ 22, выключает триггер 13 прерывания и включает триггер 21 запрета записи Приэтом входы источника питания дешифратора 24 и блока 2 подключаются к выходу основного источника 6, блок 1 остается подключенным к выходу резервного источника 7 (за счет сигнала с выхода триггера запрета 21 записи, поступающего через элемент ИЛИ 16), а ключ 4 выключается, запрещая дальнейшую запись ийформации в блок 1,

Двухканальный интегрирующий блок 8 сглаживает кратковременные импульс- Hbie изменения напряжения основного источника 6, которые могут вызвать без необходимости переход блока 2 к обработке прерывания.

Таким образом, в рабочем режиме все блоки и элементы устройства подключены к основному источнику 6,

При уменьшении напряжения этого источника ниже заданного порога происходит подключение блока 1, ключа

1525703

0

5

0

5

0

5

0

&

0

5

4, триггеров 13 и 21, элементов ИЛИ 16 и 22, дешифратора 24 и блока 2 к резервному источнику 7, обработка режима прерывания блоком 2 и по его сигналу (с помощью дешифратора 24) выключение ключа 4, отключение бло-. ка 2 и дешифратора 24 от резервного источника 7 и подютючение к основному источнику 6, а блок 1, кпюч 4, триггеры 13 и 21 и элементы 1ШИ 16 и 22 остаются подключенными к резервному Источнику 7 о

В этом состоянии информация хранится в блоке 1 до включения основного источника 6 о Это. позволяет обеспечить блок 2 и дешифратор 24 питанием от резервного источника 7 на время обработки прерывания, программное отключение блока 2 и дешифратора 24 от резервного источгшка 7, отключение шины записи от блока 1, что повышает надежность рабо ты ьшкро- процессорной системы и позволяет сохранить необходимую информацию в блоке 1 ,

Формула изобретения

Запоминающее устройство с сохранением информации при отключении питания, содержащее блок памяти, блок управления, триггер запрета записи, ключ, два элемента ИЛИ и перекпк - чат ель, первый и второй информационные входы которого являются входами основного и резервного источников питания устройства соответственно, выход переключателя подютючен к входам источника питания блока памяти и ключа, выход триггера запрета записи подключен к управляющему входу ключа, информационный вход и выход которого .подключены к выходу Запись- чтение блока управления и к входу 3anHcb-4TeHiie блока памяти соответственно, адресно-информационный вход- выход которого соединен с одноимен- ным входом-выходом блока управления, отличающееся тем, что, с целью повьшения надежности устройства за счет исключения потерь информации при переключении на резервное питание, в него введены двухканаль- ный интегрирующий блок, компаратор, селекторы переднего и заднего фронтов, триггер прерывания, дешифратор и дополнительньш переключатель, первый и второй информационные входы

которо го соединены с входами основного и резервного источников питагшя устройства и с первым и вторым входа- 1ми дэухканального.интегрирующего бло- 1ка соответственно, первый и второй |выходы которого соединены с первым и вторым входами компаратора,- вход источника питания и выход которого

соединены с входом основного ИСТОЧ- ,

ника питания устройства и с входами селекторов переднего и заднего фронтов соответственно, выходы которых соединены с входом сброса блока упаэления и с входом установки тригге- pa прерывания соответственно, выход

електора переднего фронта соединен

первым входом первого элемента ИЛИ и с входом сброса триггера запрета записи, выход которого соединен с первым входом второго элемента ИЛИ,

Sbnei 311(н1я те IS

выход которого соединен с управляющим входом переключателя, выход триггера прерывания соединен с вторым входом второго элемента ИЛИ, с управляющим входом дополнительного переключателя и с входом прерывания блока управления, адресно-информационный вход-выход которого соединен с входом дешифратора, выход которого соединен с входом установки триггера запрета записи и с вторым входом первого элемента ИЛИ, выход которого соединен с входом сброса триггера прерывания, выход дополнительного переключателя соединен с входами источника питания блока управления и дешифратора, выход переключате- л-я соединен с входами источника питания первого и второго элементов ИЛИ и триггеров прерывания и запрета записи.

| Устройство для защиты информации в блоках памяти при отключении питания | 1986 |

|

SU1363222A2 |

Авторы

Даты

1989-11-30—Публикация

1987-10-26—Подача