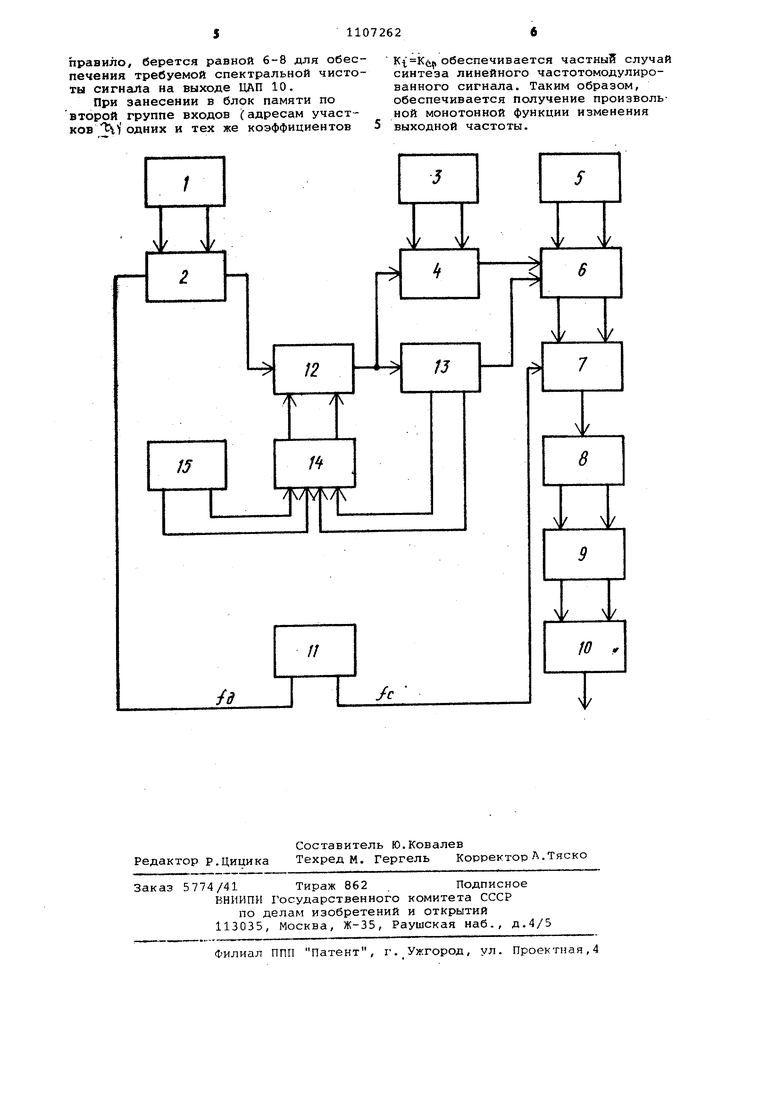

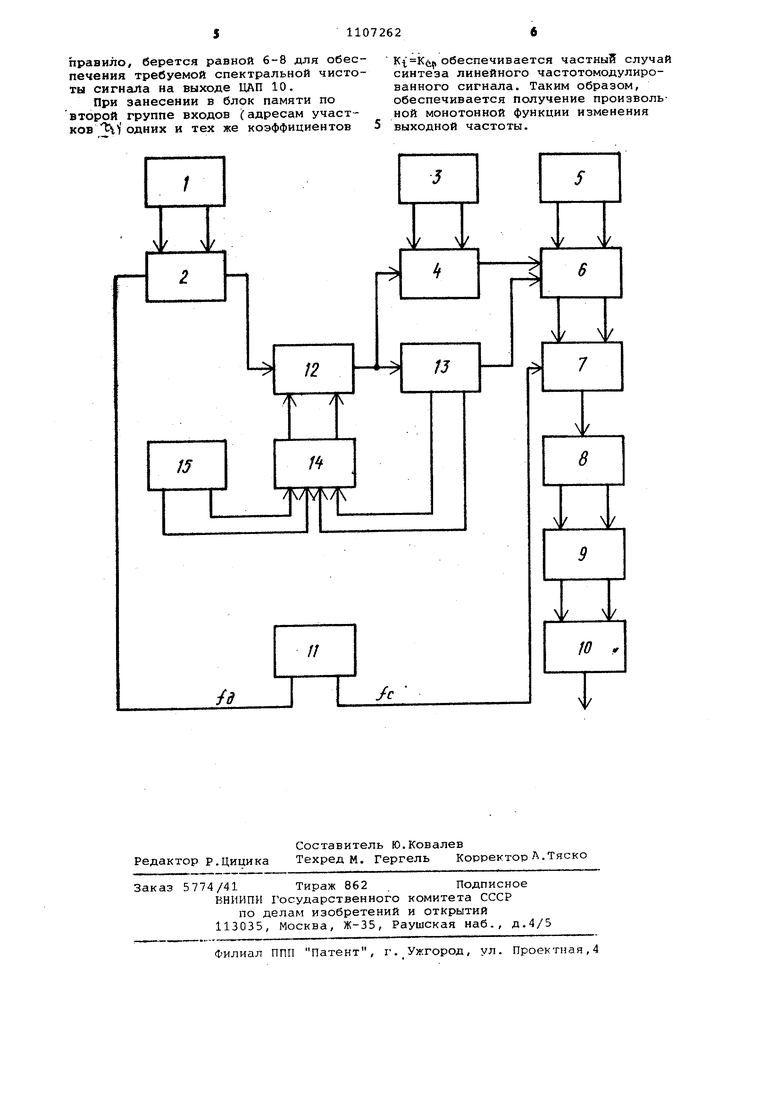

Изобретение относится к радиотех нике и может использоваться для получения изменяющейся по произволь ному закону частоты в системах свя гидролокации и в устройствах вычис лительной техники. Известен цифровой синтезатор из меняющейся частоты, содержащий последовательно соединенные опорный генератор, блок вычисления фазы, :блок памяти, цифроаналоговый преоб |разователь и фильтр нижних частот, а также блок установки частоты ClI. Однако известный цифровой синтезатор изменяклцейся частоты не позво ет получить произвольного закона изменения выходной частоты. Наиболее близким по технической сущности к изобретению является циф ровой синтезатор изменяющейся часто ты, содержащий последовательно соед ненные датчик кода длительности сигнала и первый делитель частоты с переменным коэффициентом деления последовательно соединенные датчик кода диапазона частот, первый делитель частоты с дробно-переменным коэффициентом деления, реверсивный счетчик, второй делитель частоты с дробно-переменным коэффициентом дел ния, счетчик приращения файы,вычислитель амплитуд и цифроаналоговый преобразователь, задающий генератор первый и второй выходы которо го соединены соответственно с тактовым .входом первого делителя частоты с переменным коэффициентом деления и с тактовым входом второго делителя частоты с дробно-переменным коэффициентом деления, а также датчик кода начальной частоты, выходы кото рого подключены к соответствующим установочным входам -реверсивного .счетчика .2. Известный цифровой синтезатор изменяющейся частоты формирует на выходе только линейно-частотно-моду лированный сигнал, так как задающий генератор выдает на вход реверсивного счетчика частоту, неизменную во всем временном интервале синтеза выходного сигнала. Цель изобретения - получение произвольной монотонной функции изменения выходной частоты. Цель достигается тем, что в цифр вой синтезатор изменяющейся частоты содержащий последовательно соединенные датчик кода длительности сигнала и первый делитель частоты с переменным коэффициентом деления, последовательно соединенные датчик кода диапазона частот, первый делитель частоты с дробно-переменным коэффициентом деления, реверсивный счетчик, второй делитель частоты с дробно-переменным коэффициентом деления, счетчик приращения фазы, вычислитель амплитуд и цифроаналоговый преобразователь, задающий генератор, первый и второй выходы которого соединены соответственно с тактовым входом первого делителя частоты с переменным коэффициентом деления и с тактовым входом второго делителя частоты с дробно-переменным коэффициентом деления, а также датчик кода начальной частоты, выходы которого .подключены к соответствующим установочным входам реверсивного счетчика, введены последовательно соединенные блок памяти, второй делитель частоты с переменным коэффициентом деления и счетчик, а также датчик адреса функции, выходы которого подключены к первой группе входов блока памяти, при этом выход первого делителя частоты с переменным коэффициентом деления соединен с тактовым, входом второго делителя частоты с переменным коэффицентом деления, выход которого также подключен к тактовому входу первого делителя частоты с дробно-переменным коэффициентом деления, выход разряда переполнения счетчика подключен к входу предварительной установки реверсивного счетчика, а выходы старших разрядов счетчика соединены с второй группой входов блока памяти. На чертеже представлена структурная электрическая схема предлагаемого устройства. Цифровой синтезатор изменяющейся частоты содержит датчик 1 кода длительности сигнала, первый делитель 2 частоты с переменным коэффициентом деления(ДПКД), датчик 3 кода диапазона частот, первый делитель 4 частоты с дробно-переменным коэффициентом деления(ДДПКД), датчик 5 кода начальной частоты,реверсивный счетчикб,второй делитель 7 частоты с дробко-пере- менньлм коэффициентом деления СДДПКД), счетчик 8 приращения фазы, вычислитель 9 амплитуд, цифроаналоговый преобразователь(, задающий генератор 11, второй делитель 12 частоты с переменным коэффициентом деления{ДПКД), счетчик 13, блок 14 памяти и датчик 15 адреса функции. Цифровой синтезатор изменяющейся частоты работает следующим образом. При помощи датчика 1 кода длительности, датчика 3 кода диапазона, датчика 5 кода начальной частоты и датчика 15 адреса функции устанавливаются необходимые значения соответственно кода длительности сигнала / диапазона изменения частоты Д, начальной частоты fц и код адреса требуемой функции изменения частоты из набора занесенных в блок 14 памяти. Импульсы с выхода второго ДПКД 12 поступают одновременно на первый ДДПКД 4 и на вход счетчика 13, имею щих равную емкость 2& . Каждому t-м линейному участку аппроксимации выбранной функции изменения частоты соответствует коэффициент деления .н управляющих входах второго ДПКД 12 который может изменяться только через импульсов на его выходе, где р - число с.тарших разрядов счет чика 13, соединенных с блоком 14 памяти и определяющих число линейных участков аппроксимации. Именно это .количество импульсов необходимо для смены адреса обращения к блоку 14 памяти. Смена кода по второй группе входов блока 14 памяти через постоянное число импульсов обеспечивает аппроксимацию функции линейными участками с равномерным разбиение по частоте на Д/2 и неравномерньпи разбиением по времени на trДействительно время отработки длительности tt одиночного сигнала определяется поступлением на счетчи 13 и первый ДЦПКД 4 2 импульсов, из которых на выход первого ДДПКД 4 поступает толькос импульсов, соответствующих установленному диапазону изменения частоты Д, следовательно, на каждый 2 выходных импульсов первого ДДПКД 4 приходится С1../2р выходных импульсов. Длительность t каждого г-го ли нейного участка аппроксимации функц (интервал времени, за который на выходе второго ДПКД 12 появляется импульсов пропорциональна пери оду Тл частоты на первом выходе задающего генератора 11, коэффициента деления К,первого ДПКД 2 и второго ДПКД 12 Kt г 2VKi-Ki. Длительность сигнала tc-это сумма всех г С-р г. 2 TXK.K ,. Для занесения К в блок 14 памя предварительно из условий требуемой точности аппроксимации функции опре деляется средний целочисленный коэффициент Kiel,второго ДПКД 12 Кх 2 ,|,K, , при этом L С- ТА К К Так как всер участков аппроксимации имеют равное приращение по .частоте Д/2 , то коэффициенты -Ki можно определять как целочисленные отношения интервалов t. Отработка длительности сигнала с. опреде/;яетс моментом переполнения счетчика 13 через 2 импульсов на его входе, результате чего импульс переполнен сбрасывает реверсивный счетчик 6 в начальное состояние по входу предустановки. Первоначально установленное в реверсивном счетчика 6 число 0., соответствующее начальной- частоте на каждом -м линейном участке аппроксимации функции, изменяется на величину с /2 и за время полной отработки tt на величину , причем частота поступления импульсов ,, в реверсивный счетчик 6 с выхода первого ДДПКД 4 зависит от крутизны; линейного участка аппроксимации функции (от коэффициента . (MCi-lcO%/2 fiC / K,-KilИмпульсы частоты синхронизации $ поступают с второго выхода зада- ющего генератора 11 на тактовый вход второго ДДПКД 7 емкостью 2, частота на его выходе f ч- f с.- (3./2.Ц где й- - текущее значение числа в реверсивном счетчике 6. Счетчик 8 приращения фазы емкостью 2 подсчитывает число импульсов, поступающих на его вход, полное его заполнение соответствует, отсчету периода 2з синусоиды выходной частоты .. Вычислитель 9 амплитуды преобразует непрерывно нарастающие числа счетчика 8 приращения фазы в текущее цифровое значение амплитуды, которые преобразуются ЦАП 10 в непрерывный выходной сигнал с частотой V2 fca/2 Соответственно начальная и Конечная выходные частоты определяются как feuxH unA ; :fe«x..aH qJ/2r Диапазон изменения частоты через .параметры цифрового синтезатора выра|жается зависимостью . Коэффициенты выбираются из условий обеспечения необходимой точности аппроксимации исходной функции изменения частоты. Чем больше РИ i.ep f тем больше участков аппроксимации и точнее границы их смены по отношению к исходной кривой изменения частоты. Емкость 2 первого ДЦПКД 4 определяется верхним значением диапазона частот, устанвливаемым датчиком 3 кода диапазона. Емкость 2 второго ДЦПКД 7 определяется исходя из требуемого шага . дискретного приращения частоты, равной минимальной выходной частоте при этом величина m , как 1

правило, берется равной 6-8 для обеспечения требуемой спектральной чистоты сигнала на выходе ЦАП 10.

При занесении в блок памяти по второй группе входов (адресам участков одних и тех же коэффициентов

,р обеспечивается частный случай синтеза линейного частотомодулированного сигнала. Таким образом, обеспечивается получение произвольной монотонной функции изменения выходной частоты.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор изменяющейся частоты | 1988 |

|

SU1525861A1 |

| Цифровой синтезатор изменяющейся частоты | 1985 |

|

SU1298836A1 |

| Цифровой синтезатор изменяющейся частоты | 1988 |

|

SU1525860A2 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ДРОБНЫМ ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1992 |

|

RU2041563C1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ДРОБНЫМ ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 2002 |

|

RU2222101C2 |

| Генератор синусоидальных колебаний инфранизкой частоты | 1986 |

|

SU1334354A1 |

| Цифровой синтезатор изменяющейся частоты | 1988 |

|

SU1578800A1 |

| Синтезатор частот | 1986 |

|

SU1396279A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2008 |

|

RU2379830C1 |

| Цифровой синтезатор частот | 1988 |

|

SU1566454A1 |

ЦИФРОВОЙ СИНТЕЗАТОР ИЗМЕНЯЮЩЕЙСЯ ЧАСТОТЫ, содержащий последовательно соединенные датчик кода длительности сигнала и первый делитель частоты с переменным коэффициентом деления, последовательно соединенные Датчики кода диапазона частот, первый делитель частоты с дробно-переменным коэффициентом деления, реверсивный счетчик, второй делитель частоты с дробно-переменным коэффициентом деления, счетчик приращения фазы, вычислитель амплитуд и цифроаналоговый преобразователь, задающий генератор, первый и второй выходы которого соединены соответственно с тактовым входом первого делителя частоты с переменным коэффициентом деления и с тактовым входом второго делителя частоты с дробно-переменным коэффициентом деления, а также датчик кода начальной частоты, выходы которого подключены к соответствующим установочным входам реверсивного счетчика,о тличающийся тем, что, с целью получения произвольной монотонной функции изменения выходной частоты, введены последовательно соединенные блок памяти, второй делитель с переменным коэффициентом деления и счетчик, а также датчик адреса функции, выходы которЮго подключены к первой группе входов блока Пс1мяти, при этом выход первого делителя частоты с переменным коэффициентом деления соединен с тактовым входом второго делителя частоты с переменным коэффициентом деления, выход которого также подключен к тактовому входу первого делителя частоты с дробно-переменным коэффици- , ентом деления, выход разряда пере- j полнения счетчика подключен к входу j предварительной установки реверсив- i ного счетчика, а выходы старших | разрядов счетчика соединены с i Ч второй группой входов блока памяти. ND а ND

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Шапиро Д.Н., Паин А.А | |||

| Основы теории синтеза частот | |||

| М., Радио и связь, 1981, с | |||

| Вагонный распределитель для воздушных тормозов | 1921 |

|

SU192A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| КРЕПЕЖНЫЙ ЭЛЕМЕНТ ДЛЯ МНОГОСЛОЙНОГО СТЕКЛА И УСТРОЙСТВО С КРЕПЕЖНЫМ ЭЛЕМЕНТОМ, ЗАКРЕПЛЕННЫМ В ПЛАСТИНЧАТОМ МНОГОСЛОЙНОМ ТЕЛЕ | 2001 |

|

RU2241810C2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-08-07—Публикация

1982-11-17—Подача