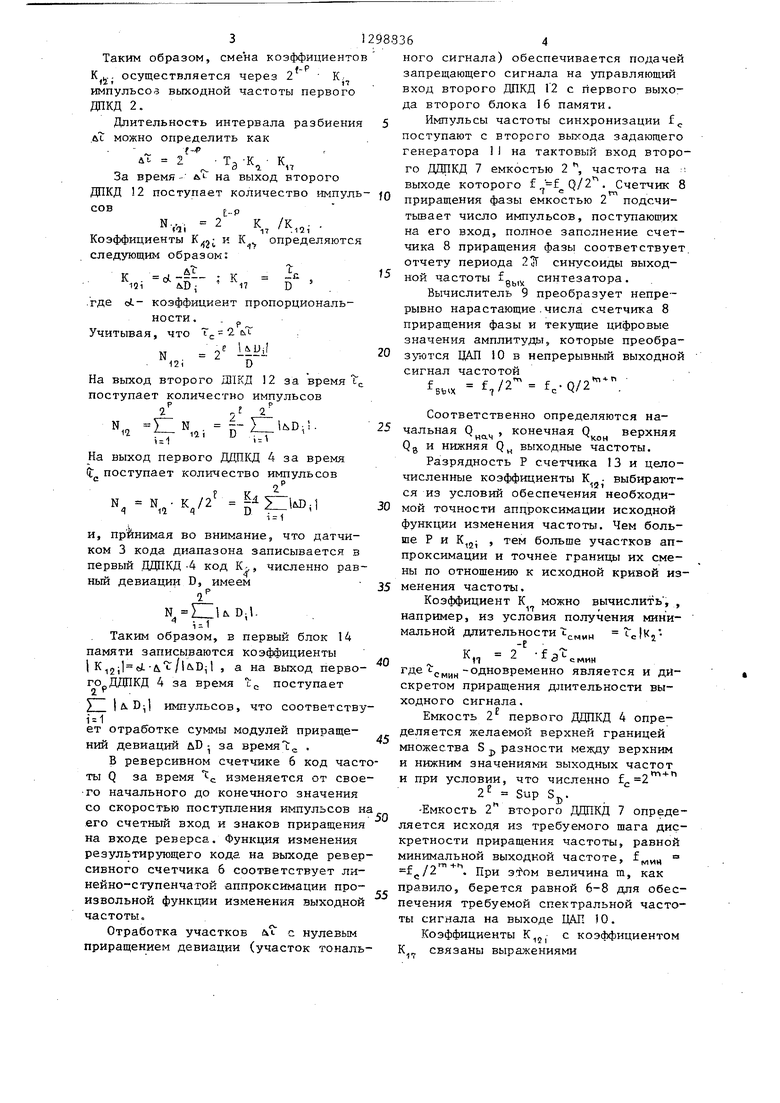

6, счетчик 8 приращения фазы, вычислитель 9 амплитуд, ЦАП 10, задающий генератор 11, счетчик 13, блоки памяти (БП) 14, 16, датчик 15 адреса функции, делитель частоты 17. С помощью датчиков 1, 3, 5, 15 устанавливаются соотв. необходимые значения Каждому линейному участку аппроксимации выбранной функции изменения частоты, записанной в БП 14, 1о соответствует свой коэф.деления на управляющих входах ДПКД 12. Коэф. деления на управляющих входах ДПКД 12

1

Изобретение относится к радиотехнике и может быть использовано для получения изменякщейся по произвольному закону частоты в различных системах связи, гидролокации и в измерительной технике.

Цель изобретения - формирование произвольных законов изменения выходной частоты.

На чертеже представлена структурная электрическая схема цифрового синтезатора изменяющейся частоты.

Цифровой синтезатор изменякяцейся частоты содержит датчик I кода длительности сигнала, первый делитель 2 частоты с переменным коэффициентом деления (дакд), датчик 3 кода диапазона частоты, первый делитель 4 частоты с дробно-переменным коэффициентом деления (ДДПКД), датчик 5 кода начальной частоты, реверсивный счетчик 6, второй ДДЖД 7, счетчик 8 приращения фазы, вычислитель 9 амплитуд цифроаналоговый преобразователь (ЦАП 10, задающий генератор 11, второй ДПКД 12, счетчик 13, первый блок 14 памяти, датчик 15 адреса функции, второй блок 16 памяти, делитель 7 частоты.

Цифровой синтезатор изменяющейся частоты работает следующим образом.

С помощью датчика 1 кода длительности, датчика 3 кода диапазона, датчика 5 кода начальной частоты и датчика 15 адреса функции устанавливают соответственно необходимые значения длительности сигнала fс диапазона

изменяются через определенное кол-во импульсов на входе счетчика 13. «Смена кода на адресных входах БП 14, 16 через постоянное число импульсов обеспечивает аппроксимацию функции линейными участками с равномерным разбиением во времени и, в общем случае, неравномерным разбиением по частоте. Полное заполнение счетчика В соответствует отсчету -периода 23Г синусоиды выходной частоты синтезатора. Вычислитель 9 преобразует значения фазы в цифровые значения амплитуды. 1 ил.

o

5

5

изменения частоты D, начальной частоты „, требуемую функцию изменения частоты из набора занесенных в первый 14 и второй 16 блоки памяти.

Импульсы с выхода второго ДПКД 12 поступают на вход первого ДДПКД 4, имеющего емкость 2 . Каждому i-му линейному участку аппроксимации выбранной функции изменения частоты соответствует коэффициент деления К , на управляющих входах второго ДПКД , 12. Емкость счетчика 13 целесообразно выбирать равной емкости первого ДДПКД 4, т.е. равной 2. Тогда коэффициенты К,2; на управляющих входах второго ДПКД.12 будут изменяться через каждые 2 счетчика 13.

импульсов на выходе

Е-Р

Смена кода на адресньгх входах пер вого 14 и второго 16 блоков памяти через постоянное число импульсов 2 обеспечивает в устройстве аппроксимацию функции линейными участками с равномерным разбиением по времени на и в общем случае неравномерным разбиением по частоте на ьВ .

Длительность отрабатываемого сигнала ТГ определяется по формуле

е . . где 2 - емкость счетчика 13;

Т - период частоты f.,;

К„ - коэффициент деления первого ДПКД 2;

К - коэффициент деления делителя 17 частоты.

Таким образом, смена коэффициентов

f-P К ц., осуществляется через 2 К/

импульсов выходной частоты первого ДПКД 2.

Длительность интервала разбиения .ut

можно определить как

f- p i L 2 -Т:, -к.

К.

-Э 1 -Мт За время - л 1 на выход второго

ДПКД 2 поступает количество импульсов р

Nvai 2 К /К,,, . Коэффициенты - К определяются ел едующим о б р а 3 ом:

&i.

D:

К

17

-Г.

D

. где oL- коэффициент пропорциональности. . „

Учитывая, что

. N,2;

На выход второго Д1ШД 12 за время

поступает количестно импульсов рр

г 2 2

N.™ 111 N , -- .

12

Hi

D

i 1 i l

На выход первого ДЦПКД 4 за время (f поступает количество импульсов

N, Na

К„/2 , 1 1

К D

и, принимая во внимание, что датчиком 3 кода диапазона записывается в первый ДДПКД-4 код К.,, численно равный девиации D, имеем

N LIlbD;l.

i 1

Таким образом, в первый блок 14 памяти записываются коэффициенты 1 1 , а на выход первого ДДПКД 4 за время 1, поступает 2 Р

) |&D:J| импульсов, ЧТО соответству1 1

ет отработке суммы модулей приращений девиаций лО за времяТ: ,

В реверсивном счетчике 6 код частоты Q за время изменяется от свое- го начального до конечного значения со скоростью поступления импульсов на его счетный вход и знаков приращения на входе реверса. Функция изменения результирующего кода на выходе реверсивного счетчика 6 соответствует линейно-ступенчатой аппроксимации произвольной функции изменения выходной частоты.

Отработка участков с нулевым приращением девиации (участок тональ

2983364

ного сигнала) обеспечивается подачей запрещающего сигнала на управляющий вход второго ДПКД 12 с первого выхода второго блока 16 памяти. 5 Импульсы частоты синхронизации f, поступают с второго выхода задающего генератора I на тактовый вход второго ДДПКД 7 емкостью 2 % частота на ; выходе которого . Счетчик 8 О приращения фазы емкостью 2 подсчи- тьшает число импульсов, поступающих на его вход, полное заполнение счетчика 8 приращения фазы соответствует, отчету периода 201 синусоиды выход

15

20

ной частоты fgj, синтезатора.

Вычислитель 9 преобразует непрерывно нарастающие.числа счетчика 8 приращения фазы и текущие цифровые значения амплитуды, которые преобразуются ЦДЛ 10 в непрерывный выходной сигнал частотой

-BbiX

/2 f,.Q/2

5

0

5

0

5

0

5

Соответственно определяются начальная Q , конечная Q верхняя Qg и нижняя Q выходные частоты.

Разрядность Р счетчика 13 и целочисленные коэффициенты К . выбираются из условий обеспечения необходимой точности апцроксимации исходной функции изменения частоты. Чем больше Р и К.,2; , тем больше участков аппроксимации и точнее границы их смены по отношению к исходной кривой изменения частоты.

Коэффициент К можно вычислить , , например, из условия получения минимальной длительности

К,

Ml 3 с мин где LPI I -одновременно является и дискретом приращения длительности выходного сигнала.

Емкость 2 первого ДДПКД 4 определяется желаемой верхней границей множества S разности между верхним и нижним значениями выходных частот

,: о tn + n

И При условии, что численно f 2 2 Sup Sj.

-Емкость 2 второго ДДПКД 7 определяется исходя из требуемого шага дискретности приращения частоты, равной минимальной выходкой частоте, цц . При величина т, как правило, берется равной 6-8 для обеспечения требуемой спектральной частоты сигнала на выходе ПДП )0.

Коэффициенты К,, коэффициентом

К.

связаны выражениями

к

Hi Р

К

17

JD 2 ,

1

If п 2

У к ЗД EI

Ьг ТГГ Следовательно, если все л Dij равны между собой по модулю и знаку, то / К. / К , т.е. имеем частный случай синтеза линейного частотно-модулированного сигнала с возрастающей (. К, ) или убывающей (К К текущей выходной частотой. Случай когда uD,- не равны между собой, но имеют одинаковые значения приращени

т.е,

i -1

luD-l Dj,. соответствует монотонной функции изменения выходной частоты. Наконец, ели D, отличаются между собой по знаку и модулю.

т.е, D( D имеем случай произывольной.функции изменения выходной

частоты.

После отработки функции сигнал с выхода переполнения счетчика 13 обеспечивает установку реверсивного счетчика 6 в исходное состояние по входу предварительной установки, тем самым обеспечивается при необходимости периодическое повторение произвольной функции изменения выходной частоты.

В качестве счетчика 8 приращения фазы используется двоичный счетчик, емкость которого равна числу отсчетов синусоидальной функции на период. Б простейшем случае вычислитель 9 - это блок памяти, в который записаны выборки амплитуды синусоидального сигнала в пределах периода, или преоб-. разователь кодов по квадрантам с блоком памяти выборок амплитуды в пределах одного квадранта.

В качестве задающего генератора 11 может быть использован, например, кварцевый генератор с двумя делителями с постоянными коэффициентами деления, обеспечивающими выходные частоты f 2 и fj, .

В блок 14 памяти заносятся целочисленные коэффициенты отношений ко- танг.енсов углов tfj наклона линейных участков аппроксимации произвольной функции изменения выходной частоты во времени в пределах диапазона ее изменения. Число линейных участков аппроксимации огранр1чено, поэтому избыток объема памяти используется для занесения коэффициентов ряда необхо

988366

димых функций, что обеспечивает оперативную их смену датчиком 15 адреса функции. Например, при использовании ПЗУ на 256 слов в блок 14 памяти мож- 5 но занести 16 функций, аппроксимированных 16 линейными участками.

В блок 16 памяти по первому выходу заносится код управления, который обеспечивает, зайрет рабо.ты второго О ДПКД 12, а следовательно, и всего

тракта формирования кода изменения частоты во время отработки горизонтального участка аппроксимирующей кривой изменения частоты. По второму вы- . 5 ходу блока 16 памяти заносится код управления, обеспечивающий управление реверсом реверсивного счетчика 6 при отработке возрастающего или убывающего участка аппроксимирующей кривой

изменения частоты.

Датчики кода,.длительности, кода диапазона, кода начальной частоты, адреса функции 1, 3, 5 и 15 соответственно выполнены на базе декадных переключателей, но быть выполнены на основе любых коммутацион- элементов.

Счетчик 13 - это двоичный счетчик. Число старших разрядов Р счетчика 13, соединенных с первым 14 и вторым 16 блоками памяти, определяется количеством линейных участков аппроксимируемой функции (при 16 линейных участках ). Делитель 17 частоты выполнен на основе пересчетной схемы с постоянным коэффициентом, пересчета.

На основе пересчетных схем также вьтолнены первый 2 и второй 12 ДПКД например, на основе суммирзпющих или вычитающих счетчиков с управляемым сбросом в исходное состояние. Входная частота делится на целостщзй коэффициент деления, занесенный на управляющие входы.

20

25

30

35

40

45

0

5

На базе накапливающего сумматора с использованием выхода по переполнению или преобразователей код - частота : выполнены первьш 4 и второй 7 ДЦПКД выходная частота которых определяется как произведение входной частоты на отношение числа (кода), занесенное го на управляющие входы, к емкости делителя.

Реверсивный счетчик 6 выполнен по счетной схеме, имеющей управляющие входы реверса и предустановки (параллельной записи).

Б предлагаемом цифровом синтезаторе изменяющейся частоты за счет введения второго блока памяти и делителя частоты возможно получение произвольной с одним или более экстремумами функции изменения выходной частоты, в том числе и монотонной, как частный случай. Указанное преимущество позволяет расширить функменным коэффициентом делетшя, датчи кода начальной частоты, поразрядные выходы которого подключены к соотве ствующим установочным входам реверсивного счетчика, последовательно соединенные датчик адреса функции и первый блок памяти, счетчик, выход разряда переполнения которого подкл чен к входу предварительной установ

циональные возможности цифрового син- ки реверсивного счетчика, а выходы

тезатора изменяющейся частоты. Формула изобретения

Цифровой синтезатор изменяющейся частоты, содержащий последовательно соединенные датчик кода: длительности сигнала, первый делитель частоты с переменным коэффициентом деления, второй делитель частоты с переменным коэффициентом деления, первый делитель частоты с дробно-переменным коэффициентом деления, реверсивный счетчик, второй делитель частоты с дробно-переменным коэффициентом деле ния, счетчик приращения фазы, вычислитель амплитуд и цифроаналА овый преобразователь, задающий генератор, первый и второй выходы которого сое15

старших разрядов счетчика соединены с второй группой входов первого блока памяти, а поразрядные выходы первого блока памяти подключены к соответствующим установочным входам второго делителя частоты с переменным коэффициентом дел.ения, отличающийся тем, что, с целью форми- с рования произвольных законов измене- 20 ния выходной частоты, введены второй блок памяти и делитель частоты, тактовый вход которого соединен с выходом первого делителя частоты с переменным коэффициентом деления, а выход делителя частоты подключен к входу счетчика, при этом первый и второй выходы второго блока памяти соединены соответственно с управляющим входом второго делителя частоты с пере 25

динены соответственно с тактовым вхо- менным коэффициентом деления и с входом первого делителя частоты с пере- дом управления реверсом реверсивного менным коэффициентом деления и такто- -счетчика, при этом первая группа вхо- вым входом второго делителя частоты с дов второго блока памяти соединена с дробно-переменным коэффициентом деления, а также датчик кода диапазона частот, поразрядные выходы которого подключены к установочным входам первого делителя частоты с дробно-пересоответствующими поразрядными выхо- 35 дами датчика адреса функции, а вторая группа входов второго блока памяти подключена к соответствующим выходам старщих разрядов счетчика.

Редактор В.Петраш

Составитель Ю.Ковалев

Техредм.Моргентал Корректор А.Зимокосов

Заказ 894/55 Тираж 902Подписное

ВНИШИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раущская наб., д.4/5

Производственно-полиграфическое предприятие,г.Ужгород,ул.Проектная,4

менным коэффициентом делетшя, датчик кода начальной частоты, поразрядные выходы которого подключены к соответствующим установочным входам реверсивного счетчика, последовательно соединенные датчик адреса функции и первый блок памяти, счетчик, выход разряда переполнения которого подключен к входу предварительной установ15

старших разрядов счетчика соединены с второй группой входов первого блока памяти, а поразрядные выходы первого блока памяти подключены к соответствующим установочным входам второго делителя частоты с переменным коэффициентом дел.ения, отличающийся тем, что, с целью форми- с рования произвольных законов измене- 20 ния выходной частоты, введены второй блок памяти и делитель частоты, тактовый вход которого соединен с выходом первого делителя частоты с переменным коэффициентом деления, а выход делителя частоты подключен к входу счетчика, при этом первый и второй выходы второго блока памяти соединены соответственно с управляющим входом второго делителя частоты с пере25

менным коэффициентом деления и с входом управления реверсом реверсивного -счетчика, при этом первая группа вхо- дов второго блока памяти соединена с менным коэффициентом деления и с вхо дом управления реверсом реверсивного -счетчика, при этом первая группа вхо- дов второго блока памяти соединена с

соответствующими поразрядными выхо- 35 дами датчика адреса функции, а вторая группа входов второго блока памяти подключена к соответствующим выходам старщих разрядов счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор изменяющейся частоты | 1988 |

|

SU1525861A1 |

| Цифровой синтезатор изменяющейся частоты | 1982 |

|

SU1107262A1 |

| Цифровой синтезатор изменяющейся частоты | 1988 |

|

SU1525860A2 |

| Цифровой синтезатор изменяющейся частоты | 1988 |

|

SU1578800A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ДРОБНЫМ ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 2002 |

|

RU2222101C2 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ДРОБНЫМ ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1992 |

|

RU2041563C1 |

| Цифровой синтезатор частот | 1988 |

|

SU1566454A1 |

| Генератор синусоидальных колебаний инфранизкой частоты | 1986 |

|

SU1334354A1 |

| Цифровой синтезатор частоты | 1986 |

|

SU1356222A1 |

| Цифровой синтезатор частот | 1990 |

|

SU1748251A1 |

Изобретение относится к радиот - технике и обеспечивает формирование произвольных законов изменения выходной частоты. Цифровой синтезатор со-« держит датчик 1 кода длительности сигнала, делители частоты с переменным коэф. деления (ДОКД) 2,12, датчик 3 кода диапазона частоты, делители частоты с дробно-переменным коэф.деления 4, 7, датчик 5 кода начальной частоты, реверсивный счетчик ю оо оо 00 о

| КРЕПЕЖНЫЙ ЭЛЕМЕНТ ДЛЯ МНОГОСЛОЙНОГО СТЕКЛА И УСТРОЙСТВО С КРЕПЕЖНЫМ ЭЛЕМЕНТОМ, ЗАКРЕПЛЕННЫМ В ПЛАСТИНЧАТОМ МНОГОСЛОЙНОМ ТЕЛЕ | 2001 |

|

RU2241810C2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифровой синтезатор изменяющейся частоты | 1982 |

|

SU1107262A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-03-23—Публикация

1985-07-18—Подача