1

(21)4445143/24-09

(22)04,05,88

(46) 15.07.90с Бкии № 26

(71)Таганрогский радиотехнический институт им„ В о Д« Калмыкова

(72)В0Юо Капустин, В.Со Григорьев и 0„Р, Лапаухова

(53)621.373,42(088,8)

(56)Авторское свидетельство СССР № 1107262, кло Н 03 В 23/00, 1982.

Авторское свидетельство СССР 1279077, кл„ Н 03 В 23/00, 1985о

(54)ЦИФРОВОЙ СИНТЕЗАТОР ИЗМЕНЯЮЩЕЙСЯ ЧАСТОТЫ

(57)Изобретение относится к радиотехнике и может использоваться для получения изменяющейся по произвольному монотонному закону частоты Целью изобретения является повышение точности воспроизведения закона изменения выходной частоты Цифровой синтезатор изменяющейся частоты содержит датчик 1 кода длительности сигнала, датчик 2 адреса функции, датчик 3 кода диапазона частот, датчик 4 кода начальной частоты, блок 5 памяти, перемножитель 6 кодов, делитель 7 частоты с переменным коэффициентом деления, накапливающий сумматор 8, сумматор 9, генератор 10 тактовых импульсов, блок 11 вычисления фазы, вычислитель 12 амплитуды и цифроаналоговый преобразова- Q тель 13 о 1 ил о

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор изменяющейся частоты | 1988 |

|

SU1525861A1 |

| Цифровой синтезатор изменяющейся частоты | 1982 |

|

SU1107262A1 |

| Цифровой синтезатор изменяющейся частоты | 1985 |

|

SU1298836A1 |

| АВТОМАТИЧЕСКИЙ АУДИОМЕТР | 2024 |

|

RU2840436C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ИЗМЕНЯЮЩЕЙСЯ ЧАСТОТЫ | 2015 |

|

RU2597670C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ИЗМЕНЯЮЩЕЙСЯ ЧАСТОТЫ | 2021 |

|

RU2765264C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ИЗМЕНЯЮЩЕЙСЯ ЧАСТОТЫ | 2022 |

|

RU2792012C1 |

| ИМИТАТОР УШНОГО ШУМА | 2022 |

|

RU2815507C1 |

| АУДИОМЕТР | 2022 |

|

RU2791159C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ИЗМЕНЯЮЩЕЙСЯ ЧАСТОТЫ | 2023 |

|

RU2809550C1 |

Изобретение относится к радиотехнике и может использоваться для получения изменяющейся по произвольному монотонному закону частоты. Целью изобретения является повышение точности воспроизведения закона изменения выходной частоты. Цифровой синтезатор изменяющейся частоты содержит датчик 1 кода длительности сигнала, датчик 2 адреса функции, датчик 3 кода диапазона частот, датчик 4 кода начальной частоты, блок памяти 5, перемножитель 6 кодов, делитель частоты с переменным коэффициентом деления 7, накапливающий сумматор 8, сумматор 9, генератор 10 тактовых импульсов, блок 11 вычисления фазы, вычислитель 12 амплитуды и цифроаналоговый преобразователь 13. 1 ил.

С

ел 1

00

00

ыход

5

Изобретение относится к радиотехнике и может использоваться для получения изменяющейся по произвольному монотонному закону выходной частоты.

Цепь изобретения - повышение точности воспроизведения закона изменения выходной частоты.

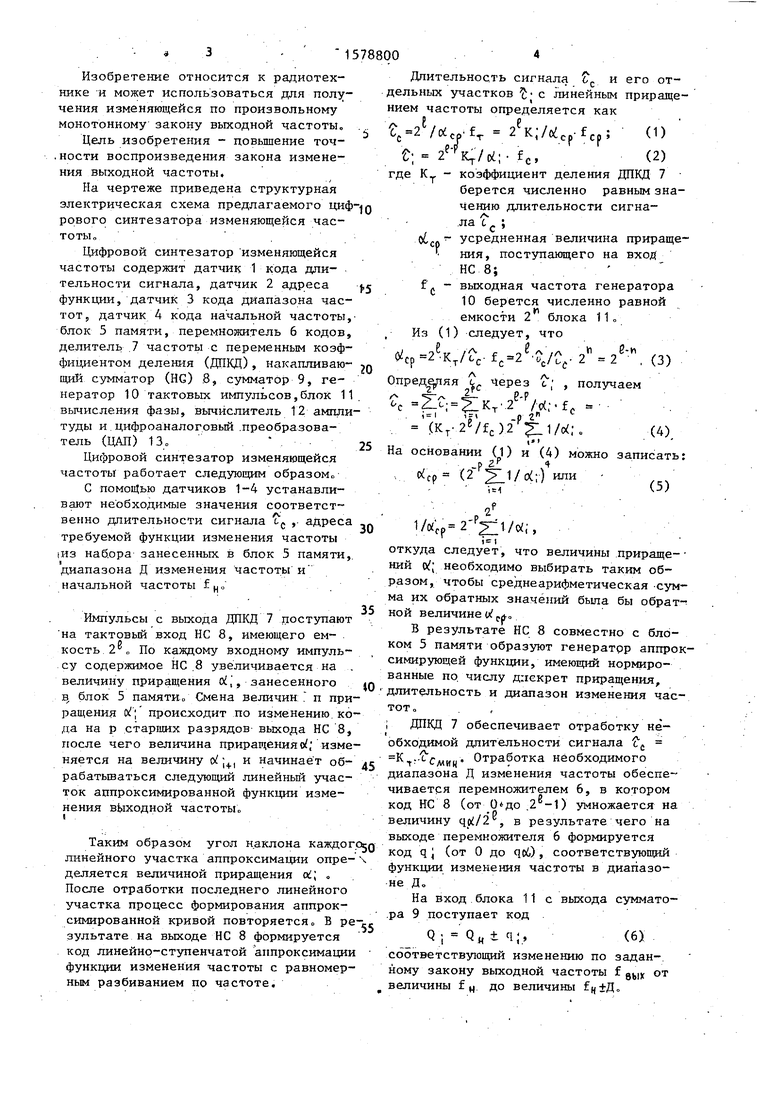

На чертеже приведена структурная электрическая схема предлагаемого циф-jQ рового синтезатора изменяющейся частоты о

Цифровой синтезатор изменяющейся частоты содержит датчик 1 кода длительности сигнала, датчик 2 адреса функции, датчик 3 кода диапазона час- ют, датчик 4 кода начальной частоты, блок 5 памяти, перемножитель 6 кодов, делитель 7 частоты с переменным коэффициентом деления (ДПКД), накапливаю- ,« щий сумматор (НС) 8, сумматор 9, генератор 10 тактовых импульсов,блок 11 вычисления фазы, вычислитель 12 амплитуды и цифроаналоговый преобразователь (ДАЛ) 13,

Цифровой синтезатор изменяющейся частоты работает следующим образом,,

С помоЩью датчиков 1-4 устанавливают необходимые значения соответственно длительности сигнала Јс , адреса .- требуемой функции изменения частоты (Из набора занесенных в блок 5 памяти, диапазона Д изменения частоты и начальной частоты fн„

Импульсы с выхода ДПКД 7 поступают на тактовый вход НС 8, имеющего емкость По каждому входному импульсу содержимое НС 8 увеличивается на величину приращения Oi,, занесенного |Q в, блок 5 памяти о Смена величин п приращения К1; происходит по изменению кода на р старших разрядов выхода НС 8, после чего величина приращения о/; изменяется на величину oi I4-| и начинает об- дс рабатываться следующий линейный участок аппроксимированной функции изменения выходной частотьи

г.

15788004

Длительность сигнала 6С и его отдельных участков Ј с линейным приращением частоты определяется как

faЛ V / - Гг 1

fT 2 к;/сЈср fcp;

ч (Г К fj

Ј:

. f

с

(1) (2)

где KT - коэффициент деления ДПКД 7

берется численно равным значению длительности сигнала Јс ;

оЈ - усредненная величина прираще- ния, поступающего на вход

НС 8;

fc - выходная частота генератора 10 берется численно равной емкости 2 блока 11 Из (1) следует, что

,6„ ,л ,. Л л ,Л „и б-и

У

cp 2v-KT/tc

4 /л «At

А.

Определяя с через с;

Јс -zc,-ibT 2е-рм

г .о 2 g i -

получаем

(кт 2K/fc)2 11/о(;.

(3)

(4)

На основании (р1) и (4) можно записать:

ср ((Уили

,-Р

(5)

1/«сР 2 211М

откуда следует, что величины приращений необходимо выбирать таким образом, чтобы среднеарифметическая сумма их обратных значений была бы обратной величине «f

В результате НС 8 совместно с блоком 5 памяти образуют генератрр аппроксимирующей функции, имеющий нормированные по числу дискрет приращения, длительность и диапазон изменения частот

, ДПКД 7 обеспечивает отработку не- iл

обходимой длительности сигнала сс

Kt Смин необходимого диапазона Д изменения частоты обеспечивается перемножителем 6, в котором код НС 8 (от 2-1) умножается на величину qtf/2 , в результате чего на

„ ,выходе перемкожителя 6 формируется

Таким образом угол наклона каждогогл , s n ,

и код q . (от 0 до qc6) , соответствующий

vuapTva дтттт-пптглт матгмтт оттт% э-

функции изменения частоты в диапазоне До

На вход блока 11 с выхода сумматора 9 поступает код

линейного участка аппроксимации опре деляется величиной приращения od; ° После отработки последнего линейного участка процесс формирования аппроксимированной кривой повторяется о В ре-.

55

зультате на выходе НС 8 формируется код линейно-ступенчатой аппроксимации функции изменения частоты с равномерным разбиванием по частоте.

г.

6С ей я к

faЛ V / - Гг 1

fT 2 к;/сЈср

ч (Г К fj

Ј:

. f

с

5

« 5

где KT - коэффициент деления ДПКД 7

берется численно равным значению длительности сигнала Јс ;

оЈ - усредненная величина прираще- ния, поступающего на вход

НС 8;

fc - выходная частота генератора 10 берется численно равной емкости 2 блока 11 Из (1) следует, что

,6„ ,л ,. Л л ,Л „и б-и

У

cp 2v-KT/tc

4 /л «At

А.

Определяя с через с;

Јс -zc,-ibT 2е-рм

г .о 2 g i -

получаем

(кт 2K/fc)2 11/о(;.

(3)

(4)

На основании (р1) и (4) можно записать:

ср ((Уили

(5)

,-Р

1/«сР 2 211М

откуда следует, что величины приращений необходимо выбирать таким образом, чтобы среднеарифметическая сумма их обратных значений была бы обратной величине «f

В результате НС 8 совместно с блоком 5 памяти образуют генератрр аппроксимирующей функции, имеющий нормированные по числу дискрет приращения, длительность и диапазон изменения частот

, ДПКД 7 обеспечивает отработку не- iл

обходимой длительности сигнала сс

Kt Смин необходимого диапазона Д изменения частоты обеспечивается перемножителем 6, в котором код НС 8 (от 2-1) умножается на величину qtf/2 , в результате чего на

.

55

Q; Qwt q;,

(6)

соответствующий изменению по заданному закону выходной частоты f вы)( от величины f H до величины ffj+До

Блоки 11 и 12 обеспечивают формирование выходной синусоидальной функции с частотой, определяемой выражением

Bbllf е

Q;/2M,

(7)

и при условии, что fc численно равна 2, имеем fBb,x, численно равную QJ0 Если о(; то имеем случай синтеза линейно частотномодулированного сигнала,, При С(, 0 синтезируется тональный сигнал с частотой Јц„ Минимальная длительность отрабатываемого циф- ровым синтезатором изменяющейся частоты сигнала по аналогии с (1) определяется как

- т 2 / . /«с

f

С

(8)

т.е„ она пропорциональна емкости НС 8 и обратно пропорциональна среднему значению величины приращения на линейном участке.

Таким образом, предлагаемый цифровой синтезатор изменяющейся частоты обеспечивает более высокую точность воспроизведения закона изменения выходной частоты при сохранении пределов установки диапазона выходной частоты и длительности выходного сигнала.

Q г

0

5

0

5

Формула изобретения Цифровой синтезатор изменяющейся частоты, содержащий последовательно соединенные датчик кода длительности сигнала и делитель частоты с переменным коэффициентом деления, последовательно соединенные датчик кода диапазона частот, перемножитель кодов, сумматор, блок вычисления фазы, вычислитель амплитуды и цифроаналоговый преобразователь, а также датчик кода начальной частоты, выходы которого соединены с другими соответствующими входами сумматора, генератор тактовых импульсов, выход которого подключен к тактовым входам делителя частоты с переменным коэффициентом деления и блока вычисления фазы, датчик адреса функции и блок памяти, отличающийся тем, что, с целью повышения точности воспроизведения закона изменения выходной частоты, введен накапливающий , сумматор, разрядные выходы которого соединены с первыми адресными входами блока памяти и с другими входами перемножителя кодов, при этом выход делителя частоты с переменным коэффициентом деления соединен с тактовым входом накапливающего сумматора, к информационным входам которого подключены поразрядно выходы блока памяти, вторые адресные входы которого соединены поразрядно с выходами датчика адреса функции

Авторы

Даты

1990-07-15—Публикация

1988-05-04—Подача