10

1453408

Изобретение относится к технике автоматизации разработки микропроцессорных систем и предназначено длч использования во внутрисхемныхэмуляторах, замещающих в отхшживаемой системе микропроцессор неконвейерной архитектуры с открытой системой шин.

Цель изобретения - упрощение устройства .

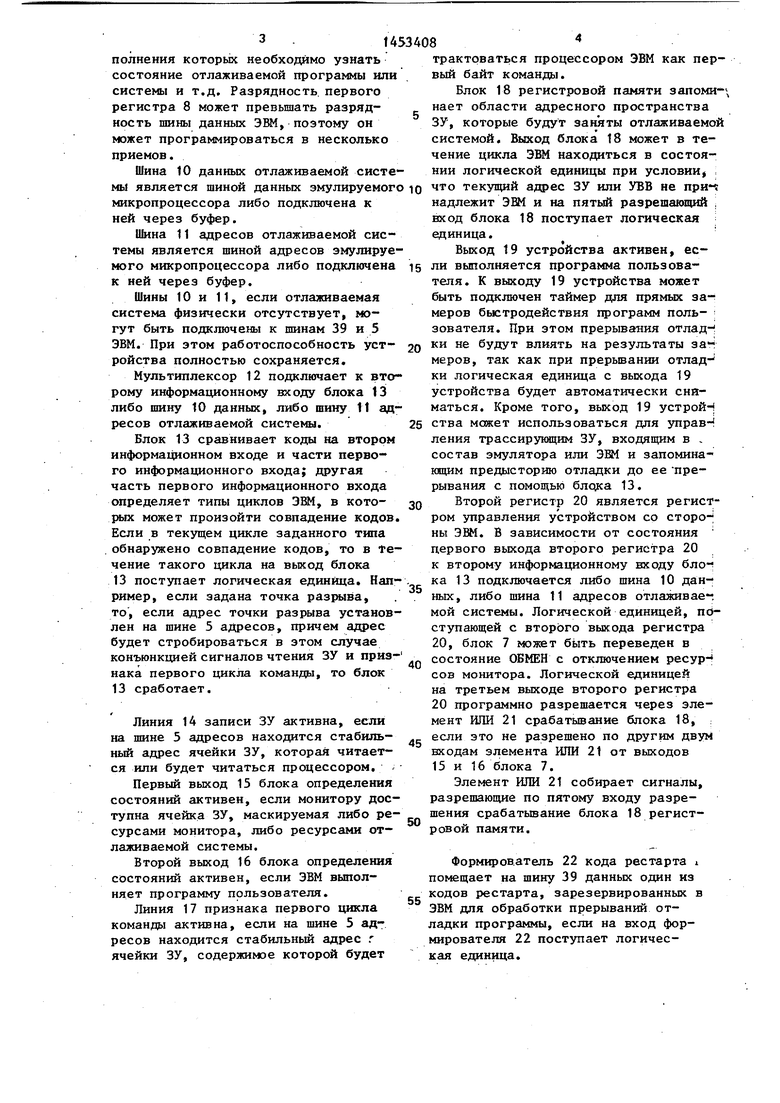

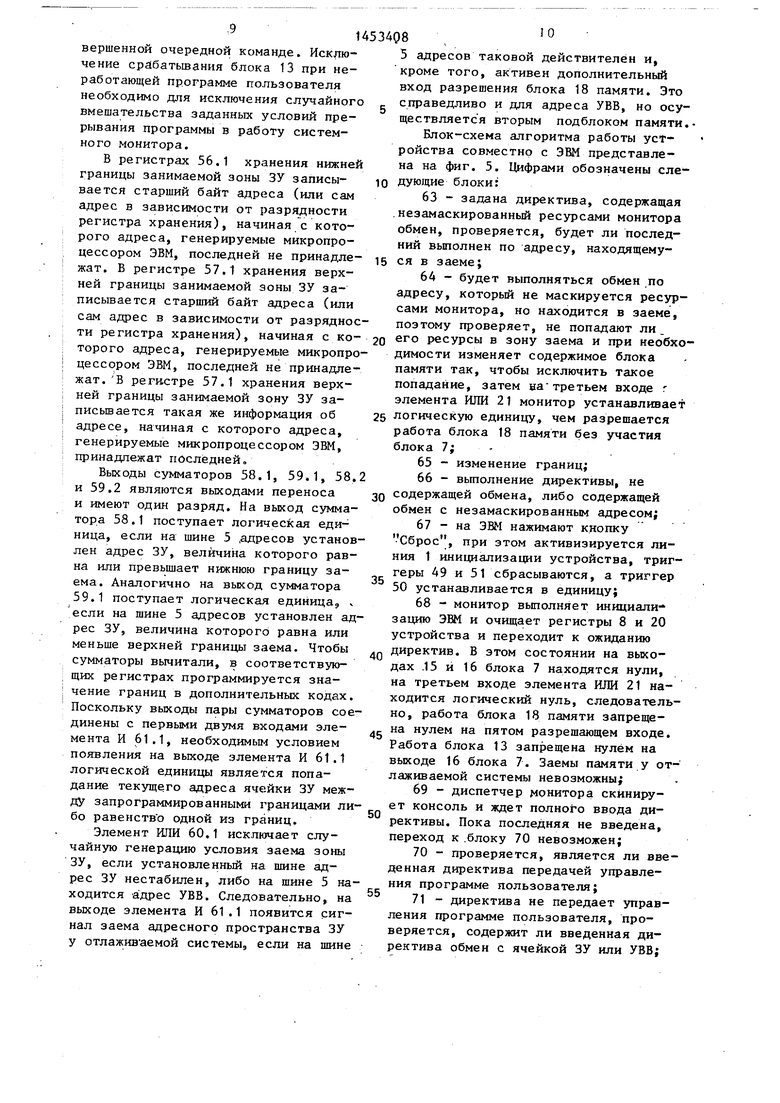

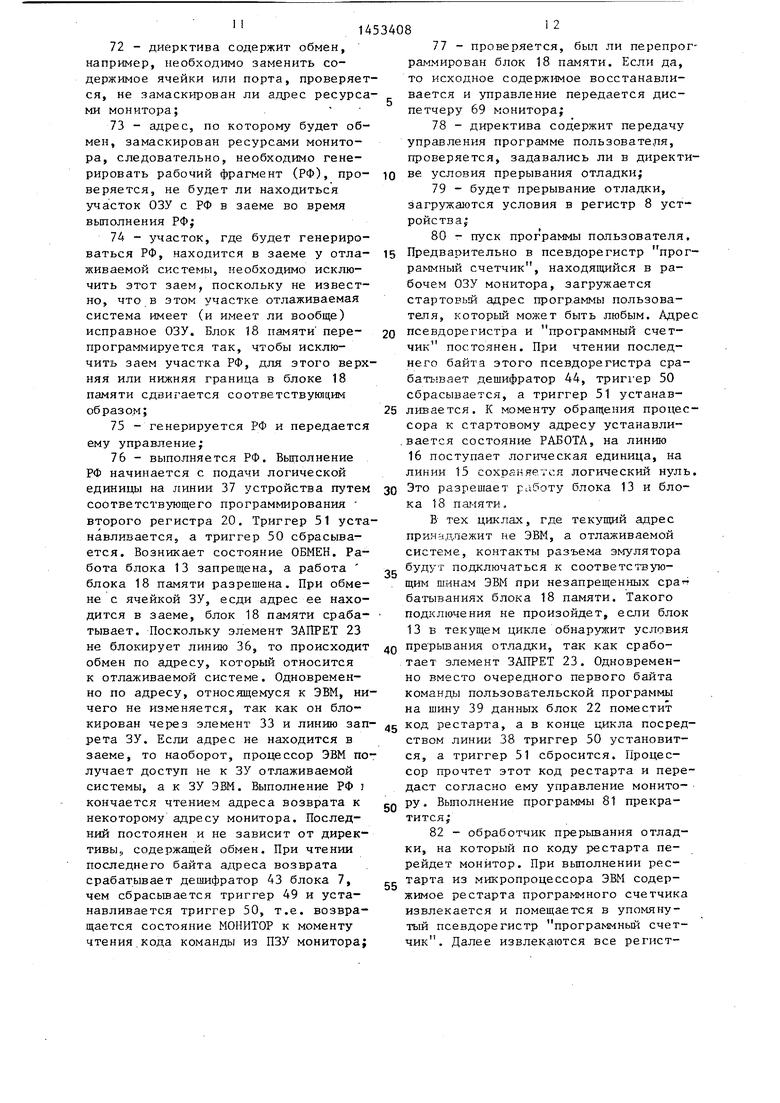

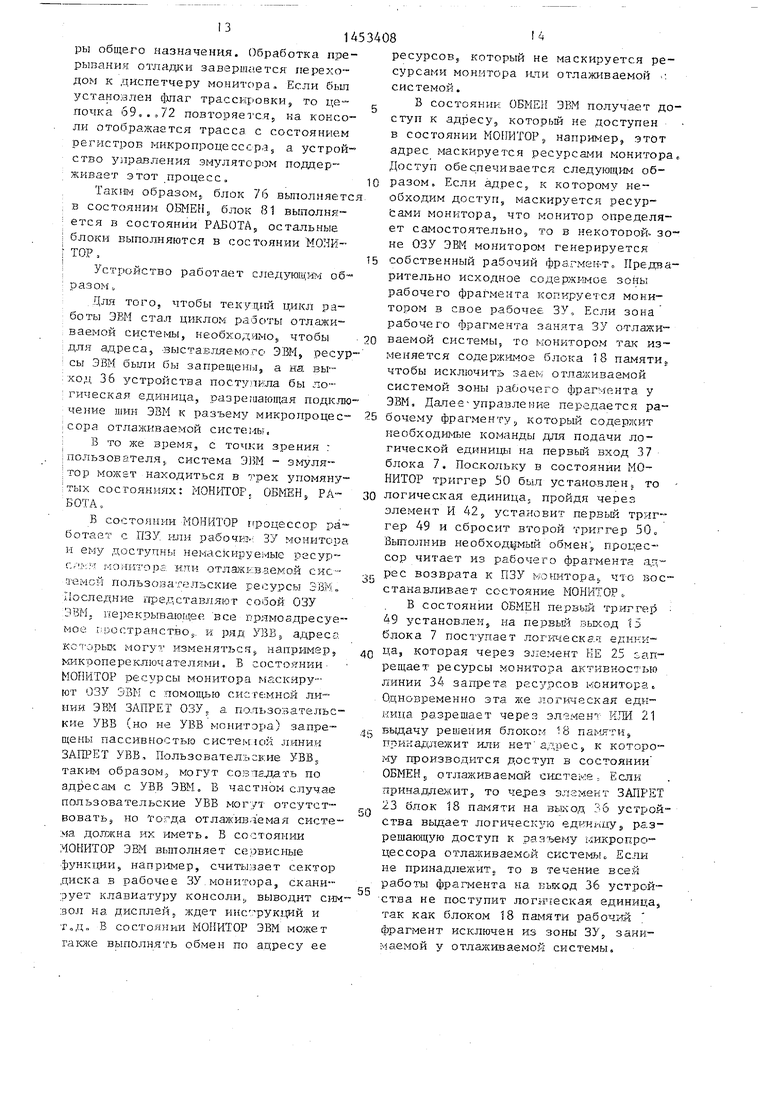

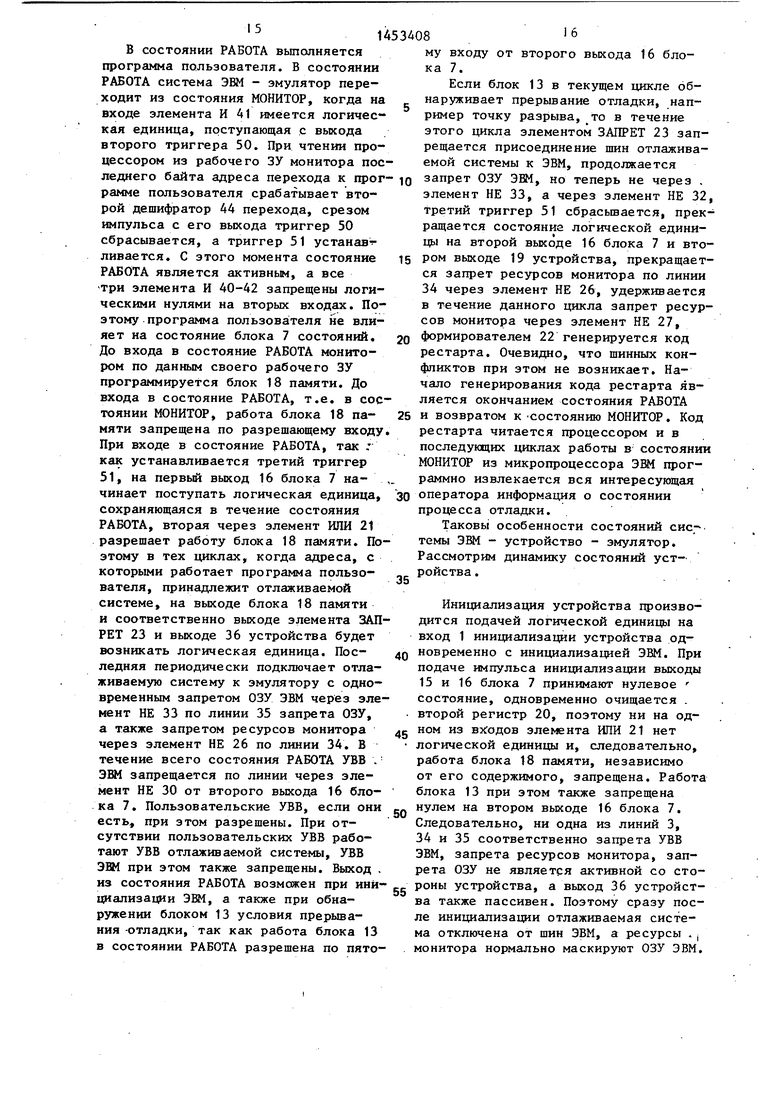

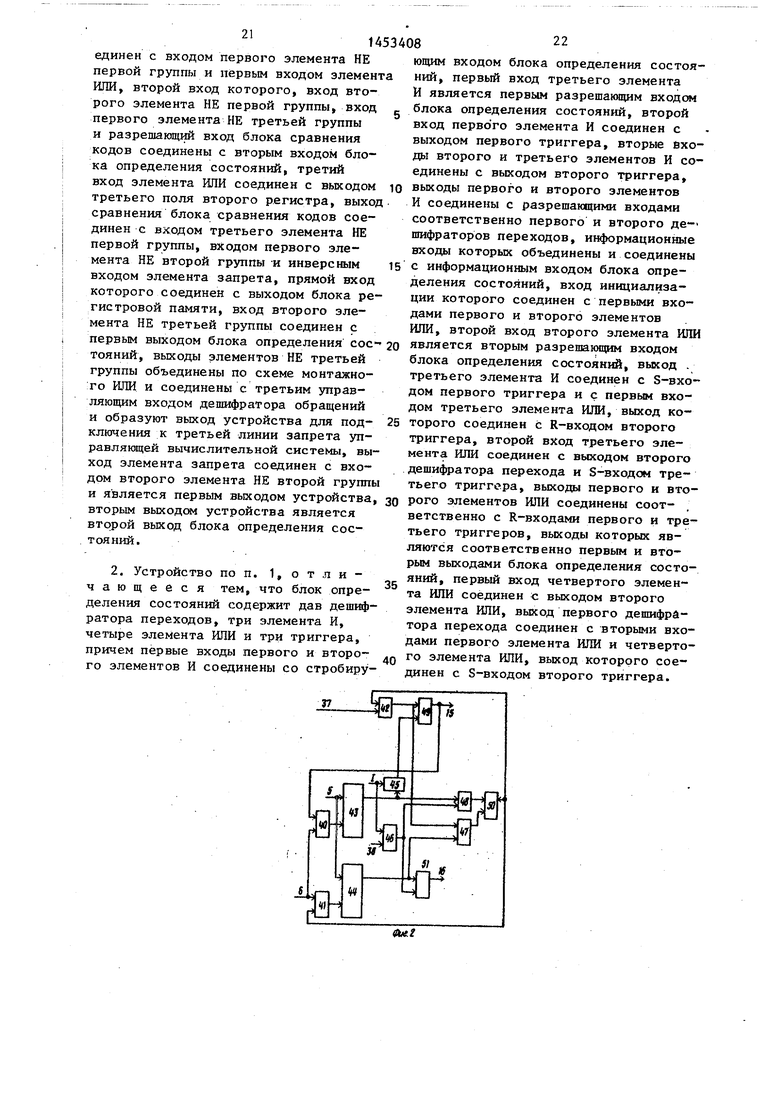

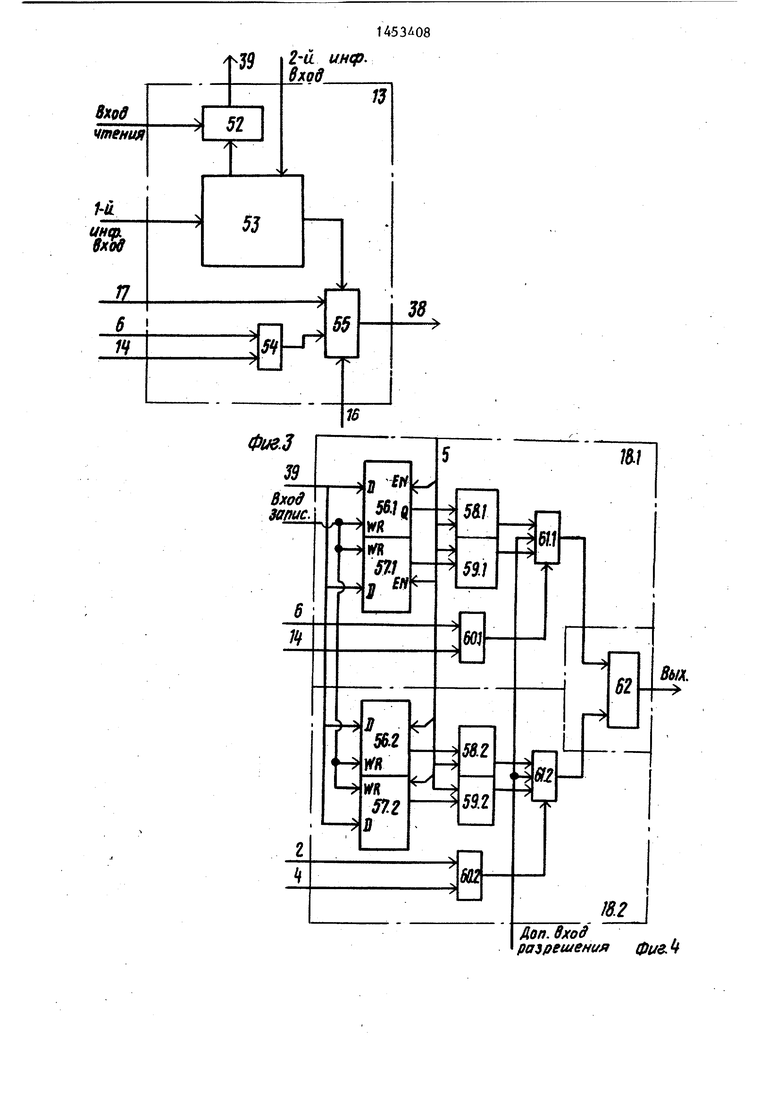

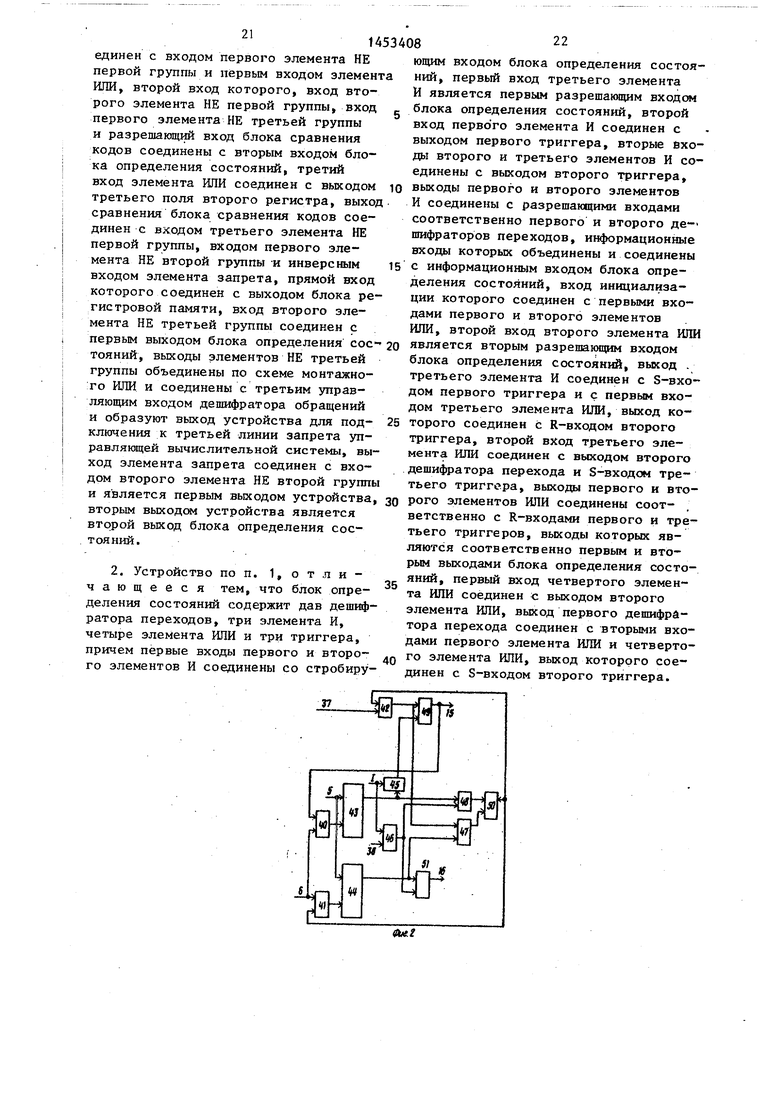

На фиг, 1 представлена функциональная схема устройства для отладки микропроцессорной системы; на фиг.2 - функциональная схема блока определения состояний на фиг. 3 - функциональная схема блока сравнения кодов; на фиг, 4 - функциональная схема блока регистровой памятиJ на фиг. 5 - схема алгоритма работы устройства.

На схеме устройства (фиг. 1) обоз- 2о начены: вход 1 инициализации устройства, линия 2 чтения ввода-вывода управляющей вычислительной системы (УВС), третья линия 3 запрета УВС,

линия 4 записи ввода-вьшода УВС, ад- 25 ищем устройстве (ПЗУ) ЭВм ресная шина 5 УВС, линия 6 чтения па-рии1.1ве JBM.

мяти УВС, блок 7 опредех1ения состоя- первьй регистр 8, дещифратор ,9

5

Блок сравнения кодов ( держит ключ 52, схему 53 кодов, элемент ИЛИ 54, эл

Блок регистровой памят содержит регистры 56.1 и ти нижних границ зон заем 57.1 и 57.2 памяти верхни заема, сумматоры 58.1, 58 59.2, элементы ИЛИ 60.1 и элементы И 61.1 и 61.2, эл 62,

В качестве управляющей льной системы используется

Функциональное назначен турных компонент следующее инициализации устройства п на линия инициализации ЭВМ навливает ЭВМ в состояние, тором ее системный монитор начинает свою работу , т.е. инициализации процессор ЭВ щается к началу програ мы записанной в постоянном за

35

40

НИИ,

обращений, шина 10 данньзх отлаживаемой системы,, адресная шина 11отлаживаемой системы, мультиплексор 12, блок 13 сравнен ия кодов, линия 14 записи памяти УВС, первый выход 15 бло- -. ка определения состояний, второй выход 16 блока определения состояний, линия 17 признака первого цикла ко- i манды yBCs блок 18 регистровой памя- THj второй выход 19 устройства, второй регистр 20, элемент ИЛИ 21, формирователь 22 кода .рестарта, элемент ЗАПРЕТ 23, первая группа 24 элементов НЕ, первый 25, второй 26 и третиз 27 элементы НЕ первой группы, третья группа 28 элементов НЕ,, первьй 29 и второй 30 элементы НЕ третьей группы, вторая группа 31 элементов НЕ, первый 32 и второй 33 элементы НЕ второй группы, первая линия 34 запрета УВС, вторая линия 35 запрета УВС, первьй выход 36 устройства, первьй .37 и второй 38 управлякщие входы блока состояний, шина 39 данных УВС.

Блок определения состояний (фиг.2) содержит первый 40, второй 41 и тий 42 элементы И, первый 43 и второй 44 дешифраторы переходов, первый 45, второй 46, третий 47 и чет- вертьй 48 элементы ИЛИ,, первьй 49, второй-50 и третий 51 триггеры.

Линия 2 чтения устройст вывода (УВВ) активна, если адресов установлен стабиль УВВ, который читается или таться процессором ЭВМ.

Линия 3 залрета УВЗ акт требуется запретить обраще принадлежащим ЭВМ, поэтому и второй 20 регистры, блок являются УВВ, принадлежащи как выбираемые ее монитором

Линия 4 записи УВВ актив на шине 5 адресов установле бильньй адрес УВВ, в которо письюает или будет записьша мацию.

Адресная шина 5 служит д чи адреса запоминакнцего уст (ЗУ) иди УВВ по магистрали Д2 блокам, в том числе к эмуля устройству управления эмуля

Линия 6 чтения активна, шине 5 адресов находится ст адрес ячейки ЗУ, которая чи или будет читаться процессо

Блок 7 определения состо ляется основной структурной той устройства, дискриминир запоминающе.й состояния ЭВМ: ОБМЕН, РАБОТА.

Первьй регистр 8 запомин раммируемые в нем монитором прерывания отладки, наприме са точек разрыва, коды кома

50

55

10

о

5 ищем устройстве (ПЗУ) ЭВм рии1.1ве JBM.

5

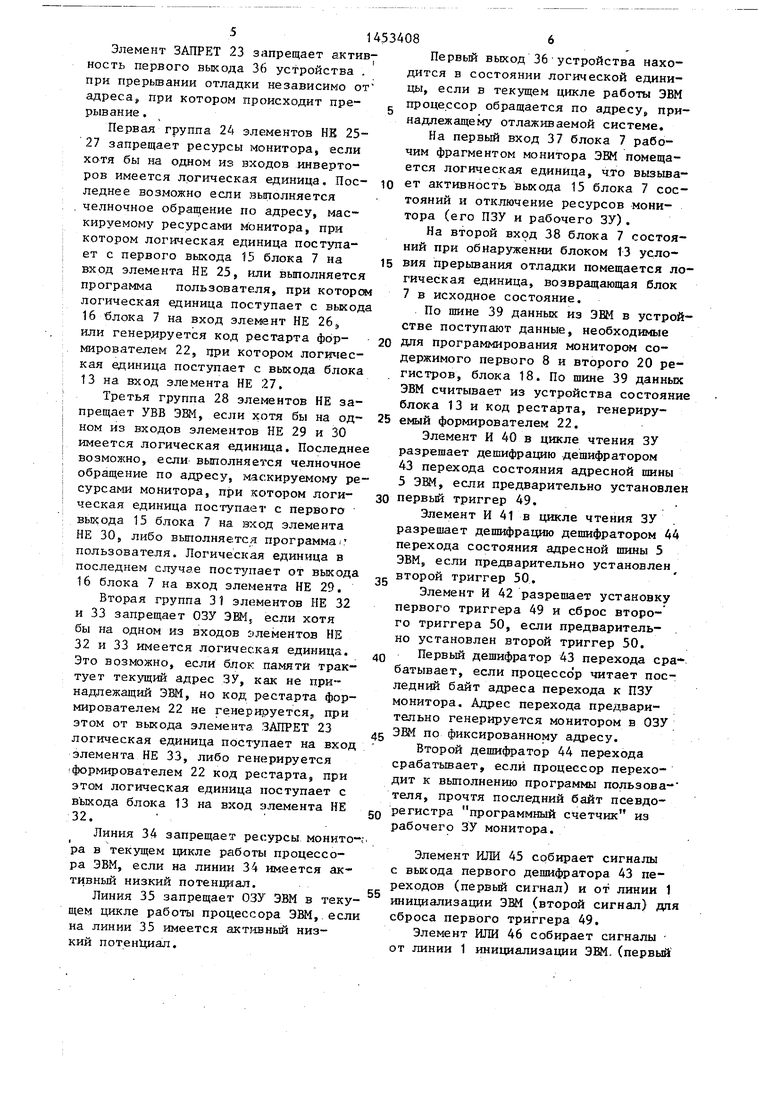

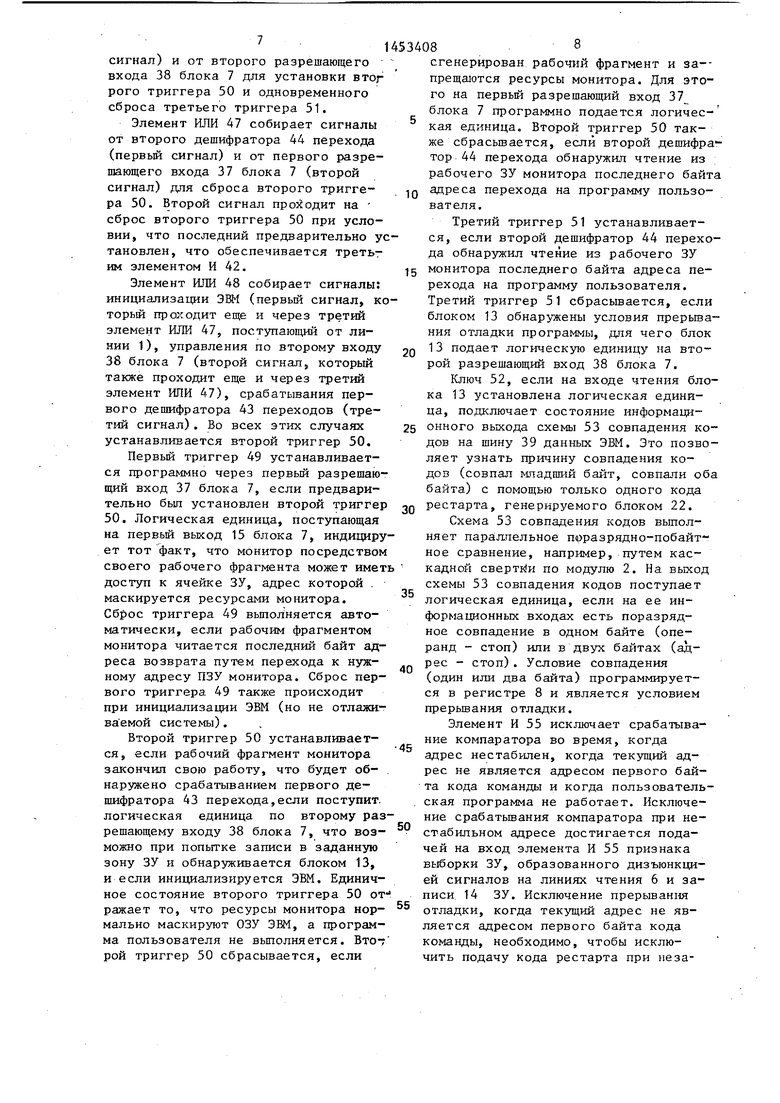

Блок сравнения кодов (фиг. 3) содержит ключ 52, схему 53 совпадения кодов, элемент ИЛИ 54, элемент И 55.

Блок регистровой памяти (фиг. 4) содержит регистры 56.1 и 56.2 памя- ти нижних границ зон заема, регистры 57.1 и 57.2 памяти верхних границ зон заема, сумматоры 58.1, 58.2, 59.1 и 59.2, элементы ИЛИ 60.1 и 60.2, элементы И 61.1 и 61.2, элемент ИЛИ 62,

В качестве управляющей вычислительной системы используется ЭВМ.

Функциональное назначение структурных компонент следующее. К входу инициализации устройства подключена линия инициализации ЭВМ, она устанавливает ЭВМ в состояние, при котором ее системный монитор-отладчик начинает свою работу , т.е. после инициализации процессор ЭВМ обращается к началу програ мы монитора, записанной в постоянном запомина25 ищем устройстве (ПЗУ) ЭВм рии1.1ве JBM.

35

40

-.

Линия 2 чтения устройства ввода- вывода (УВВ) активна, если на шине У адресов установлен стабильньй адрес УВВ, который читается или будет читаться процессором ЭВМ.

Линия 3 залрета УВЗ активна, если требуется запретить обращение к УВВ, принадлежащим ЭВМ, поэтому первый 8 и второй 20 регистры, блоки 13 и 18 являются УВВ, принадлежащими ЭВМ, как выбираемые ее монитором.

Линия 4 записи УВВ активна, если на шине 5 адресов установлен стабильньй адрес УВВ, в которое ЭВМ за- письюает или будет записьшать информацию.

Адресная шина 5 служит для передачи адреса запоминакнцего устройства (ЗУ) иди УВВ по магистрали ЭВМ к ее Д2 блокам, в том числе к эмулятору и к устройству управления эмуляторе.

Линия 6 чтения активна, если на шине 5 адресов находится стабильный адрес ячейки ЗУ, которая читается или будет читаться процессором ЭВМ.

Блок 7 определения состояний является основной структурной компонентой устройства, дискриминирующей и за- запоминающе.й состояния ЭВМ: МОНИТОР ОБМЕН, РАБОТА.

Первьй регистр 8 запоминает программируемые в нем монитором условия прерывания отладки, например, адреса точек разрыва, коды команд, до вы50

55

полнения которых необходимо узнать состояние отлаживаемой программы или системы и т.д. Разрядность, первого регистра 8 может превьшать разрядность шины данных ЭШ, поэтому он может программироваться в несколько приемов.

Шина 10 данных отлаживаемой систетрактрваться процессором ЭВМ как первый байт команды.

Блок 18 регистровой памяти заломи- нает области адресного пространства ЗУ, которые будут заняты отлаживаемой системой. Выход блока 18 может в течение цикла ЭВМ находиться в состоянии логической единицы при условии,

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОФУНКЦИОНАЛЬНОЕ ОТЛАДОЧНОЕ УСТРОЙСТВО ДЛЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2016 |

|

RU2634197C1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1348839A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1425683A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

| Устройство отладки микропрограммных блоков | 1988 |

|

SU1541617A1 |

| Электронная вычислительная машина для ускоренной обработки запросов прерываний | 1988 |

|

SU1621029A1 |

| Устройство для отладки программ | 1988 |

|

SU1654827A1 |

| Устройство для контроля микропроцессорной системы | 1989 |

|

SU1640693A1 |

Изобретение относится к технике автоматизации разработки микропроц ес- сорных систем и предназначено для использования во внутрисхемных эмуляторах. Целью изобретения является упрощение устройства и связанного с ним эмулятора. Устройство содержит дешифратор обращений 9, регистры 8 и 20, мультиплексор 12, блок 13 сравнения кодов, элементы ЗАПРЕТ 23 и ИЛИ 21, , блок 18 регистровой памяти, формирователь 22 кода рестарта, три группы элементов НЕ и блок 7 определения состояний. 1 з.п. ф-лы, 5 Ш1. § (Л с

мы является шиной данных эмулируемого ю текущий адрес ЗУ или УЕВ не при- микропроцессора либо подключена к надлежит ЭВМ и на пятый разрешающий . ней через буфер.вход блока 18 поступает логическая

Шина 11 адресов отлаживаемой системы является шиной адресов эмулируемого микропроцессора либо подключена к ней через буфер.

Шины 1О и 11, если отлаживаемая система физически отсутствует, могут быть подключены к шинам 39 и 5 ЭВМ. При этом работоспособность уст- ройства полностью сохраняется.

Мультиплексор 12 подключает к второму информационному входу блока 13 либо шину 10 данных, либо шину 11 адресов отлаживаемой системы.

Блок 13 сравнивает коды на втором информационном входе и части первого информационного входа; другая часть первого информационного входа определяет типы циклов ЭВМ, в которых может произойти совпадение кодов. Если в текущем цикле заданного типа обнаружено совпадение кодов, то в te- чение такого цикла на выход блока 13 поступает логическая единица. Например, если задана точка разрыва, то, если адрес точки разрыва установлен на шине 5 адресов, причем адрес будет стробироваться в этом случае конъюнкцией сигналов чтения ЗУ и признака первого цикла команды, то блок 13 сработает.

Линия 14 записи ЗУ активна, если на шине 5 адресов находится стабильный адрес ячейки ЗУ, которая читается или будет читаться процессором.

Первый выход 15 блока определения состояний активен, если монитору доступна ячейка ЗУ, маскируемая либо ресурсами монитора, либо ресурсами отлаживаемой системы.

Второй выход 16 блока определения состояний активен, если ЭВМ выполняет программу пользователя.

Линия 17 признака первого цикла команды активна, если на шине 5 адресов находится стабильный адрес г ячейки ЗУ, содержимое которой будет

5

5

0

0

5

0

5

5

единица.

Выход 19 устройства активен, если выполняется программа пользователя. К выходу 19 устройства может быть подключен таймер для прямых замеров быстродействия программ поль- зователя. При этом прерывания отлад- ки не будут влиять на результаты за меров, так как при прерьшании отлад- ки логическая единица с выхода 19 устройства будет автоматически сниматься. Кроме того, выход 19 устрой- ства может использоваться для управН ления трассирукщим ЗУ, входящим в , состав эмулятора или ЭВМ и запоминающим предысторию отладки до ее прерывания с помощью блсука 13.

Второй регистр 20 является регистром управления устройством со сторо-j ны ЭШ. В зависимости от состояния первого выхода второго регистра 20 к второму информационному входу бло- ка 13 подключается либо шина 10 данных, либо шина 11 адресов отлаживаег мой системы. Логической единицей, поступающей с второго выхода регистра 20, блок 7 может быть переведен в состояние ОБМЕН с отключением ресур-| сов монитора. Логической единицей на третьем выходе второго регистра 20 программно разрешается через элемент ИЛИ 21 срабатывание блока 18, если это не разрешено по другим двум входам элемента ИЛИ 21 от выходов 15 и 16 блока 7.

Элемент PfflH 21 собирает сигналы, разрешающие по пятому входу разрешения срабатывание блока 18 регистровой памяти.

Формиров.атель 22 кода рестарта i на шину 39 данных один из кодов рестарта, зарезервированных в ЭВМ для обработки прерываний отладки программы, если на вход формирователя 22 поступает логическая единица.

10

1453408

Элемент ЗАПРЕТ 23 запрещает активность первого выхода 36 устройства . при прерьшании отладки независимо от адреса, при котором происходит прерывание .

Первая группа 24 элементов НЕ 25- 27 запрещает ресурсы монитора, если хотя бы на одном из входов инверторов имеется логическая единица. Последнее возможно если выполняется челночное обращение по адресу, маскируемому ресурсами монитора, при котором логическая единица поступает с первого выхода 15 блока 7 на вход элемента НЕ 25, или выполняется программа пользователя, при которая логическая единица поступает с выхода 16 блока 7 на вход элемент НЕ 26, или генерируется код рестарта фор- мирователем 22, цри котором логвдес- кая единица поступает с выхода блока 13 на вход элемента НЕ 27.

Третья группа 28 элементов НЕ за

ппршярт VRK -эта/; wiuRa и и КОД рестарта

прещает УВВ ЭШ, если хотя бы на од- 25 емый формирователем 22

ном из ВХОЛОВ чгтрмоитг.п Ни- OQ „ ол i woai слей д .

Первый выход 36 уст дится в состоянии логи цы, если в текущем цик g процессор обращается п надлежащему отлаживаем

На первый вход 37 б чим фрагментом монитор ется логическая единиц ет активность выхода 15 тояний и отключение рес тора (его ПЗУ и рабочег

На второй вход 38 бл ний при обнаружении бло 15 ВИЯ прерывания отладки гическая единица, возвр 7 в исходное состояние.

По шине 39 данных из стве поступают данные, 20 для программирования мо держимого первого 8 и в гистров, блока 18. По ш ЭВМ считывает из устрой блока 13 и код рестарта

ном из входов элементов НЕ 29 и 30 имеется логическая единица. Последнее возможно, если выполняется челночное обращение по адресу, маскируемому ресурсами монитора, при котором логическая единица поступает с первого выхода 15 блока 7 на вход элемента НЕ 30, либо выполняется программа. пользователя. Логическая единица в

rzr/-n :/«vs°- 3. О -;;«. Гзт

16 блока 7 на вход элемента НЕ 29.

Вторая группа 31 элементов НЕ 32 и 33 запрещает ОЗУ ЭШ, если хотя бы на одном из входов элементов НЕ 32 и 33 имеется логическая единица. Это возможно, если блок памяти трактует текущий адрес ЗУ, как не принадлежащий Эт, но код рестарта формирователем 22 не генерируется, при этом от вькода элемента ЗАПРЕТ 23 логическая единица поступает на вход элемента НЕ 33, либо генерируется iформирователем 22 код рестарта, при этом логическая единица поступает с в ыхода блока 13 на вход элемента НЕ 32.

Линия 34 запрещает ресурсы монито-; ра в текущем цикле работы процессора ЭВМ, если на линии 34 имеется активный низкий потенциал.

Линия 35 запрещает ОЗУ ЭВМ в текущем цикле работы процессора ЭВМ, если на линии 35 имеется актг-шный низкий потенциал.

Элемент И 40 в цикле разрешает дешифрацию де 43 перехода состояния а 5 ЭШ, если предварител 30 первьй триггер 49.

Элемент И 41 в цикле разрешает дешифрацию деш перехода состояния адрес ЭВМ, если предварительно

Элемент И 42 разрешае первого триггера 49 и сб го триггера 50, если пре но установлен второй три

40 Первый дешифратор 43 батывает, если процессор ледний байт адреса перех монитора. Адрес перехода тельно генерируется мони

45 ЭВМ по фиксированному ад

Второй дешифратор 44 срабатьшает, если процес дит к вьшолнению програм теля, прочтя последний б 50 регистра программный сч рабочего ЗУ монитора.

Элемент ИЖ 45 собира с выхода первого дешифра gg реходов (первьй сигнал) инициализации ЭВМ (второй сброса первого триггера

Элемент ИЛИ 46 собирае от линии 1 инициализации

0

wiuRa и и КОД рестарта

5 емый формирователем 22

Первый выход 36 устройства находится в состоянии логической единицы, если в текущем цикле работы ЭВМ g процессор обращается по адресу, принадлежащему отлаживаемой системе.

На первый вход 37 блока 7 рабочим фрагментом монитора ЭШ помещается логическая единица, что вызьша- ет активность выхода 15 блока 7 состояний и отключение ресурсов монитора (его ПЗУ и рабочего ЗУ).

На второй вход 38 блока 7 состояний при обнаружении блоком 13 усло- 5 ВИЯ прерывания отладки помещается логическая единица, возвращающая блок 7 в исходное состояние.

По шине 39 данных из ЭВМ в устройстве поступают данные, необходимые 0 для программирования монитором содержимого первого 8 и второго 20 регистров, блока 18. По шине 39 данных ЭВМ считывает из устройства состояние блока 13 и код рестарта, генериру 25 емый формирователем 22

i woai слей д .

Элемент И 40 в цикле чтения ЗУ разрешает дешифрацию дешифратором 43 перехода состояния адресной шины 5 ЭШ, если предварительно установлен 30 первьй триггер 49.

Элемент И 41 в цикле чтения ЗУ разрешает дешифрацию дешифратором 44 перехода состояния адресной шины 5 ЭВМ, если предварительно установлен

О -;;«. Гзт

Элемент И 42 разрешает установку первого триггера 49 и сброс второ- го триггера 50, если предварительно установлен второй триггер 50.

Первый дешифратор 43 перехода срабатывает, если процессор читает последний байт адреса перехода к ПЗУ монитора. Адрес перехода предварительно генерируется монитором в ОЗУ

ЭВМ по фиксированному адресу.

Второй дешифратор 44 перехода срабатьшает, если процессор переходит к вьшолнению программы пользова- теля, прочтя последний байт псевдо- регистра программный счетчик из рабочего ЗУ монитора.

Элемент ИЖ 45 собирает сигналы с выхода первого дешифратора 43 пе- реходов (первьй сигнал) и от линии 1 инициализации ЭВМ (второй сигнал) для сброса первого триггера 49.

Элемент ИЛИ 46 собирает сигналы т линии 1 инициализации ЭВМ. (первый

7 ,

сигнал) и от второго разрешающего входа 38 блока 7 для установки втог рого триггера 50 и одновременного сброса третьего триггера 51.

Элемент ИЛИ 47 собирает сигналы от второго дешифратора 44 перехода (первьй сигнал) и от первого разрешающего входа 37 блока 7 (второй сигнал) для сброса второго триггера 50. Второй сигнал на - сброс второго триггера 50 при условии, что последний предварительно установлен, что обеспечивается третьим элементом И 42.

Элемент ИЛИ 48 собирает сигналы: инициализации ЭШ (первый сигнал, который проходит еще и через третий элемент ИЛИ 47, поступающий от линии 1), управления по второму входу 38 блока 7 (второй сигнал, который также проходит еще и через третий элемент ИЛИ 47), срабатывания первого дешифратора 43 переходов (тре- Т1-1Й сигнал) . Во всех этих случаях устанавливается второй триггер 50.

Первьй триггер 49 устанавливается программно через первьш разрешающий вход 37 блока 7, если предварительно бып установлен второй триггер 50. Логическая единица, поступающая на первьй выход 15 блока 7, индицирует тот факт, что монитор посредством своего рабочего фрагмента может иметь доступ к ячейке ЗУ, адрес которой . маскируется ресурсами монитора. Сброс триггера 49 вьшолняется автоматически, если рабочим фрагментом монитора читается последний байт адреса возврата путем перехода к нужному адресу ПЗУ монитора. Сброс первого триггера 49 также происходит при инициализации ЭВМ (но не отлажн- ва емой системы).

Второй триггер 50 устанавливается, если рабочий фрагмент монитора закончил свою работу, что будет об- , наружено срабатыванием первого дешифратора 43 перехода,если поступит. логическая единица по второму раз-

10

15

20

сгенерирован рабочий фрагмент и запреща отся ресурсы монитора. Для это го на первьй разрешающий вход 37 блока 7 программно подается логичес кая единица. Второй триггер 50 также сбрасывается, если второй дешифр тор 44 перехода обнаружил чтение из рабочего ЗУ монитора последнего 6afi адреса перехода на программу пользо вателя.

Третий триггер 51 устанавливается, если второй дешифратор 44 перех да обнаружил чтение из рабочего ЗУ монитора последнего байта адреса пе рехода на программу пользователя. Третий триггер 51 сбрасьшается, есл блоком 13 обнаружены условия прерьш ния отладки программы, для чего бло 13 подает логическую единицу на вто рой разрешающий вход 38 блока 7.

Ключ 52, если на входе чтения бл ка 13 установлена лог гческая единица, подключает состояние информационного выхода схемы 53 совпадения к дов на шину 39 данных ЭВМ. Это позво ляет узнать причину совпадения кодов (совпал младший байт, совпали о байта) с помощью только одного кода рестарта, генерируемого блоком 22.

Схема 53 совпадения кодов вьтол- няет пара;л:пельное поразрядно-побайтное сравнение, например, путем каскадной свертки по модулю 2. На выход схемы 53 совпадения кодов поступает логическая единица, если на ее информационных входах есть поразрядное совпадение в одном байте (операнд - стоп) или в двух байтах (адрес - стоп). Условие совпадения (один или два байта) программируется в регистре 8 и является условием прерьшания отладки.

Элемент И 55 исключает срабатывание компаратора во время, когда адрес нестабилен, когда текущий адрес не является адресом первого байта кода команды и когда пользователь ская программа не работает. Исключение срабатьшания компаратора при не25

30

35

40

45

решающему входу 38 блока 7, что воз- стабильном адресе достигается подаможно при попытке записи в заданную зону ЗУ и обнаруживается блоком 13, и если инициализируется ЭВМ. Единичное состояние второго триггера 50 от- ражает то, что ресурсы монитора нор- мально маскируют ОЗУ ЭШ, а программа пользователя не выполняется. Вто-; рой триггер 50 сбрасывается, если

10

15

20

сгенерирован рабочий фрагмент и за- преща отся ресурсы монитора. Для этого на первьй разрешающий вход 37 блока 7 программно подается логичес- кая единица. Второй триггер 50 также сбрасывается, если второй дешифратор 44 перехода обнаружил чтение из рабочего ЗУ монитора последнего 6afiTa адреса перехода на программу пользователя.

Третий триггер 51 устанавливается, если второй дешифратор 44 перехода обнаружил чтение из рабочего ЗУ монитора последнего байта адреса перехода на программу пользователя. Третий триггер 51 сбрасьшается, если блоком 13 обнаружены условия прерьша- ния отладки программы, для чего блок 13 подает логическую единицу на второй разрешающий вход 38 блока 7.

Ключ 52, если на входе чтения блока 13 установлена лог гческая единица, подключает состояние информационного выхода схемы 53 совпадения кодов на шину 39 данных ЭВМ. Это позволяет узнать причину совпадения кодов (совпал младший байт, совпали оба байта) с помощью только одного кода рестарта, генерируемого блоком 22.

Схема 53 совпадения кодов вьтол- няет пара;л:пельное поразрядно-побайтное сравнение, например, путем каскадной свертки по модулю 2. На выход схемы 53 совпадения кодов поступает логическая единица, если на ее информационных входах есть поразрядное совпадение в одном байте (операнд - стоп) или в двух байтах (адрес - стоп). Условие совпадения (один или два байта) программируется в регистре 8 и является условием прерьшания отладки.

Элемент И 55 исключает срабатывание компаратора во время, когда адрес нестабилен, когда текущий адрес не является адресом первого байта кода команды и когда пользовательская программа не работает. Исключение срабатьшания компаратора при не25

30

35

40

45

чей на вход элемента И 55 признака выборки ЗУ, образованного дизъюнкцией сигналов на линиях чтения 6 и записи 14 ЗУ. Исключение прерыван1ся отладки, когда текущий адрес не является адресом первого байта кода команды, необходимо, чтобы исключить подачу кода рестарта при неза 145340810

чение сп 5° ° / Г адресов таковой действителен и,

работаюшей Дополнительней

необхоЗ пользователявход разрешения блока 18 памяти. Это

необходимо для исключения случайногосправедливо и для адреса УВВ, но осурываГя пп -«--ПС условий пре- ществляется вторым подблоков памяти.ного мон:;тооГ Блок-схема алгоритма работы yetп г ройства совместно с ЭВМ представле.ра г-н е зоГзГ::™™. ,„ :г„л:™ ; - -вается старший байт аяоеса Гипи гямAT

цессором ЭВМ. последней не принадле-, я в заеме находящемужат. В регистре 57.1 хранения верх-(./, R,

ней границы занимаемой зоны ЗУ за-,„ выполняться обмен по

писывается старший байт адреса (или который не маскируется ресур:Г.: . i™ s ,.

торого адреса, генерируемые микропро- димости изменяет содержимое блока

цессором ЭВМ, последней не принадле-памяти так, чтобы исключить такое

жат. В регистре 57.1 хранения верх-попадание, затем на третьем входе ней границы занимаемой зону ЗУ за-элемента ИЛИ 21 монитор устанавливает

письшается такая же информация об25 логическую единицу, чем разрешается

адресе, начинал с которого адреса,работа блока 18 памяти без участия

генерируемые микропроцессором ЭВМ,блока 7; принадпежат последней.65 - изменение границ;

Вькоды сумматоров 58.1, 59.1, 58.266 - вьтолнение директивы, не

и 39.2 являются выходами переносазо содержащей обмена, либо содержащей

и имеют один разряд. На выход сум.а-обмен с незамаскированным адресом;

тора Ь8.1 поступает логическая еди-67 - на ЭВМ нажимают кнопку ница, если на шине 5 .адресов установ- сброс, при этом активизируется лилен адрес ЗУ, величина которого рав-ния 1 инициализации устройства тригна или превышает нижнюю границу за-геры 49 и 51 сбрасываются, а триггер

ема. Аналогично на выход сумматора 50 устанавливается в единицу;

рес ЗУ, величина которого равна илиустройства и переходит к ожиданию

меньше верхней границы заема. Чтобыдиректив. В этом состоянии на вькожГ пГги соответствую-дах .15 и 16 блока 7 находятся нули,

щих регистрах программируется зна-„а третьем входе элемента ИЛИ 21 начение границ в дополнительных кодах.ходится логический нуль, следовательПоскольку выходы пары сумматоров сое-но, работа блока 18 памяти запрещементГи бГГ н f ° ° разрешающем входе.

мента И 61.1, необходимым условиемРабота блока 13 запрещена нулём на

ло™Г™- элемента И 61.1вьосоде 16 блока 7. Заемы памяти у отлогическои единицы является попа-лаживаемой системы невозможны;

дание текущего адреса ячейки ЗУ меж-69 - диспетчер монитора скйнируДУ запрограммированными границами ли-ет консоль и ждет полного ввода ди- бо равенство одной из границ. рективы. Пока последняя не введена,

Элемент Ш1И 60.1 исключает слу-переход к .блоку 70 невозможен;

чайную генерацию условия заема зоны70 - проверяется, является ли ввеЗУ, если установленный на шине ад-денная директива передачей управлерес ЗУ нестабилен, либо на шине 5 на-ния программе пользователя; ходится адрес УВВ. Следовательно, на 55 71 - директива не передает управвыходе элемента И 61.1 появится сиг-ления программе пользователя, пронал заема адресного пространства ЗУверяется, содержит ли введенная диу отлаживаемой системы, если на шинеректива обмен с ячейкой ЗУ или УВВ72- диерктива содержит обмен, например, необходимо заменить содержимое ячейки или порта, проверяется, не замаскрфован ли адрес ресурсами монитора;

73- адрес, по которому будет обмен, замаскирован ресурсами монитора, следовательно, необходимо генерировать рабочий фрагмент (РФ), проверяется, не будет ли находиться участок ОЗУ с РФ в заеме во время выполнения РФ;

7Д - участок, где будет генерироваться РФ, находится в заеме у отла- 15 Предварительно в псевдорегистр программный счетчик, находящийся в рабочем ОЗУ монитора, загружается стартовый адрес программы пользователя, который может быть любым. Адрес

живаемой системы, необходимо исключить этот заем, поскольку не известно, что в этом участке отлаживаемая система имеет (и имеет ли вообще) исправное ОЗУ. Блок 18 памяти перепрограммируется так, чтобы исключить заем участка РФ, для этого верхняя или нижняя граница в блоке 18 памяти сдвигается соответствующим образом;

75- генерируется РФ и передается ему управление;

76- выполняется РФ. Выполнение РФ начинается с подачи логической единицы на линии 37 устройства путем соответствующего программирования - второго регистра 20. Триггер 51 устанавливается, а триггер 50 сбрасывается. Возникает состояние ОБМЕН. Работа блока 13 запрещена, а работа блока 18 памяти разрешена. При обмене с ячейкой ЗУ, веди адрес ее находится в заеме, блок 18 памяти срабатывает. Поскольку элемент ЗАПРЕТ 23

не блокирует линию 36, то происходит 40 прерывания отладки, так как срабо- обмен по адресу, который относится тает элемент ЗАПРЕТ 23. Одновремен- к отлаживаемой системе. Одновремен- но вместо очередного первого байта но по адресу, относящемуся к ЭВМ, ни- команды пользовательской программы чего не изменяется, так как он бло- ка шину 39 данных блок 22 поместит кирован через элемент 33 и линию зап- g код рестарта, а в конце цикла посред- рета ЗУ. Если адрес не находится в ством линии 38 триггер 50 установит- заеме, то наоборот, процессор ЭВМ по- ся, а триггер 51 сбросится. Процеслучает доступ не к ЗУ отлаживаемой системы, а к ЗУ ЭВМ. Выполнение РФ j кончается чтением адреса возврата к некоторому адресу монитора. Последний постоянен и не зависит от директивы, содержащей обмен. При чтении последнего байта адреса возврата срабатывает дешифратор 43 блока 7, чем сбрасьшается триггер 49 и устанавливается триггер 50, т.е. возвращается состояние МОНИТОР к моменту чтения.кода команды из ПЗУ монитора;

77- проверяется, был ли перепрограммирован блок 18 памяти. Если да, то исходное содержимое восстанавливается и управление передается диспетчеру 69 монитора;

78- директива содержит передачу управления программе пользователя, проверяется, задавались ли в директиве условия прерывания отладки;

79- будет прерывание отладки, загружаются условия в регистр 8 устройства;

80- пуск прог раммы пользователя.

Предварительно в псевдорегистр программный счетчик, находящийся в рабочем ОЗУ монитора, загружается стартовый адрес программы пользователя, который может быть любым. Адрес

псевдорегистра и программный счетчик постоянен. При чтении последнего байта этого псевдорегистра сра- батьшает дешифратор 44, трип ер 50 сбрасывается, а триггер 51 устанавливается. К моменту обращения процессора к стартовому адресу устанавли- вается состояние РАБОТА, на линию 16 поступает логическая единица, на линии 15 сохраняется логический нуль. Это разрешает piiDoTy блока 13 и блока 18 памяти.

В- тех циклах, где текущий адрес принадлежит не ЭВМ, а отлаживаемой системе, контакты разъема эмулятора будут подключаться к соответствующим шинам ЭВМ при незапрещенных сра батываниях блока 18 памяти. Такого подключения не произойдет, если блок 13 в текущем цикле обнаружит условия

50

55

сор прочтет этот код рестарта и передаст согласно ему управление монитору. Вьшолнение программы 81 прекратится;

82 - обработчик прерьшания отладки, на который по коду рестарта перейдет монитор. При выполнении рестарта из микропроцессора ЭВМ содержимое рестарта программного счетчика извлекается и помещается в упомянутый псевдорегистр программный счетчик. Далее извлекаются все регист13

ры общего назначения. Обработка пррывания отладки завершается: переходом к диспетчеру монитора. Если бы установлен таг трассировки, то цепочка 69..,72 повторяется, ка консли отображается трасса с состояние регистров микропроцессора, а устроство управления эмулятором поддер-- жквает этот процесс.

Такш образом,, блок 76 вьтолияе в состоянии ОБМЕН, блок 81 выполняется в состоянии РАБОТА, остальные блоки выполняются в состоянии МОЧИ ТОР.

Устройство работает следующиг- об ; разом.

Для того, чтобы текулдш ра боты ЭВМ стал циклом работы ваемой системы, необход лмо, чтобы для яцреса, -ззыставляемого ЭВМ, ресу ; сы ЭВМ бьши бы запрещены, а на ход 36 устройства поступила бы ло- ; гическая единица, разрешающая подк,л чение шин ЭВМ к разъему микропроцес ;сора отлаживаемой системы, : В то же время, с точки зрения г i пользователя,, система - эмуля- ргор может находиться в трех упомяну :тых состояниях: МОНИТОР, ОБМЕН РА-БОТА.

Б состоянии МОНИТОР ггроцессор работает с ПЗЗ или рабочк ЗУ монитор и ему доступнЕ. немаскируемые расур-- cpi-M могнп ора или отл.ажклзаемой сие- а емсй пользовательские ресурсы ЗБМ,. 11оследние представляют собой ОЗУ ЭйМ. перакрываюгдее все прямоадресуе мое :н:,остранство,. и ряд УВВ адреса ксторьпс могут изменяться5 например, К -1кропереключателями. В состоянии. МОНИТОР ресурсы монитора мг скиру- ют ОЗУ УВМ с помоццэю сист :мной линии ЭВМ ЗАПРЕТ ОЗУ, а пользовательские УВВ (но не УВВ монитора) запре- пассивностью системной линии ЗАШЛЕТ УВВ, Пользовательские УВВ, таким образомJ могут соваздтдть по адресам с УВВ ЭВМ. В частном случае пользовательские УВВ могут отсутствовать, но то;гда отлаживаемая систе- а догокна их иметь. В состоянии МОНИТОР ЭВМ выполняет сервисные функции, например, считълзает сектор диска в рабочее ЗУ. монитора, скггни- рует клавиатуру консоли,, выводит снч вол на дисплей, ждет инструкций и т,д„ В состоянии МОНИТОР ЭВМ может также выполнять обмен по адресу ее

ресурсов, который не маскируется ресурсами монитора или отлаживаемой .: системой.

g В состоянии ОБМЕН ЭВМ получает доступ к адресу, которьй не доступен в состоянии МОНИТОР, например, этот адрес маскируется ресурса1 1и монитора. Доступ обеспечивается следующим об10 разом. Если адрес, к которому необходим доступ, маскируется ресур- Ьами монитора, что монитор определяет самостоятельно, то в некоторой, зоне ОЗУ ЭВМ монитором генерируется

15 собственный рабочий фрагмен-т. Предварительно исходное содерхимое зоны рабочего фрагмента копируется монитором в свое рабочее ЗУ, Если зона рабочего фрагмента занята ЗУ отлажи20 ваемой системы, то монитором так изменяется содержимое блока 18 памяти, чтобы исключить заем отла;киваемой системой зоны рабочего фрагмента у ЭВМ, Дапее-упра) передается ра35 бочему фрагменту, которьш содержит необходим1з1е команды для подачи логической едини1№1 на первьш вход 37 блока 7, Поскольку в состоянии МОНИТОР триггер 50 был установлен,

то

0 логическая единица, пройдя через

элемент И 42, установит первьй триггер 49 и сбросит второй триггер 50„ Вьтолнив необход4|мьй обмен, процессор читает из рабочего фрагмента ад- . рее возврата к ПЗУ монитора что восстанавливает состояние МОНИТОР,

В состоянии ОБМЕН перзьй триггер : 49 установлен, на первьпл выход 15 блока 7 поступает логг-иескэл едини- 0 ца, которая через элемент НЕ 25 запрещает ресурсы монитора активностью линии 34 запрета ресурсов монитора Одновременно эта. же логическая единица разрешает через элемент ЕЛИ 21 5 выдачу решения блоком 18 ,

принадлежит илк нет адрес, к которому производится доступ в состоянии ОБМЕН, отлаживаемой сш;те;ч1е, Еслк нрннад/1ежит,, то через элзмент ЗАПРЕТ 23 блок 18 на выход 36 устройства вьщает логическую едкниыуз разрешающую доступ к разъему ьшкропро- цессора отлалсивавлмой системьи Если не принадлел ит то в течение всегй работы фрагмента на 36 устройства не поступит логическая единица, так как блоком 18 памяти рабочий ; фрагмент исключен из зоны ЗУ, занимаемой у отлаживаемой системы.

0

5

В состоянии РАБОТА выполняется программа пользователя. В состоянии РАБОТА система ЭВМ - эмулятор переходит из состояния МОНИТОР, когда на входе элемента И 41 имеется логическая единица, поступающая с выхода второго триггера 50. При чтении процессором из рабочего ЗУ монитора поеледнего байта адреса перехода к прог- ю запрет ОЗУ ЭВМ, но теперь не через

20

25

рамме пользователя срабатывает второй дешифратор 44 перехода, срезом импульса с его выхода триггер 50 сбрасывается, а триггер 51 устанавт- ливается. С этого момента состояние РАБОТА является активным, а все -три элемента И 40-42 запрещены логическими нулями на вторых входах. Поэтому программа пользова теля не влияет на состояние блока 7 состояний. До входа в состояние РАБОТА монитором по данным своего рабочего ЗУ программируется блок 18 памяти. До входа в состояние РАБОТА, т.е. в состоянии МОНИТОР, работа блока 18 памяти запрещена по разрешающему входу. При входе в состояние РАБОТА, так . как устанавливается третий триггер 51, на первый выход 16 блока 7 начинает поступать логическая единица, сохраняющаяся в течение состояния РАБОТА, вторая через элемент ИЛИ 21 разрешает работу блока 18 памяти. Поэтому в тех циклах, когда адреса, с которыми работает программа пользователя, принадлежит отлаживаемой системе, на выходе блока 18 памяти и соответственно выходе элемента ЗАПРЕТ 23 и выходе 36 устройства будет возникать логическая единица. Пос- 0 ледняя периодически подключает отлаживаемую систему к эмулятору с одновременным запретом ОЗУ ЭВМ через элемент НЕ 33 по линии 35 запрета ОЗУ, а также запретом ресурсов монитора через элемент НЕ 26 по линии 34. В течение всего состояния РАБОТА УВВ . ЭВМ запрещается по линии через элемент НЕ 30 от второго выхода 16 блока 7. Пользовательские УВВ, если они

элемент НЕ 33, а через элемент НЕ 3 третий триггер 51 сбрасьшается, пре ращается состояние логической едини на второй выходе 16 блока 7 и вт 15 ром выходе 19 устройства, прекращае ся запрет ресурсов монитора по лини 34 через элемент НЕ 26, удерживаетс в течение данного цикла запрет ресу сов монитора через элемент НЕ 27, формирователем 22 генерируется код рестарта. Очевидно, что шинных конфликтов при этом не возникает. Начало генерирования кода рестарта яв ляется окончанием состояния РАБОТА и возвратом к -состоянию МОНИТОР. Код рестарта читается процессором и в последующих циклах работы в состояни МОНИТОР из микропроцессора ЭШ программно извлекается вся интересующая оператора информация о состоянии процесса отладки.

Таковы особенности состояний системы ЭШ - устройство - эмулятор. Рассмотрим динамику состояний устройства .

30

35

45

50

Инициализация устройства производится подачей логической единицы на вход 1 инициализации устройства одновременно с инициализацией ЭВМ. При подаче импульса инищсализации выходы 15 и 16 блока 7 принимают нулевое состояние, одновременно очищается . второй регистр 20, поэтому ни на одном из вх одов элемента ИЛИ 21 нет логической единицы и, следовательно, работа блока 18 памяти, независимо от его содержимого, запрещена. Работ блока 13 при этом также запрещена нулем на втором выходе 16 блока 7. Следовательно, ни одна из линий 3, 34 и 35 соответственно запрета УВВ ЭВМ, запрета ресурсов монитора, запрета ОЗУ не является активной со сто роны устройства, а выход 36 устройст ва также пассивен. Поэтому сразу пос ле инициализации отлаживаемая система отключена от шин ЭВМ, а ресурсы . монитора нормально маскируют ОЗУ ЭВМ

есть, при этом разрешены. При отсутствии пользовательских УВВ работают УВВ отлаживаемой системы, УВВ ЭВМ при этом также запрещены. Выход , из состояния РАБОТА возможен при инициализации ЭВМ, а также при обнаружении блоком 13 условия прерывания -отладки, так как работа блока 13 в состоянии РАБОТА разрешена по пятому входу от второго выхода 16 блока 7.

Если блок 13 в текущем цикле обнаруживает прерьшание отладки, например точку разрыва, то в течение этого цикла элементом ЗАПРЕТ 23 запрещается присоединение шин отлаживаемой системы к ЭВМ, продолжается

запрет ОЗУ ЭВМ, но теперь не через

элемент НЕ 33, а через элемент НЕ 32, третий триггер 51 сбрасьшается, прекращается состояние логической едини- на второй выходе 16 блока 7 и вто- ром выходе 19 устройства, прекращается запрет ресурсов монитора по линии 34 через элемент НЕ 26, удерживается в течение данного цикла запрет ресурсов монитора через элемент НЕ 27, формирователем 22 генерируется код рестарта. Очевидно, что шинных конфликтов при этом не возникает. Начало генерирования кода рестарта является окончанием состояния РАБОТА и возвратом к -состоянию МОНИТОР. Код рестарта читается процессором и в последующих циклах работы в состоянии МОНИТОР из микропроцессора ЭШ программно извлекается вся интересующая оператора информация о состоянии процесса отладки.

Таковы особенности состояний системы ЭШ - устройство - эмулятор. Рассмотрим динамику состояний устройства .

0

5

0

5

Инициализация устройства производится подачей логической единицы на вход 1 инициализации устройства одновременно с инициализацией ЭВМ. При подаче импульса инищсализации выходы 15 и 16 блока 7 принимают нулевое состояние, одновременно очищается . второй регистр 20, поэтому ни на одном из вх одов элемента ИЛИ 21 нет логической единицы и, следовательно, работа блока 18 памяти, независимо от его содержимого, запрещена. Работа блока 13 при этом также запрещена нулем на втором выходе 16 блока 7. Следовательно, ни одна из линий 3, 34 и 35 соответственно запрета УВВ ЭВМ, запрета ресурсов монитора, запрета ОЗУ не является активной со стороны устройства, а выход 36 устройства также пассивен. Поэтому сразу после инициализации отлаживаемая система отключена от шин ЭВМ, а ресурсы . , монитора нормально маскируют ОЗУ ЭВМ.

1 7

Устройство нормсшьио функционирует даже тогда, когда все адресное пространство ЗУ принадлежит не ЭВМ, а отлаживаемой системе. Зоны ЗУ, принадлежащие отлаживаемой системе„ ука- .зываются оператором специальным инструкциями монитора и записываются в рабочее ЗУ монитора.

Пусть оператором задана инструкция монитора, содержащая доступ к адресу, который, не маскируется ресурсами монитора, но не принадлежит ЭВМ. Перед действиями по доступу к такому адресу монитор программирует блок 18 памяти так, чтобы исключить заем зон ЗУ у отлаживаемой системы, совпадающих по адресам с ресурсами монитора. Непосредственно перед доступом монитора программно устанавливается логическая единица на третьем выходе второго регистра 20, что через элемент РШИ 21 разрешает работу блока 18 памяти. В цикле досту1453408

а логическая единица из выходе 36 устройства, как и в предыдущем слу чае, подключает разъем эмулируемого .g микропроцессора к шинам ЭВМ.

f

Таким образом, монитор имеет доступ к любой ячейке ЗУ как ЭШ, так и отлаживаемой системы, Следова 10 тельно, с помощью предлагаемого уст ройства может быть исследовано все адресное пространство ЗУ эмулируемо го микропроцессора.

15 Пусть оператор задал инструкцию монитора, содержащую доступ к УВЕ отлаживаемой системы. В этом случае монитор также освобождает место под свой рабочий фрагмент в ОЗУ ЭВМ,

20 генерирует рабочий фрагмент и передает ему управление. Рабочий фрагмент в, этом случае содержит необходимые команды ввода-вьшода, а не об мена с ЗУ. Возникает состояние ОБМЕ

гт-, Кг, -to1-.V- V- . иилпилает состояние иьин,

па блок 18 памяти срабатывает, на его 25 на выход 15 блока 7 начинает постуRfilV П ТТ ТТ T Tm -ij mTT.-i-....

выход поступает логическая единица, которая через элемент ЗАПРЕТ 23 поступает на выход 36 устройства, что подключит разъем эмулируемого микропроцессора к шинам с одновременным запретом доступа к ОЗУ ЭВМ через элемент НЕ 33. По окончании цикла доступа третий,выход регистра 20 : программируется в нуль, что запрещает работу блока 18 памяти. В течение описанных действий блок 7 оставался в состоянии МОНИТОР.а

Пусть теперь оператором задана инструкция монитора, содержащая доступ к адресу, маскируемая ресурсшчи монитора и не пpинaд.лe) ЭВМ. Г Перед генерированием рабочего фрагмента монитором блок 18 памяти программируется так, чтобы исключить заем зоны рабочего фрагмента В отличие от предыдущего случая третий выход второго регистра 20 не программируется в единицу. После передачи управления рабочему фрагменту возникает, как это описано, состояние ОБМЕН, на первьй выход 15 блока 7 поступает логическая единица и через первьй элемент ИЛИ 21 разрешает срабатывание блока 18 памяти во время цикла доступа к заданному адресу. При этом ресурсы монитора предварительно запрещены через элемент НЕ 25 по линии 34, ОЗУ ЭВМ запрещено через элемент НЕ 33 по линии 35,

пать логическая единица, которая раз решит работу блока 18 памяти и через элемент НЕ 30 запретит УЕВ ЭВМ независимо от адреса обмена и раз- 30 решит УВВ пользователя, если таковые р еются. Если УВВ пользователя нет, то блок 18 памяти предварительно про граммируется так, что любой цикл, содержащий ввод-вывод, вызывает сра- 35 батывание блока 18 памяти ,.что подключает к ЭШ разъем эмулируемого микропроцессора. Если УВВ пользовате ля в ЭВМ есть, то блок 18 памяти -- программируется так, чтобы исключить 40 срабатывание блока 18 памяти по адресу, по которому выбирается УВВ ЭВМ Таким образом, независимо от адреса УВВ, монитором исследуются как любые УВВ отлаживаемой системы, так и 45 пользовательские УВВ, если они установлены в ЭШ.

Программа пользователя может со- держать любые коды рестарта, в том числе и код, совпадающий с кодом, gQ генерируемым формирователем 22. Действительно, если в программе встретится данный код рестарта, то, если в блоке 13 не указан данный адрес как адрес прерьшания отладки, блок gg 13 не сработает и состояние ЮНИТОР не восстановится. Следовательно, по данному коду рестарта будут вьтолне- ны действия, определяемые программой пользователя, но не монитора.

1453408

а логическая единица из выходе 36 устройства, как и в предыдущем случае, подключает разъем эмулируемого микропроцессора к шинам ЭВМ.

f

Таким образом, монитор имеет доступ к любой ячейке ЗУ как ЭШ, так и отлаживаемой системы, Следова- тельно, с помощью предлагаемого устройства может быть исследовано все адресное пространство ЗУ эмулируемого микропроцессора.

Пусть оператор задал инструкцию монитора, содержащую доступ к УВЕ отлаживаемой системы. В этом случае монитор также освобождает место под свой рабочий фрагмент в ОЗУ ЭВМ,

генерирует рабочий фрагмент и передает ему управление. Рабочий фрагмент в, этом случае содержит необходимые команды ввода-вьшода, а не обена с ЗУ. Возникает состояние ОБМЕН,

-.V- V- . иилпилает состояние иьин,

на выход 15 блока 7 начинает посту

пать логическая единица, которая разрешит работу блока 18 памяти и через элемент НЕ 30 запретит УЕВ ЭВМ независимо от адреса обмена и раз- 30 решит УВВ пользователя, если таковые р еются. Если УВВ пользователя нет, то блок 18 памяти предварительно программируется так, что любой цикл, содержащий ввод-вывод, вызывает сра- 5 батывание блока 18 памяти ,.что подключает к ЭШ разъем эмулируемого микропроцессора. Если УВВ пользователя в ЭВМ есть, то блок 18 памяти -- программируется так, чтобы исключить 0 срабатывание блока 18 памяти по адресу, по которому выбирается УВВ ЭВМ. Таким образом, независимо от адреса УВВ, монитором исследуются как любые УВВ отлаживаемой системы, так и 5 пользовательские УВВ, если они установлены в ЭШ.

Программа пользователя может со- держать любые коды рестарта, в том числе и код, совпадающий с кодом, Q генерируемым формирователем 22. Действительно, если в программе встретится данный код рестарта, то, если в блоке 13 не указан данный адрес как адрес прерьшания отладки, блок g 13 не сработает и состояние ЮНИТОР не восстановится. Следовательно, по данному коду рестарта будут вьтолне- ны действия, определяемые программой пользователя, но не монитора.

Формула изобретения

15

20

25

30

35

дом дешифратора обращений, инфор ционный и адресный входы блока р стровой памяти подключены к вход устройства для подключения соотв ственно к двунаправленной шине д ных и к шине адреса управляющей числительной системы, с первого п четвертый разрешающие входы блока регистровой памяти подключены к в дам устройства для подключения к ниям соответственно чтения памяти записи памяти, чтения ввода-выво и записи ввода-вывода управляющей вычислительной системы, четвертый выход ,. дешифратора обращений соед нен с входом записи второго регис вход сброса которого подключен к ду инициализации устройства, инфо мационный вход второго регистра п ключен к входу-выходу устройства подключения к двунаправленной шин данных управляющей вычислительной темы, выход первого поля второго гистра соединен с управляющим вхо мультиплексора, выходы элементов первой группы объединены по схеме монтажного ИЛИ и образуют выход у ройства для подключения к первой нии запрета управляющей вьгаислите ной системы, выходы элементов НЕ рой группы объединены по схеме мо тажного ИЛИ и образуют выход устр ства для подключения к второй лин запрета управляющей вычислительной системы, отличающееся тем, что, с целью упрощения устрой ва, оно содержит блок определения состояний, элемент ИЛИ, элемент за

ный вход блока сравнения кодов соеди- рета, третью группу элементов НЕ,

нен с выходом мультиплексора, информационный выход блока сравнения кодов подключен к входу-выходу устройства для подключения к двунаправленной шине данных управлякяцей вычислительной системы, вход разрешения . чтения блока сравненй я кодов соединен с вторым выходом дешифратора об- ращенр1й, выход сравнения блока сравнения кодов соединен с входом форми- ;рователя кода рестарта, первый, второй и третий стробируницие входы блока сравнения кодов подключены к входам устройства для подключения к линиям соответственно чтения памяти, за- писи памяти и признака первого цикла команды управляющей вычислительной системы, вход записи блока регист- , ровой памяти соединен с третьим выхо45

50

55

причем вход инициализации блока оп деления состояний подключен к вход инициализации устройства, стробиру щий вход блока определения состоян подключен к входу устройства для п ключения к линии чтения памяти упр ляющей вычислительной системы, пер вый и второй разрешающие входы бло определения состояний соединены со ветственно с выходом второго поля второго регистра и выходом сравнен блока сравнения кодов, информацион вход блока определения состояний п ключен к входу устройства для подк чения к шине-адреса управляющей вы числительной системы, выход элемен ИЛИ соединен с пятым разрешающим в дом блока регистровой памяти, перв выход определения блока состояний

10

15

0

5

0

5

дом дешифратора обращений, информационный и адресный входы блока регистровой памяти подключены к входам устройства для подключения соответственно к двунаправленной шине данных и к шине адреса управляющей вычислительной системы, с первого по четвертый разрешающие входы блока регистровой памяти подключены к входам устройства для подключения к линиям соответственно чтения памяти, записи памяти, чтения ввода-вывода и записи ввода-вывода управляющей вычислительной системы, четвертый выход ,. дешифратора обращений соединен с входом записи второго регистра, вход сброса которого подключен к входу инициализации устройства, информационный вход второго регистра подключен к входу-выходу устройства для подключения к двунаправленной шине данных управляющей вычислительной системы, выход первого поля второго регистра соединен с управляющим входом мультиплексора, выходы элементов НЕ первой группы объединены по схеме монтажного ИЛИ и образуют выход устройства для подключения к первой линии запрета управляющей вьгаислитель- ной системы, выходы элементов НЕ второй группы объединены по схеме монтажного ИЛИ и образуют выход устройства для подключения к второй линии запрета управляющей вычислительной системы, отличающееся тем, что, с целью упрощения устройства, оно содержит блок определения состояний, элемент ИЛИ, элемент зап рета, третью группу элементов НЕ,

рета, третью группу элементов НЕ,

причем вход инициализации блока определения состояний подключен к входу инициализации устройства, стробирую- щий вход блока определения состояний подключен к входу устройства для подключения к линии чтения памяти управляющей вычислительной системы, первый и второй разрешающие входы блока определения состояний соединены соответственно с выходом второго поля . второго регистра и выходом сравнения блока сравнения кодов, информационный вход блока определения состояний подключен к входу устройства для подключения к шине-адреса управляющей вычислительной системы, выход элемента ИЛИ соединен с пятым разрешающим входом блока регистровой памяти, первый выход определения блока состояний со-

единен с входом первого элемента НЕ первой группы и первым входом элемента ИЛИ, второй вход которого, вход второго элемента НЕ первой группы, вход первого элемента НЕ третьей группы и разрешающий вход блока сравнения кодов соединены с вторым входом блока определения состояний, третий вход элемента Ш1И соединен с выходом третьего поля второго регистра, выход сравнения блока сравнения кодов соединен с входом третьего элемента НЕ первой группы, входом первого элемента НЕ второй группы -и инверсным входом элемента запрета, прямой вход которого соединен с выходом блока регистровой памяти, вход второго элемента НЕ третьей группы соединен с

ющим входом блока определения сост ний, первый вход третьего элемента И является первым разрешающим вход

g блока определения состояний, второ вход перво го элемента И соединен с выходом первого триггера, вторые в ды второго и третьего элементов И единены с выходом второго триггера

10 выходы первого и второго элементов И соединены с разрешающими входами соответственно первого и второго д шифраторов переходов, информационны входы которых объединены и соедине

15 с информационным входом блока опре деления состояний, вход инициализа ции которого соединен с первыми вхо дами первого и второго элементов ИЛИ, второй вход второго элемента И

„,. . элемента J

. Т° . .- 20 является ВТОРЫМ разрешающим входом

тояний, вькоды элементов НЕ третьей группы объединены по схеме монтажного ИЛИ и соединены с третьим управляющим входом дешифратора обращений и образуют выход устройства для подключения к третьей линии запрета управляющей вычислительной системы, выход элемента запрета соединен с входом второго элемента НЕ второй группы

блока определения состояний, выход третьего элемента И соединен с S-вх дом первого триггера и с первым вхо дом третьего элемента ИЛИ, выход ко 25 торого соединен с R-входом второго триггера, второй вход третьего элемента ИЛИ соединен с выходом второг дешифратора перехода и S-входом тре тьего тригго-ра, выходы первого и вт

„ „. - - л ttcif 1зшли,ци| lieuburo и в

Lr. .fl°l°: устройства, зо РОГО элементов ИЛИ соединены соотвторым выходом устройства является второй выход блока определения состояний.

2g яний, первый вход четвертого элемен та ИЛИ соединен с выходом второго элемента ИЛИ, выход первого дешифра тора перехода соединен с вторыми вх дами первого элемента ИЛИ и четверт

40 го элемента ИЛИ, выход которого сое динен с S-входом второго триггера.

7

ющим входом блока определения состояний, первый вход третьего элемента И является первым разрешающим входе

блока определения состояний, второй вход перво го элемента И соединен с выходом первого триггера, вторые входы второго и третьего элементов И соединены с выходом второго триггера,

выходы первого и второго элементов И соединены с разрешающими входами соответственно первого и второго дешифраторов переходов, информационные входы которых объединены и соединены

с информационным входом блока определения состояний, вход инициализации которого соединен с первыми входами первого и второго элементов ИЛИ, второй вход второго элемента ИЛИ

. элемента J

является ВТОРЫМ разрешающим входом

является ВТОРЫМ разрешающим входом

блока определения состояний, выход третьего элемента И соединен с S-вхо- дом первого триггера и с первым входом третьего элемента ИЛИ, выход ко- торого соединен с R-входом второго триггера, второй вход третьего элемента ИЛИ соединен с выходом второго ешифратора перехода и S-входом третьего тригго-ра, выходы первого и вто - л ttcif 1зшли,ци| lieuburo и в

РОГО элементов ИЛИ соединены соотзо РОГО элементов ИЛИ соединены соответственно с R-входами первого и третьего триггеров, выходы которых являются соответственно первым и вторым выходами блока определения состо2g яний, первый вход четвертого элемента ИЛИ соединен с выходом второго элемента ИЛИ, выход первого дешифратора перехода соединен с вторыми входами первого элемента ИЛИ и четверто40 го элемента ИЛИ, выход которого соединен с S-входом второго триггера.

«te/

/ ч

J9

2 й . вход

Вход чтения

52

/ ч

/

инф вхо(

53

5

-Л

S5

38

62

Выл.

Лucneт sjt

66

(Pu2.S

| Патент США № 4231087, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Алексеенко А.Г., Галицын А.А., Иванников А.Д | |||

| Проектирование радиоэлектронной аппаратуры на микропроцессорах | |||

| - М.: Радио и связь, 1984, с | |||

| Переносное устройство для вырезания круглых отверстий в листах и т.п. работ | 1919 |

|

SU226A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-01-23—Публикация

1987-01-12—Подача