шифрации состояний, блок дешифрации управляющих сигналов, блок дешифрации канальных команд, два блока триггеров, блок регистровой памяти информационных сигналов, мультиплек сор сигналов состояний и блок регистровой памяти управляющих сигналов, К групп управляющих выходов которого подключены к входам служебных сигналов К устройств вывода, К групп информационных входов мультиплексора сигналов состояний подключены к выходам сигналов состояний К устройств вывода, К групп информационных выходов блока, регистровой памяти информационных сигналов подсоединены к информационным входам К устройств вывода, группа выходов блока дешифрации управляющих сигналов подключена к шине сигналов состояния процессора, при этом группа информационных входов-выходов коммутатора данных соединена с группами информационных входов блока регистровой памяти управляющих сигналов и блока регистровой памяти информационных сигналов и группами информационных выходов мультиплексора сигналов состояний и второго блока триггеров и первой группой информационных выходов первого блока триггеров, вьрсоды элементов И группы соединены с группой адресных входов блока дешифрации ввода-вывода, дешифратора памяти, блока регисровой памяти управлякмцих сигналов, мультиплексора сигналов состояний и блока регистровой памяти информационных сигналов, выход отсутствия захвата блока управления соединен с входом разрешения блока дешифрации ввода-вывода, первый выход которого соединен с вто|Е)ым управляющим входом блока приема данных, , группа управлякицих выходов которого соединена с группой нулевых входов первого блока триггеров, вторая группа выходов которого соединена с группой нулевых входов второго блока триггеров и .первой группой информационных входов блока дешифрации состояний, вторая группа информационных входов которого соединена с группой информационных входов блока дешифрации канальных кома и группой информационных выходов регистра номера канала, группа информационных входов которого подключена к информационному выходу

процессора, первый и второй выходы регистра направления обмена соединены с входами ввода и вывода блока дешифрации ввода-вывода соответственно, второй выход которого сое- динен с вторым управляющим входом блока выдачи текущего состояния, третий управляющий вход которого соединен с первым выходом блока дешифрации управляющих сигналов, первый вход которого соединен с первым входом блока дешифрации канальных команд и с вторым выходом блока выделения адреса устройства, третий выход которого соединен с вторым входом блока дешифрации канальных команд, первая группа выходов которого соединена с группой входов занесения блока приема данных и группой единичных входов первого блока триггеров, вторая группа выходов блока дешифрации канальных команд соединена с группой единичны входов второго блока триггеров, раз . решакщий вход которого соединен с соответствующим разрядом группы управляющих выходов блока приема данных, группа входов выборки блока постоянной памяти соединена с группой выходов дешифратора памяти, выход которого соединен с разрешающим входом блока оперативной памяти, третий, четвертый и пятый выходы блока дешифрахщи ввода-вывода соединены с управляющими входами блока постоянной памяти управлякидих сигналов, мультиплексора сигналов состояний и блока регистровой памяти информационных сигналов соответственно, группа информационных входов блока дешифрации управляющих сигналов подключена к выходу команд процессора, синхровход блока дешифрации состояний соединен с управляющим входом блока выделения адреса устройства, четвертый выход которого соединен с входом блока дешифрации состояний, первый и второй выходы которого соединены с первым и вторым входами блока дешифрации управляющих сигналов соответственно, второй выход которого соединен с третьим входом блока дешифрации канальных команд, пятый выход блока выделения адреса устройства соединен с входом занесения регистра номера канала, шестой выход блока дешифрации ввода-вывода соединен с входом разрешения дешифратора памятиi К+1-я группа выходов блока регистровой памяти управляю|щих сигналов соединена с третьей

i группой информационных входов

блочка дешифрации состояний.

2, Устройство по п.1, о т л и- чающееся тем, что блок дешифрации управляющих сигналов содержит дешифратор, элемент ИЛИ и три элемента И, причем группа ин;формационных входов дешифратора образует группу информационшлх блока, управляющий вход де- шифратора соединен с первыми в)со|дами первого и второго элементов И и является первым управляющим

. входом блока, вторые входы первого и

Изобретение относится к области : вычислительной техники и может быть использовано для подключения устройств вывода к процессору ЭВМ.

Цель изобретения - повышение пропускной способности устройства за.счет его одновременной работы с несколькими устройствами вывода одного или разного типа.

Рассмотрим один из возможных вариантов устройства для сопряжения с тремя печатающими устройствами (ПчУ).

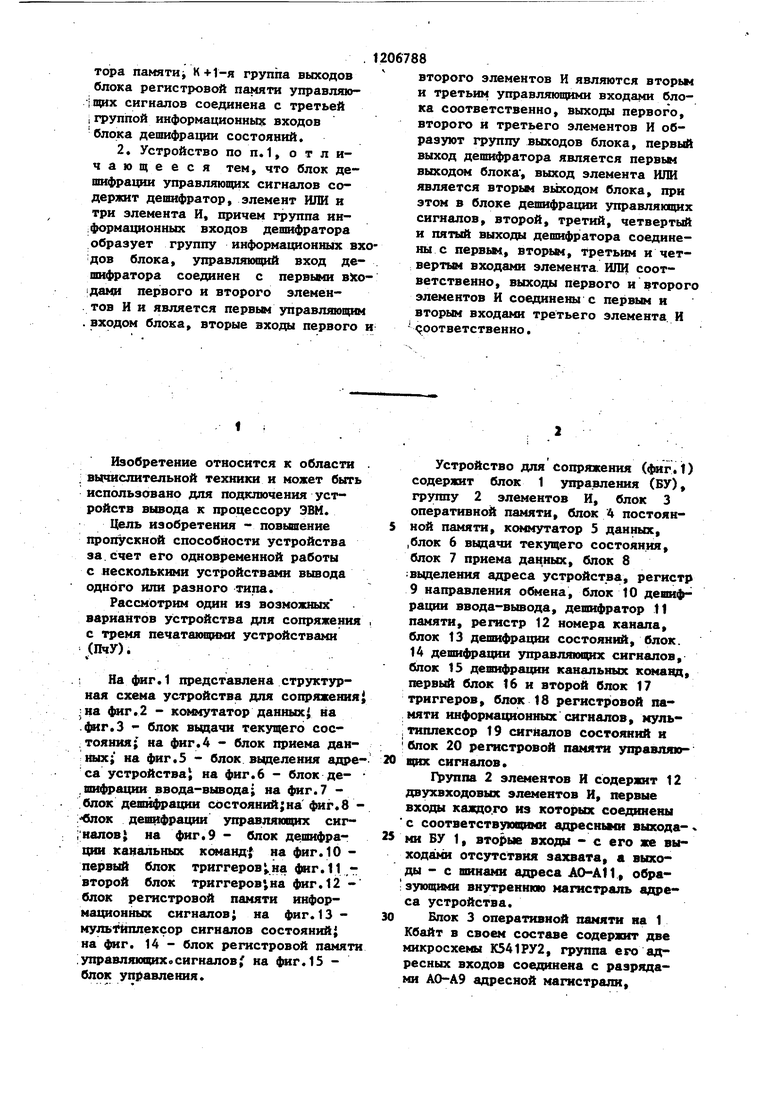

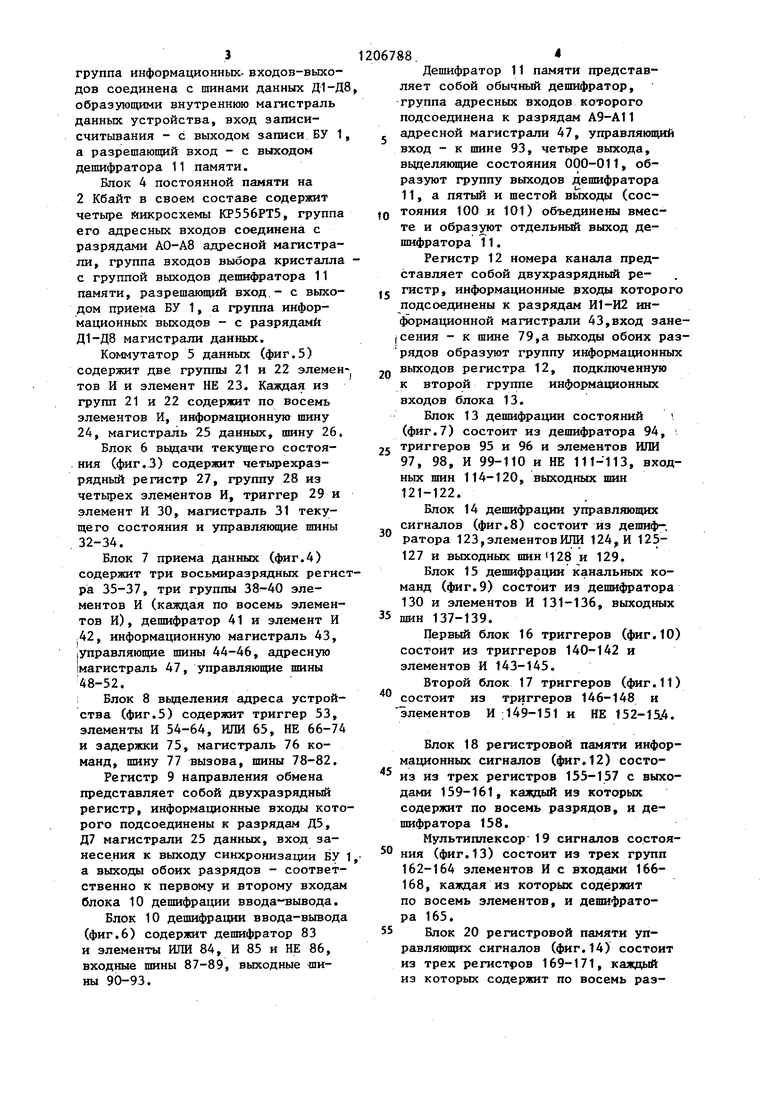

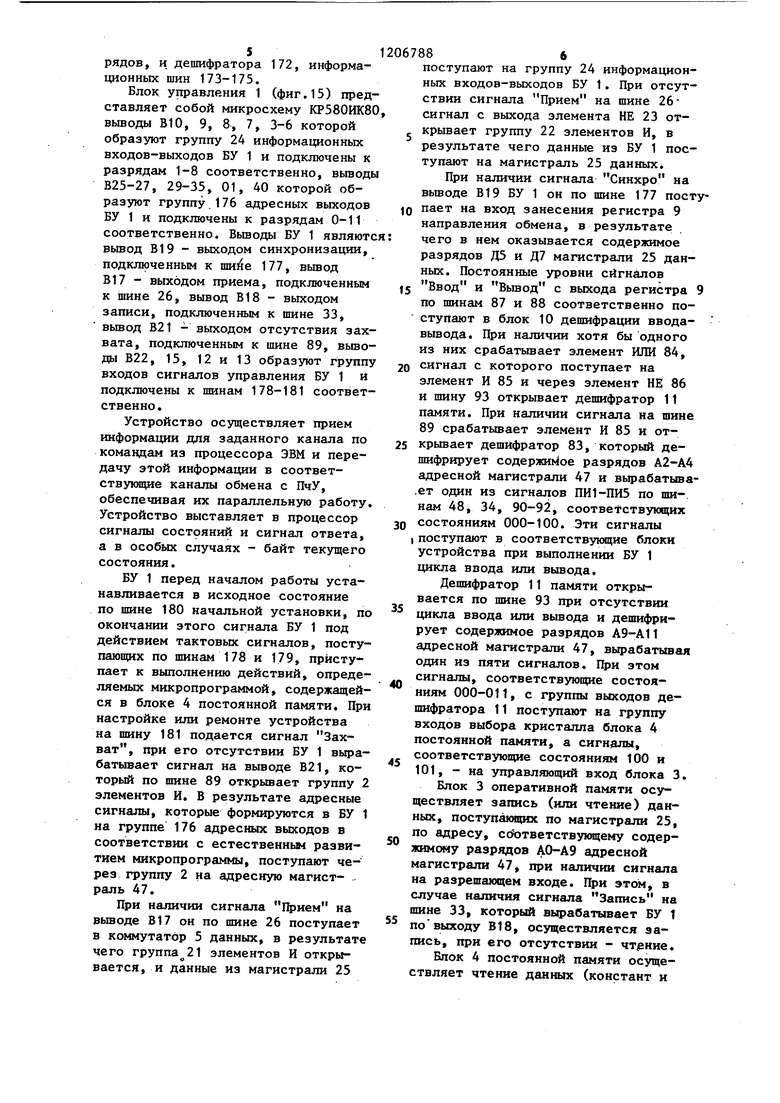

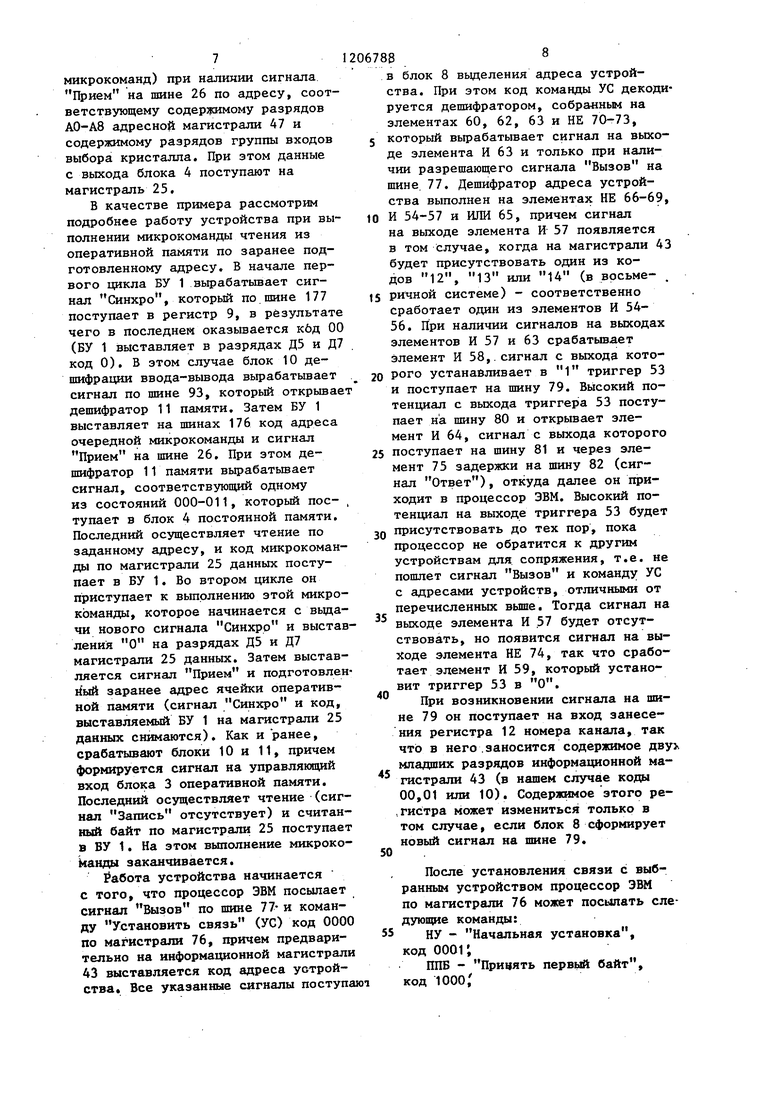

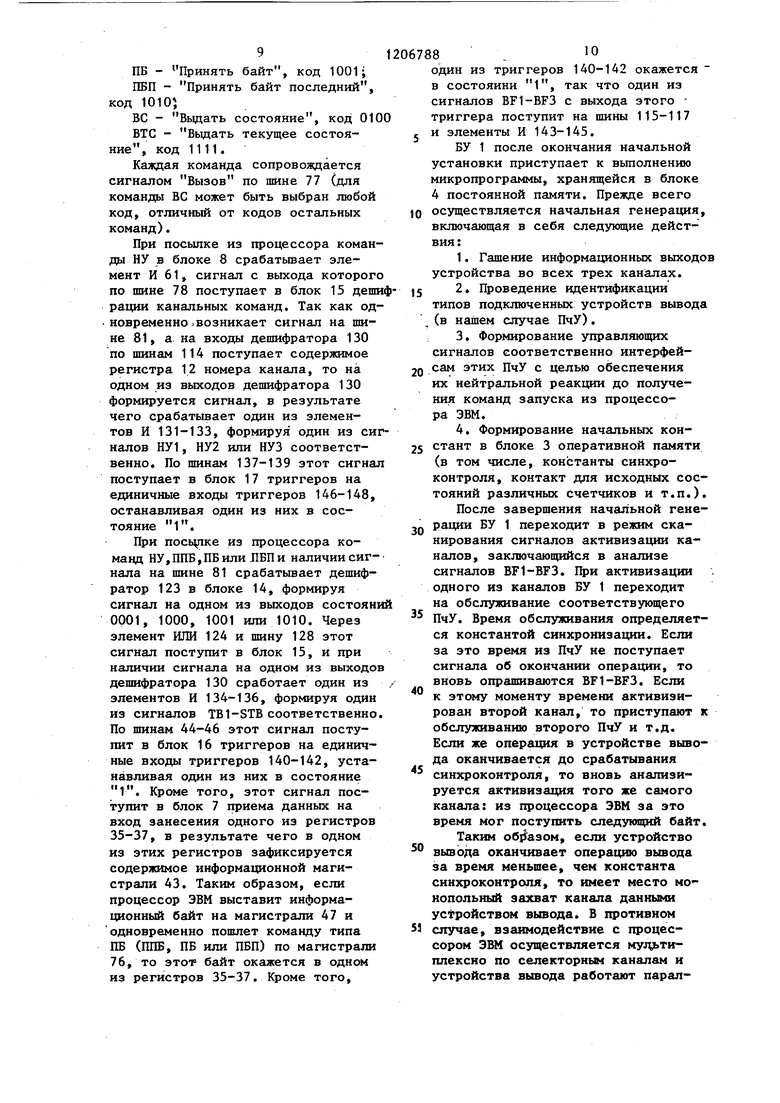

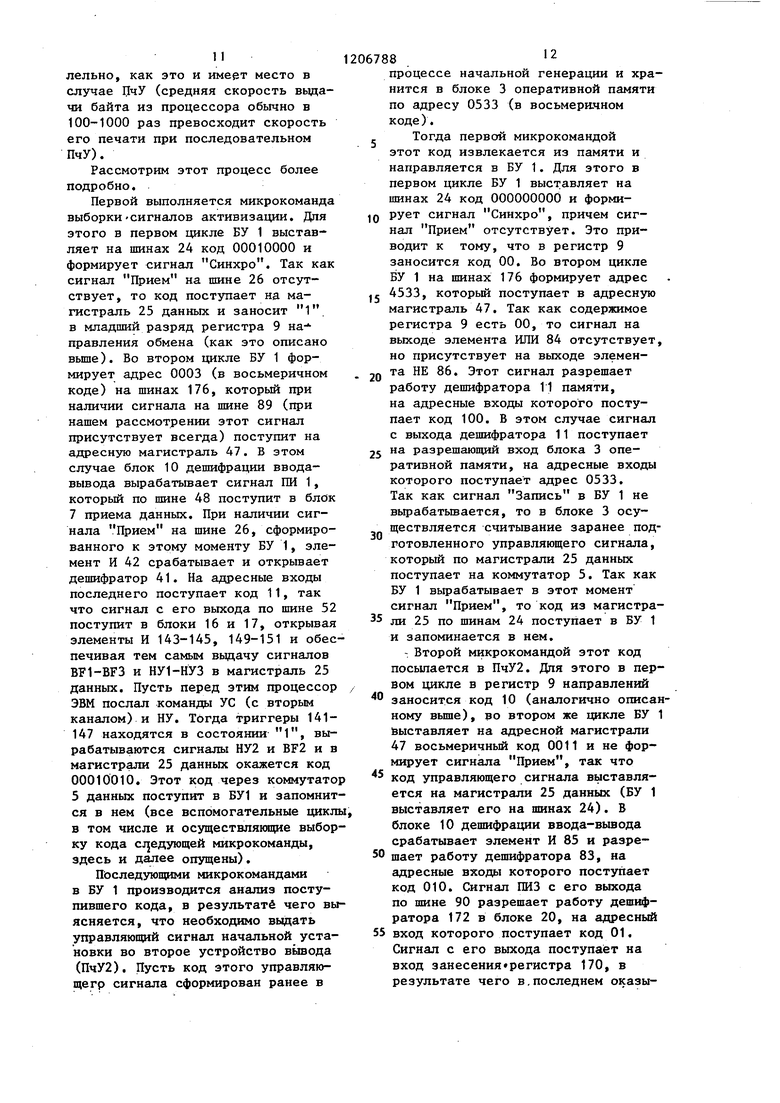

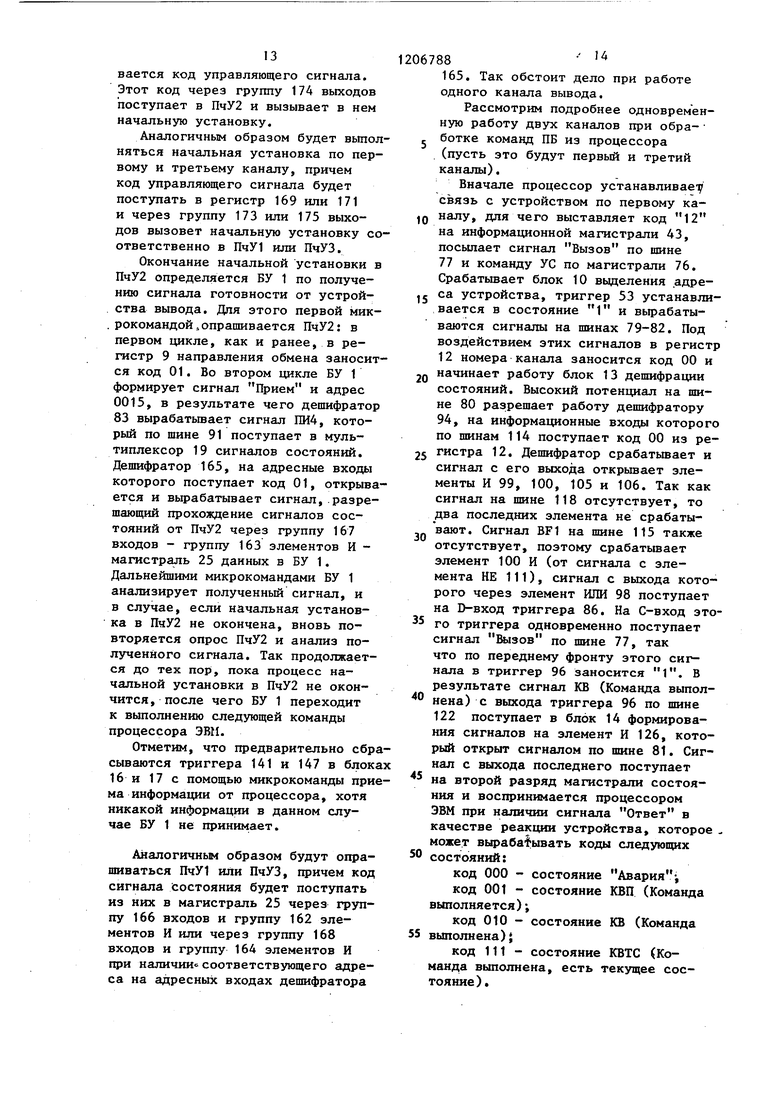

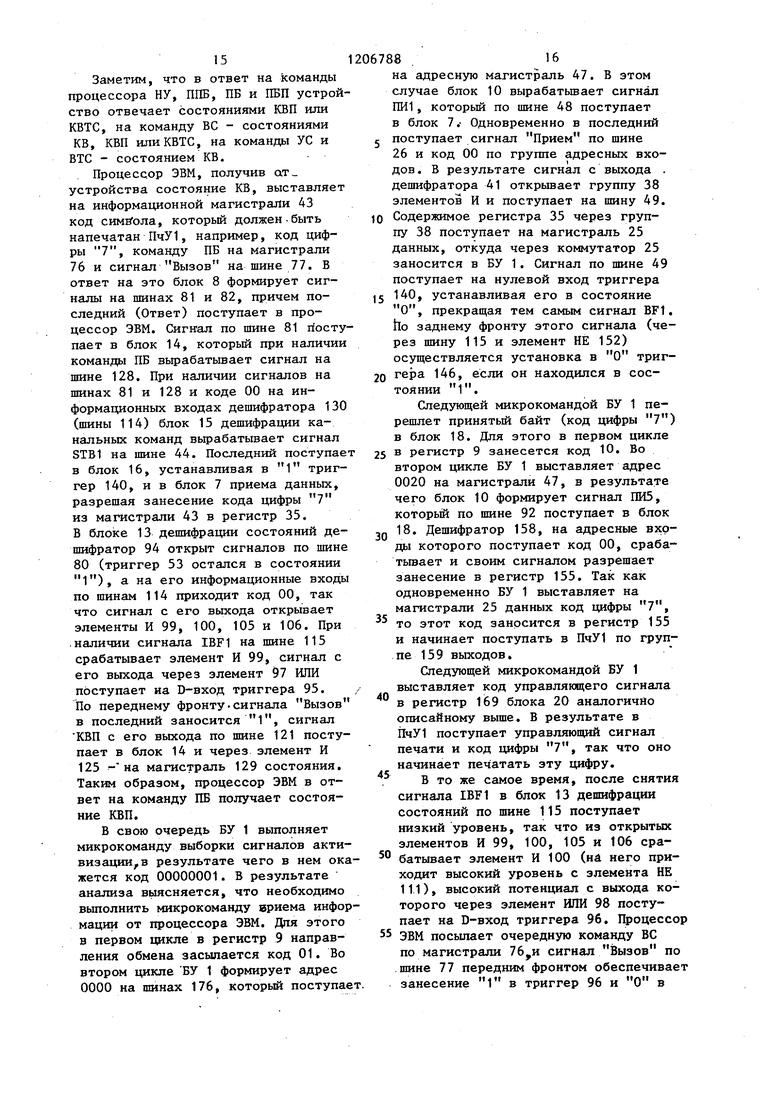

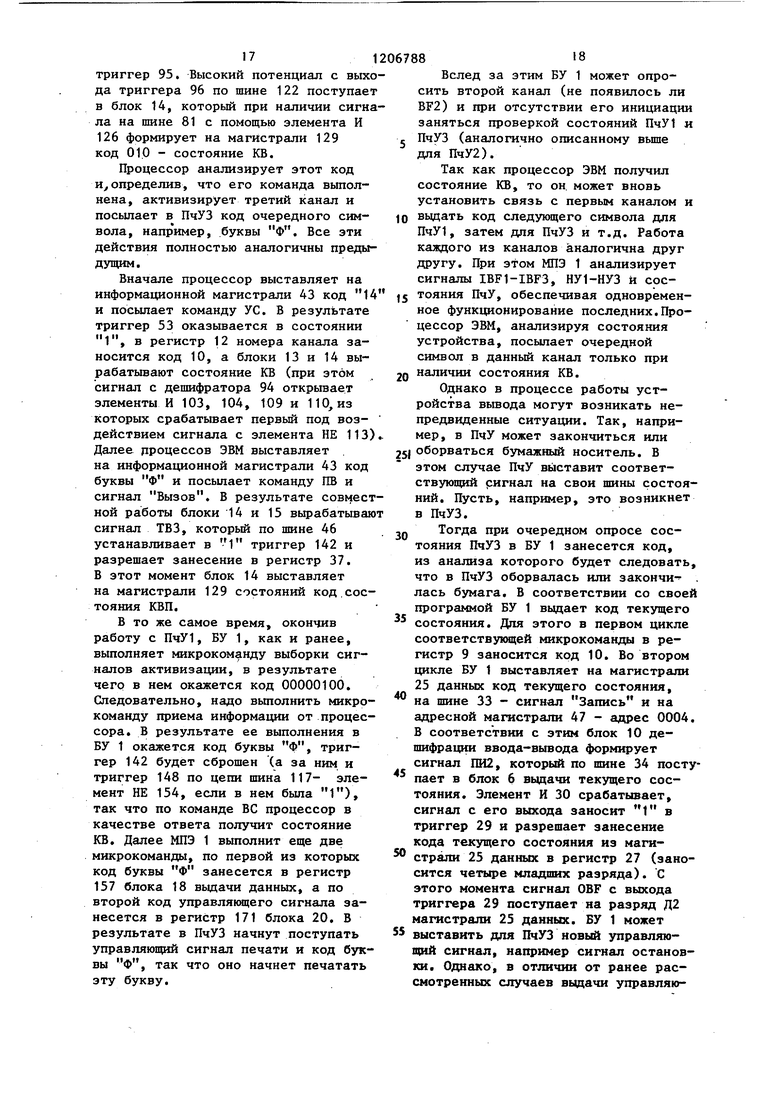

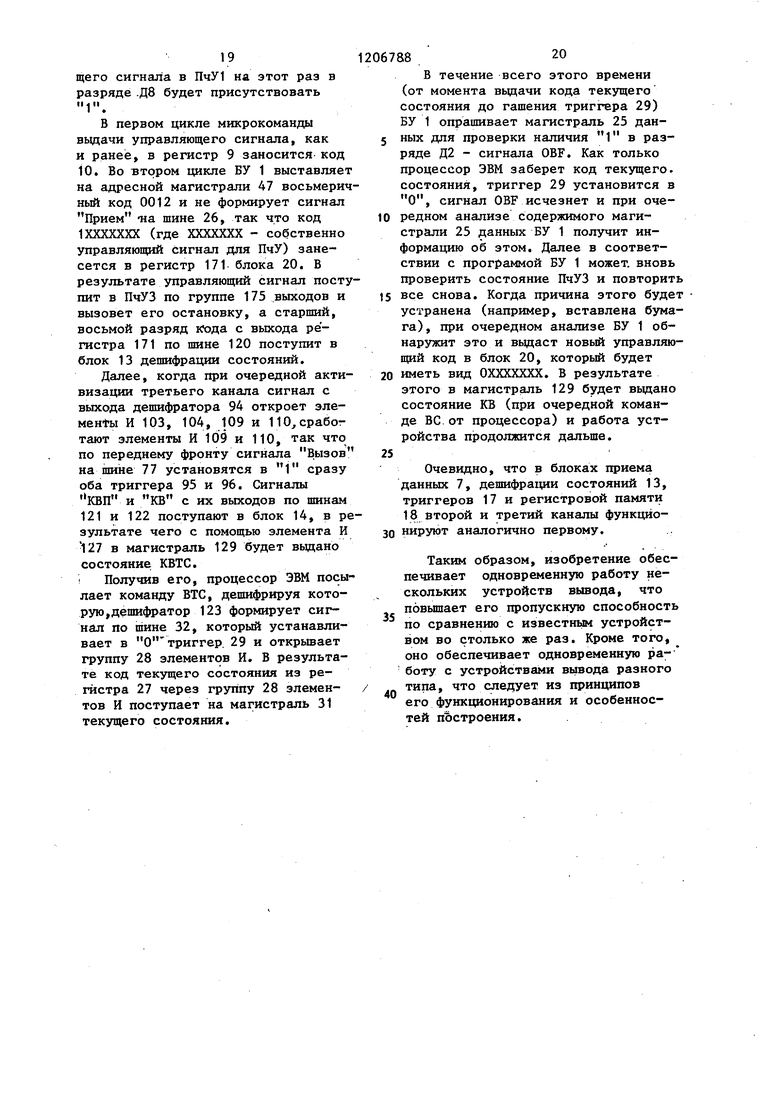

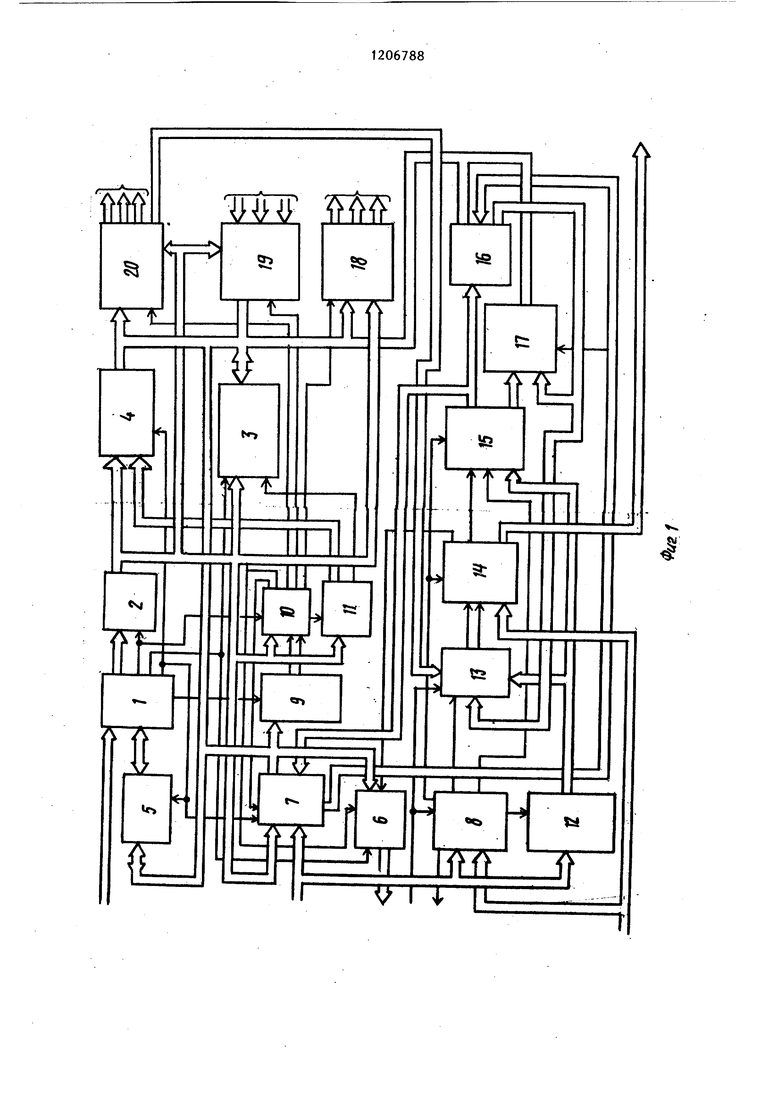

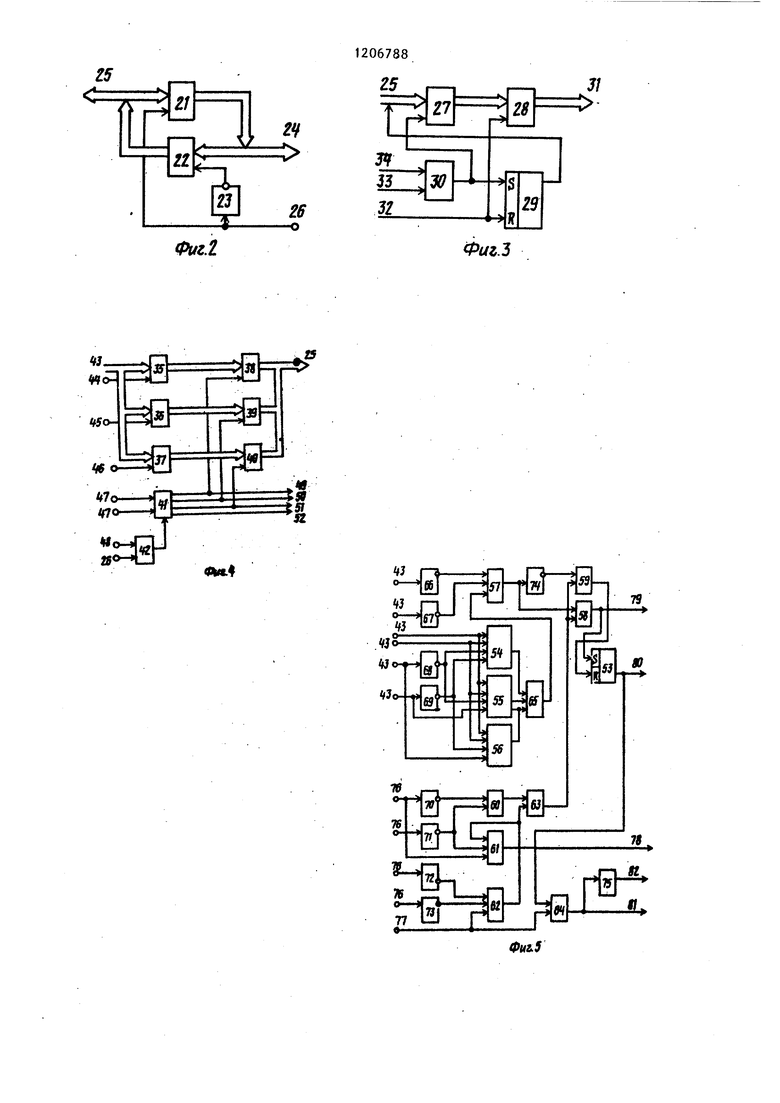

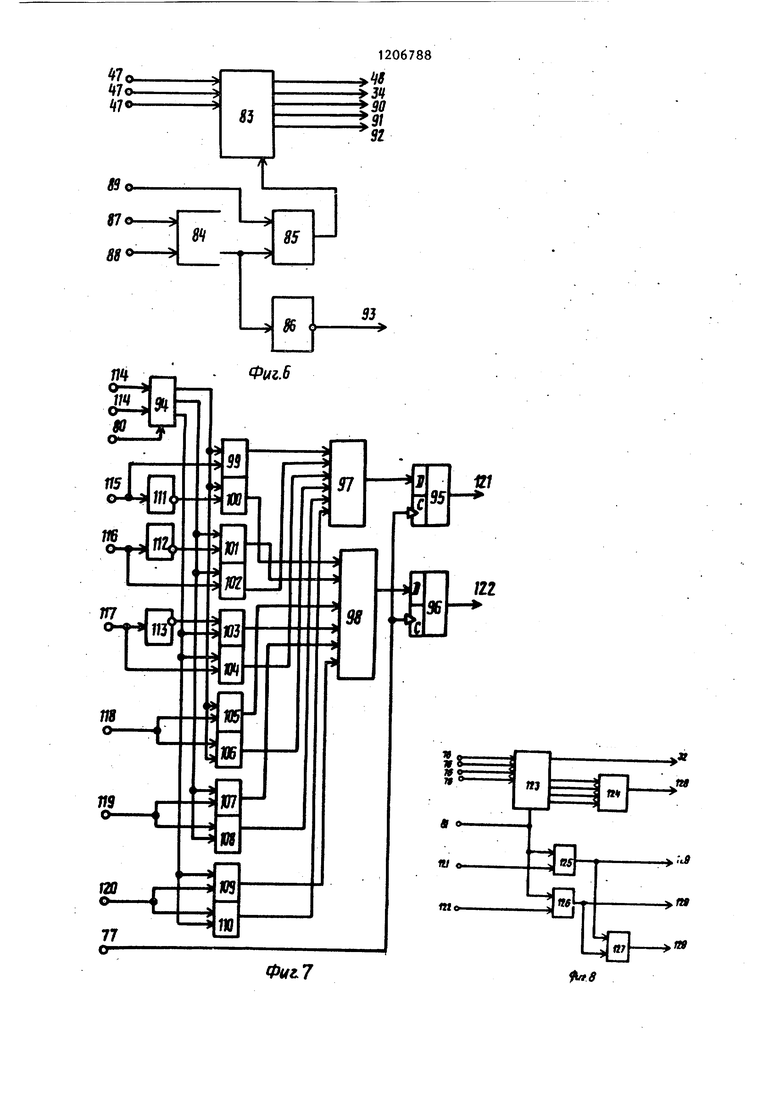

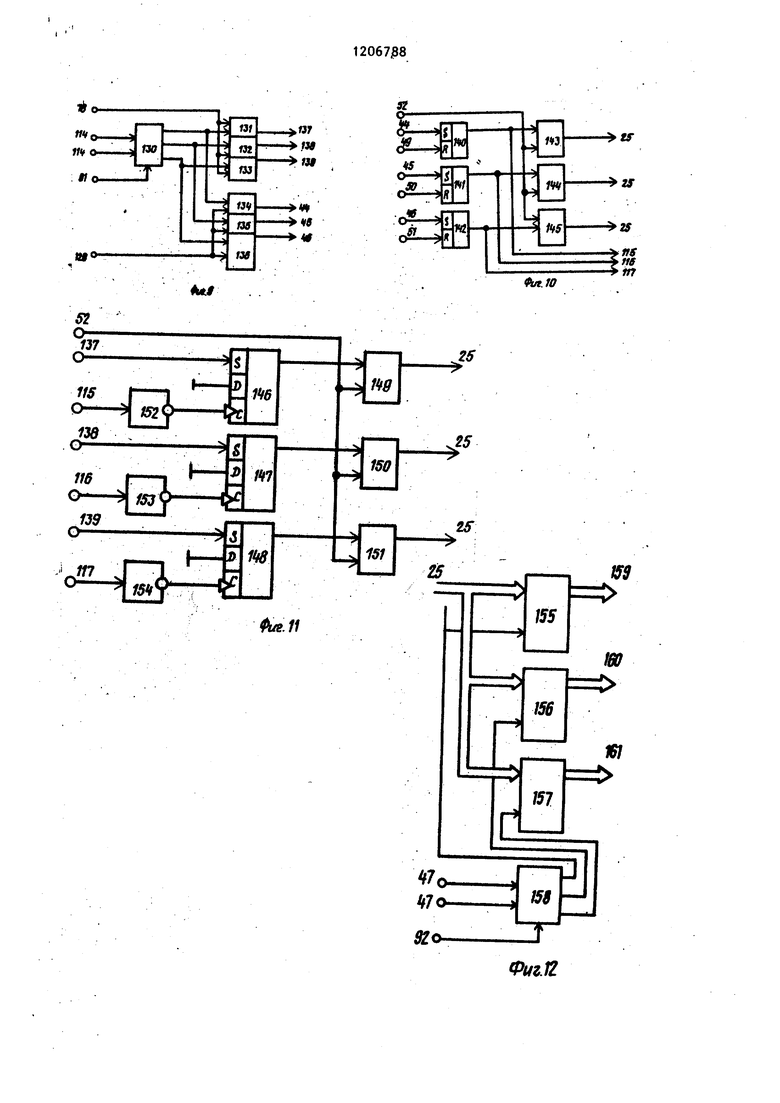

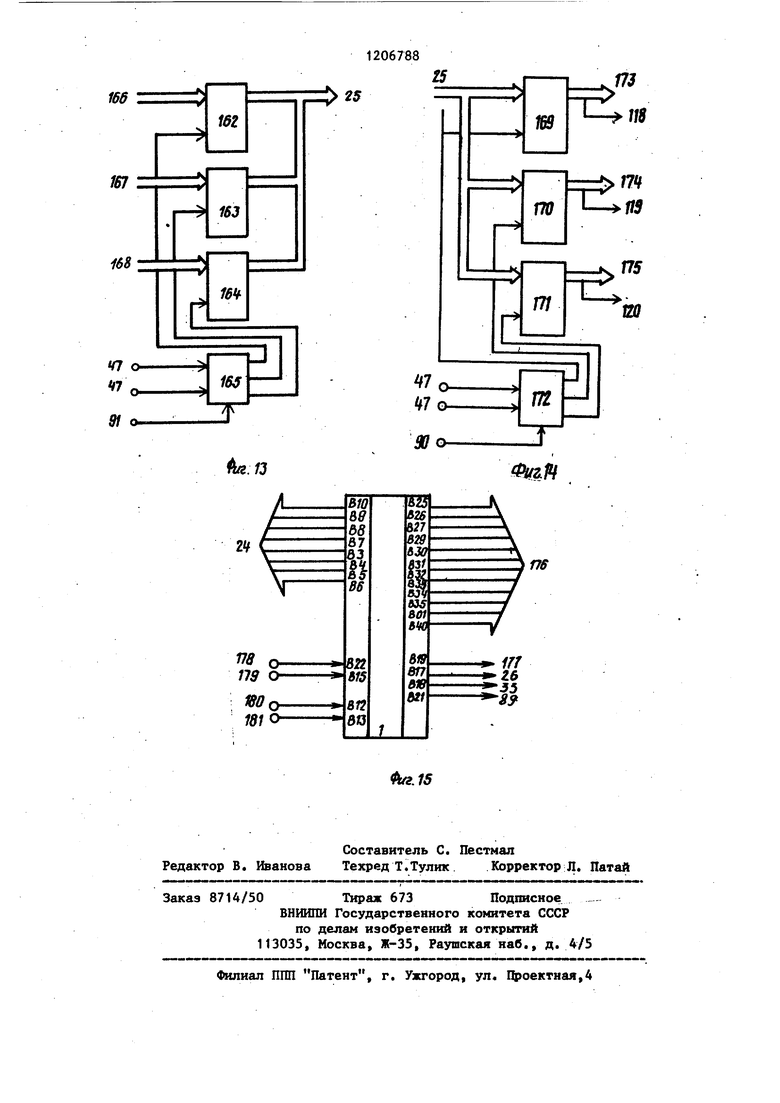

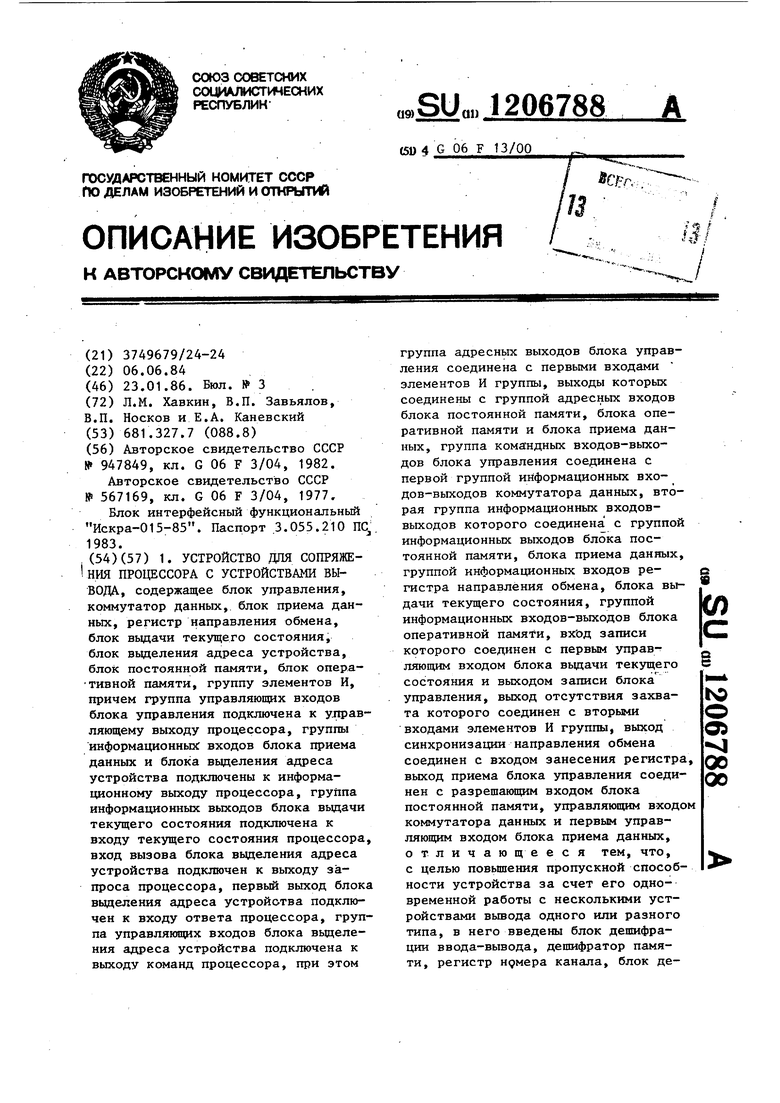

; На фиг.1 представлена структурная схема устройства для сопряжения на фиг.2 - коммутатор данных на .фиг.З - блок вьщачи текущего состояния; на фиг.4 - блок приема дан- 1шх; на фиг.5 - блок выделения адреса устройства i на фиг.6 - блок де- ,шифрации ввода-вывода; на фиг.7 - блок дешифрации состояний;на фиг.8 - дешифрации управляющих сиг ;налов} на фиг.9 - блок дешифрации канальных К1жанд| на фиг.10 - первый блок триггеров;на фиг.11,г второй блок триггеров«,на фиг. 12 - блок регистровой памяти инфор- мгщионных сигналов; на фиг.13 - мулы йплексор сигналов состояний} на фиг. 14 - блок регистровой памяти :управляющихосигналовf на фиг.15 - блок управления.

второго элементов И являются вторьн и третьим управляющими входами блока соответственно, выходы первого, второго и третьего элементов И образуют группу выходов блока, первый выход дешифратора является первым выходом блока , выход элемента ИЛИ является вторым выходом блока, при этом в блоке дешифрации управляющих сигналов, второй, третий, четвертый и пятый выходы дешифратора соединены с первым, вторым, третьим и четвертым входами элемента. ШШ соответственно, выходы первого и второго элементов И соединены с первым и вторым входами третьего элемента. И

(соответственно.

Устройство для сопряжения (фиг.1) содержит блок 1 управления (БУ), группу 2 элементов И, блок 3 оперативной памяти, блок А постоян- ной памяти, коммутатор 5 данных, ,блок 6 вьщачи текущего состояния, блок 7 приема данных, блок 8 выделения адреса устройства, регистр 9 направления обмена, блок 10 дешифрации ввода-вывода, дешифратор 11 памяти, регистр 12 номера канала, блок 13 дешифрации состояний, блок. 14 дешифрации управляющих сигналов, блок 15 дешифрации канальных комацд, первый блок 16 и второй блок 17 триггеров, блок 18 регистровой памяти информационных сигналов, мульIтиплексор 19 сигналов состояний и

I блок 20 регистровой памяти управляю- щих сигналов.

2 элементов И содержит 12 двухвходовых элементов И, первые входы каждо.го из которых соединены

с соответствуют адресньми выхода- ми БУ 1, вторые входы - с его же выходами отсутствия захвата, а выходы - с шинами адреса А(ЬА11, обра зующими внутреннюю магистраль адреса устройства.

Блок 3 оперативной памяти на 1 Кбайт в своем составе содержит две микросхемы К541РУ2, группа его адресных входов соединена с разрядами АО-А9 адресной магистрали.

группа информационных- входов-выходов соединена с шинами данных Д1-Д образую1цими внутреннюю магистраль данных устройства, вход записи- считывания - с выходом записи БУ 1 а разрешающий вход - с выходом дешифратора 11 памяти.

Блок 4 постоянной памяти на 2 Кбайт в своем составе содержит четыре микросхемы КР556РТ5, группа его адресных входов соединена с разрядами АО-А8 адресной магистрали, группа входов выбора кристалла с группой выходов дешифратора 11 памяти, разрешающий вход - с выходом приема БУ 1, а группа информационных выходов - с разрядами Д1-Д8 магистрали данных.

Коммутатор 5 данных (фиг.5) содержит две группы 21 и 22 элементов И и элемент НЕ 23. Каждая из групп 21 и 22 содержит по восемь элементов И, информационную шину 24, магистраль 25 данных, шину 26.

Блок 6 вьщачи текущего состояния (фиг.З) содержит четырехразрядный регистр 27, группу 28 из четьфех элементов И, триггер 29 и элемент И 30, магистраль 31 текущего состояния и управлякщие шины 32-34.

Блок 7 приема данных (фиг.4) содержит три восьмиразрядных регисра 35-37, три группы 38-40 элементов И (каждая по восемь элементов И), дешифратор 41 и элемент И 42, информационную магистраль 43, (Управляющие шины 44-46, адресную {магистраль 47, управляющие шины 48-52.

i Блок 8 выделения адреса устройства (фиг.5) содержит триггер 53, элементы И 54-64, ИЛИ 65, НЕ 66-74 и задержки 75, магистраль 76 команд, шину 77 вызова, шины 78-82.

Регистр 9 направления обмена представляет собой двухразрядный регистр, информационные входы которого подсоединены к разрядам Д5, Д7 магистрали 25 данных, вход занесения к выходу синхронизации БУ а выходы обоих разрядов - соответственно к первому и второму входам блока 10 дешифрации ввода -вывода.

Блок 10 дешифрации ввода-вывода (фиг.6) содержит дешифратор 83 и элементы ИЛИ 84, И 85 и НЕ 86, входные шины 87-89, выходные шины 90-93.

206788.

Дешифратор 11 памяти представляет собой обычный дешифратор, группа адресных входов которого подсоединена к разрядам А9-А11 , адресной магистрали 47, управляющий вход - к шине 93, четыре выхода, вьщеляющие состояния 000-011, образуют группу выходов дешифратора 11, а пятый и шестой выходы (сос- JQ тояния 100 и 101) объединены вместе и образуют отдельный выход де- пшфратора 11.

Регистр 12 номера канала представляет собой двухразрядный ре- J5 гнстр, информационные входы которого подсоединены к разрядам И1-И2 информационной магистрали 43,вход зане- (Сения - к шине 79,а выходы обоих раз- рядов образуют группу информационных 2Q выходов регистра 12, подключенную к второй группе информационных входов блока 13.

Блок 13 дешифрации состояний (фиг.7) состоит из дешифратора 94, 25 триггеров 95 и 96 и элементов ИЛИ 97, 98, И 99-110 и НЕ 111-113, входных шин 114-120, выходных шин 121-122.

Блок 14 дешифрации управляющих сигналов (фиг.8) состоит из дешиф-, ратора 123,элементов ИЛИ 124, И 125- 127 и выходных шин 128 и 129.

Блок 15 дешифрации канальных команд (фиг.9) состоит из дешифратора 130 и элементов И 131-136, выходных 35 шин 137-139.

Первый блок 16 триггеров (фиг.10) состоит из триггеров 140-142 и элементов И 143-145.

Второй блок 17 триггеров (фиг.11)

30

состоит из триггеров 146-148 и элементов И ; 149-151 и НЕ 152-15,4.

Блок 18 регистровой памяти информационных сигналов (фиг.12) состо из из трех регистров 155-157 с выходами 159-161, калздый из которых содержит по восемь разрядов, и дешифратора 158.

Мультиплексор 19 сигналов состоя ния (фиг.13) состоит из трех групп 162-164 злементов И с входами 166- 168, каждая из которых содержит по восемь элементов, и дешифратора 165.

55 Блок 20 регистровой памяти управляющих сигналов (фиг.14) состоит из трех регистров 169-171, каждый из которых содержит по восемь разрядов, и дешифратора 172, информационных шин 173-175.

Блок управления 1 (фиг.15) представляет собой микросхему КР580Ж80 вьшоды В10, 9, 8, 7, 3-6 которой образуют группу 24 информационных входов-выходов БУ 1 и подключены к разрядам 1-8 соответственно, вьгооды В25-27, 29-35, 01, 40 которой образуют группу 176 адресных выходов БУ 1 и подключены к разрядам 0-11 соответственно. Вьтоды БУ 1 являютс вьшод В19 - выходом синхронизации, подключенным к шийе 177, вывод В17 - выходом приема, подключенным к шине 26, вывод В18 - выходом записи, подключенным к шине 33, вьтод В21 - выходом отсутствия захвата, подключенным к шине 89, вьюо- ды В22, 15, 12 и 13 образуют группу входов сигналов управления БУ 1 и подключены к шинам 178-181 соответственно.

Устройство осуществляет прием информа1щи для заданного канала по командам из процессора ЭВМ и передачу этой информации в соответствующие каналы обмена с ПчУ, обеспечивая их параллельную работу. Устройство выставляет в процессор сигналы состояний и сигнал ответа, а в особых случаях - байт текущего состояния.

БУ 1 перед началом работы устанавливается в исходное состояние по шине 180 начальной установки, по окончании этого сигнала БУ 1 под действием тактовых сигналов, поступающих по шинам 178 и 179, приступает к выполнению действий, определяемых микропрограммой, содержащейся в блоке 4 постоянной памяти. При настройке или ремонте устройства на шину 181 подается сигнал Захват, при его отсутствии БУ 1 вырабатывает сигнал на вьюоде Б21, который по шине 89 открывает группу 2 элементов И. В результате адресные сигналы, которые формируются в БУ 1 на группе 176 адресных выходов в соответствии с естественным развитием микропрограммы, поступают через группу 2 на адресную магистраль 47.

При наличии сигнала Прием на выводе В17 он по шине 26 поступает в коммутатор 5 данных, в результате чего группа 21 элементов И открывается, и данные из магистрали 25

0

0

поступают на группу 24 информационных входов-выходов БУ 1. При отсутствии сигнала Прием на шине 26- сигнал с выхода элемента НЕ 23 открывает группу 22 элементов И, в результате чего данные из БУ 1 поступают на магистраль 25 данных.

При наличии сигнала Синхро на вьшоде В19 БУ 1 он по шине 177 поступает на вход занесения регистра 9 направления обмена, в результате чего в нем оказывается содержимое разрядов Д5 и Д7 магистрали 25 данных. Постоянные уровни сигналов 5 Ввод и Вьшод с выхода регистра 9 по шинам 87 и 88 соответственно поступают в блок 10 дешифрации ввода- вывода. При наличии хотя бы одного из них срабатывает элемент ИЛИ 84, сигнал с которого поступает на элемент И 85 и через элемент НЕ 86 и шину 93 открывает дешифратор 11 памяти. При наличии сигнала на шине 89 срабатывает элемент И 85 и от- 5 крывает дешифратор 83, который дешифрирует содержимое разрядов А2-А4 адресной магистрали 47 и вьфабатыва- .ет один из сигналов ПИ1-ПИ5 по ши-. нам 48, 34, 90-92, соответствующих состояниям 000-100. Эти сигналы I поступают в соответствующие блоки устройства при выполнении БУ 1 цикла ввода или вывода.

Дешифратор 11 памяти открывается по шине 93 при отсутствии цикла ввода шш вывода и дешифрирует содержимое разрядов А9-А11 адресной магистрали 47, вырабатывая один из пяти сигналов. При этом сигналы, соответствующие состояниям 000-011, с группы выходов дешифратора 11 поступают на группу входов выбора кристалла блока 4 постоянной памяти, а сигналы, соответствующие состояниям 100 и 101, - на управляющий вход блока 3.

Блок 3 оперативной памяти осуществляет запись (или чтение) дан0

5

0

5

ных, поступающих по магистрали 25, по адресу, ссйэтветствующему содер- жиметчу разрядов АО-А9 адресной магистрали 47, при наличии сигнала на разрешающем входе. При этом, в случае наличия сигнала Запись на шине 33, который вырабатывает БУ 1 по выходу В18, осуществляется запись, при его отсутствии - чтэние. Блок 4 постоянной памяти осуществляет чтение данных (констант и

микрокоманд) при налинии сигнала Прием на шине 26 по адресу, соответствующему содер:р1мому разрядов АО-А8 адресно магистрали 47 и содержимому разрядов группы входов выбора кристалла. При этом данные с выхода блока 4 поступают на магистраль 25.

В качестве примера рассмотрим подробнее работу устройства при выполнении микрокоманды чтения из оперативной памяти по заранее подготовленному адресу. В начале первого цикла БУ 1 вьфабатывает сигнал Синхро, который по шине 177 поступает в регистр 9, в результате чего в последнем оказывается кбд 00 (БУ 1 выставляет в разрядах Д5 и Д7 код 0). В этом случае блок 10 дешифрации ввода-вывода вьфабатывает сигнал по шине 93, который открывае дешифратор 11 памяти. Затем БУ 1 выставляет на шинах 176 код адреса очередной микрокоманды и сигнал Прием на шине 26. При этом дешифратор 11 памяти вырабатьюает сигнал, соответствующий одному из состояний 000-011, который пос- тупает в блок 4 постоянной памяти. Последний осуществляет чтение по заданному адресу, и код микрокоманды по магистрали 25 данных поступает в БУ 1. Во втором цикле он приступает к выполнению этой микрокоманды, которое начинается с вьща- чи нового сигнала Синхро и выставления О на разрядах Д5 и Д7 магистрали 25 данных. Затем выставляется сигнал Прием и подготовлен йый заранее адрес ячейки оперативной памяти (сигнал Синхро и код, выставляемый БУ 1 на магистрали 25 данных снимаются). Как и ранее, срабатывают блоки 10 и 11, причем формируется сигнал на управляющий вход блока 3 оперативной памяти. Последний осуществляет чтение (сигнал Запись отсутствует) и считанный байт по магистрали 25 поступает в ВУ 1. На этом выполнение микрокоманды заканчивается.

Работа устройства начинается с того, что процессор ЭВМ посылает сигнал Вызов по шине 77- и команду Установить связь (УС) код 0000 по магистрали 76, причем предварительно на информационной магистрали 43 выставляется код адреса устройства. Все указанные сигналы поступаю

2067888

в блок 8 вьщеления адреса устройства. При этом код команды УС декодируется дешифратором, собранным на элементах 60, 62, 63 и НЕ 70-73,

5 который вьфабатывает сигнал на выходе элемента И 63 и только при наличии разрешающего сигнала Вызов на шине 77. Дешифратор адреса устройства выполнен на элементах НЕ 66-69,

10 И 54-57 и ИЛИ 65, причем сигнал на выходе элемента И 57 появляется в том случае, когда на магистрали 43 будет присутствовать один из кодов 12, 13 или 14 (в врсьме15 ричной системе) - соответственно сработает один из элементов И 54- 56. 11ри наличии сигналов на выходах элементов И 57 и 63 срабатывает элемент И 58,. сигнал с выхода кото20 Рого устанавливает в 1 триггер 53 и поступает на шину 79. Высокий потенциал с выхода триггера 53 поступает на шину 80 и открывает элемент И 64, сигнал с выхода которого

25 поступает на шину 81 и через элемент 75 задержки на шину 82 (сигнал Ответ), откуда далее он приходит в процессор ЭВМ. Высокий потенциал на выходе триггера 53 будет

3Q присутствовать до тех пор, пока процессор не обратится к другим устройствам для сопряжения, т.е. не пошлет сигнал Вызов и команду УС с адресами устройств, отличными от перечисленных выше. Тогда сигнал на выходе элемента И 57 будет отсутствовать, но появится сигнал на выходе элемента НЕ 74, так что сработает элемент И 59, который установит триггер 53 в О.

При возникновении сигнала на шине 79 он поступает на вход занесе ния регистра 12 номера канала, так что в него .заносится содержимое двух младших разрядов информационной магистрали 43 (в нашем случае коды 00,01 или 10). Содержимое этого ре- гибтра может измениться только в том случае, если блок 8 сформирует новый сигнал на шине 79.

35

40

45

50

55

После установления связи с выбранным устройством процессор ЭВМ по магистрали 76 может посылать следующие команды:

НУ - Начальная установка, код 0001;

ППБ - Принять первый байт,

код юоо;

ПБ - Принять байт, код 1001;

ПБП - Принять байт последний, код 1010

ВС - Вьщать состояние, код 0100

ВТС - Бьщать текущее состояние, код 1111.

Каждая команда сопровождается сигналом Вызов по шине 77 (для команды ВС может быть выбран любой код, отличный от кодов остальных команд).

При посылке из процессора команды НУ в блоке 8 срабатьшает элемент И 61, сигнал с вьпсода которого по шине 78 поступает в блок 15 дешифрации канальных команд. Так как од- повременно.возникает сигнал на шине 81, а на входы дешифратора 130 по шинам 114 поступает содержимое регистра 12 номера канала, то на одном из выходов дешифратора 130 формируется сигнал, в результате чего срабатывает один из элементов И 131-133, формируя один из сигналов НУ1, НУ2 или НУЗ соответственно. По шинам 137-139 этот сигнал поступает в блок 17 триггеров на единичные входы триггеров 146-148, останавливая один из них в состояние 1.

При посьщке из процессора команд НУ, ППБ, ПБ или ЛБП и наличии сигнала на шине 81 срабатывает дешифратор 123 в блоке 14, формируя сигнал на одном из выходов состояний 0001, 1000, 1001 или 1010. Через элемент ИЛИ 124 и шину 128 этот сигнал поступит в блок 15, и при наличии сигнала на одном из выходов дешифратора 130 сработает один из элементов И 134-136, формируя один из сигналов TB1-STB соответственно. По шинам 44-46 этот сигнал поступит в блок 16 триггеров на единичные входы триггеров 140-142, устанавливая один из них в состояние 1. Кроме того, этот сигнал поступит в блок 7 приема данных на вход занесения одного из регистров 35-37, в результате чего в одном из этих регистров зафиксируется содержимое информационной магистрали 43. Таким образом, если процессор ЭВМ выставит информационный байт на магистрали 47 и одновременно пошлет команду типа ПБ (ППБ, ПБ или ПБП) по магистрали 76, то этот байт окажется в одном из регистров 35-37. Кроме того.

0

5

один из триггеров 140-142 окажется в состояини 1, так что один из сигналов BF1-BF3 с выхода этого триггера поступит на шины 115-117

и элементы И 143-145.

БУ 1 после окончания начальной установки приступает к вьтолнению микропрограммы, хранящейся в блоке 4 постоянной памяти. Прежде всего

осуществляется начальная генерация, включающая в себя следующие действия :

1. Гашение информационных выходов устройства во всех трех каналах.

j 2. Проведение идентификации

типов подключенных устройств вывода (в нашем случае ПчУ).

3.Формирование управляющих сигналов соответственно интерфейсам этих ПчУ с целью обеспечения их нейтральной реакции до получения команд запуска из процессора ЭВМ.

4.Формирование начальных констант в блоке 3 оперативной памяти (в том числе, константы синхро- контроля, контакт для исходных состояний различных счетчиков и т.п.).

После завершения начальной генерации БУ 1 переходит в режим сканирования сигналов активизации каналов, заключающийся в анализе сигналов BF1-BF3. При активизации одного из каналов БУ 1 переходит на обслуживание соответствующего ПчУ. Время обслуживания определяется константой синхронизации. Если за это время из ПчУ не поступает сигнала об окончании операции, то вновь опрашиваются BF1-BF3. Если к этому моменту времени активизирован второй канал, то приступают к обслуживанию второго ПчУ и т.д. Если же операция в устройстве вывода оканчивается до срабатывания синхроконтроля, то вновь анализируется активизация того же самого канала: из процессора ЭВМ за это время мог поступить следующий байт.

Таким , если устройство вывода оканчивает операцию вывода за время меньшее, чем константа синхроконтроля, то имеет место мо нопольный захват канала данными устройством вывода. В противном 3 случае, взаимодействие с процессором ЭВМ осуществляется плексно по селекторным каналам и устройства вывода работают парал0

5

0

5

0

11

лельно, как это и имеет место в случае ЦчУ (средняя скорость выдачи байта из процессора обычно в 100-1000 раз превосходит скорость его печати при последовательном ПчУ).

Рассмотрим этот процесс более подробно.

Первой выполняется микрокоманда выборки-сигналов активизации. Для этого в первом цикле БУ 1 выставляет на шинах 24 код 00010000 и формирует сигнал Синхро. Так как сигнал Прием на шине 26 отсут ствует, то код поступает на магистраль 25 данных и заносит 1 в младший разряд регистра 9 на- правления обмена (как это описано Bbmie). Во втором цикле БУ 1 формирует адрес 0003 (в восьмеричном коде) на шинах 176, который при наличии сигнала на шине 89 (при нашем рассмотрении этот сигнал присутствует всегда) поступит на адресную магистраль 47. В этом случае блок 10 дешифрации ввода- вывода вырабатывает сигнал ПИ 1, который по шине 48 поступит в блок 7 приема данных. При наличии сигнала Прием на шине 26, сформированного к этому моменту БУ 1, элемент И 42 срабатывает и открывает дешифратор 41. На адресные входы последнего поступает код 11, так что сигнал с его выхода по шине 52 поступит в блоки 16 и 17, открывая элементы И 143-145, 149-151 и обеспечивая тем самым выдачу сигналов BF1-BF3 и НУ1-НУЗ в магистраль 25 данных. Пусть перед этим процессор , ЭВМ послал команды УС (с вторым каналом) и НУ. Тогда триггеры 141- 147 находятся в состоянии 1, вырабатываются сигналы НУ2 и BF2 и в магистрали 25 данньк окажется код 00010010. Этот код через коммутатор 5 данных поступит в БУ1 и запомнится в нем (все вспомогательные циклы, в том числе и осуществлянщие выборку кода CJJeдyющeй микрокоманды, здесь и далее опущены).

Последующими микрокомандами в БУ 1 производится анализ поступившего кода, в результате чего выясняется, что необходимо выдать управляющий сигнал начальной установки во второе устройство вывода (ПчУ2). Пусть код этого управляю- щегр сигнала сформирован ранее в

10

- 20

1206788 2

процессе начальной генерации и хранится в блоке 3 оперативной памяти по адресу 0533 (в восьмеричном коде).

Тогда первой микрокомандой этот код извлекается из памяти и направляется в БУ 1. Для этого в первом цикле БУ 1 выставляет на шинах 24 код ООООООООО и формирует сигнал Синхро, причем сигнал Прием отсутствует. Это приводит к тому, что в регистр 9 заносится код 00. Во втором цикле БУ 1 на шинах 176 формирует адрес

JJ 4533, который поступает в адресную магистраль 47. Так как содержимое регистра 9 есть 00, то сигнал на выходе элемента ИЛИ 84 отсутствует, но присутствует на выходе элемента НЕ 86. Этот сигнал разрешает работу дешифратора 11 памяти, на адресные входы которого поступает код 100. В этом случае сигнал с выхода дешифратора 11 поступает

25 на разрешающий вход блока 3 оперативной памяти, на адресные входы которого поступает адрес 0533. Так как сигнал Запись в БУ 1 не вырабатьшается, то в блоке 3 осуществляется считывание заранее подготовленного управляющего сигнала, который по магистрали 25 данных поступает на коммутатор 5. Так как БУ 1 вырабатывает в этот момент сигнал Прием, то код из магистра35 ли 25 по шинам 24 поступает в БУ 1 и запоминается в нем.

- Второй микрокомандой этот код посылается в ПчУ2. Дпя этого в первом цикле в регистр 9 направлений заносится код 10 (аналогично описанному выше), во втором же цикле БУ 1 йыставляет на адресной магистрали 47 восьмеричный код ООП и не формирует сигнала Прием, так что код управляющего сигнала выставляется на магистрали 25 данных (БУ 1 выставляет его на шинах 24). В блоке 10 дешифрации ввода-вывода срабатывает элемент И 85 и разре50 шает работу дешифратора 83, на адресные входы которого поступает код 010. Сигнал ПИЗ с его выхода по шине 90 разрешает работу дешифратора 172 в блоке 20, на адресный

55 вход которого поступает код 01. Сигнал с его выхода поступает на вход занесения«регистра 170, в результате чего в,последнем оказы30

40

45

- 20

JJ

13

вается код управляющего сигнала. Этот код через группу 174 выходов поступает в ПчУ2 и вызывает в нем начальную установку.

Аналогичным образом будет вьтол няться начальная установка по первому и третьему каналу, причем код управляющего сигнала будет поступать в регистр 169 или 171 и через группу 173 или 175 выходов вызовет начальную установку соответственно в ПчУ1 или ПчУЗ.

Окончание начальной установки в ПчУ2 определяется БУ 1 по получению сигнала готовности от устройства вывода. Дпя этого первой микрокомандой, опращивается ПчУ2: в первом цикле, как и ранее, в регистр 9 направления обмена заносится код 01. Во втором цикле БУ 1 формирует сигнал Прием и адрес 0015, в результате чего дешифратор 83 вырабатывает сигнал 11И4, который по шине 91 поступает в мультиплексор 19 сигналов состояний. Дешифратор 165, на адресные входы которого поступает код 01, открывается и вьфабатывает сигнал,.разрешающий прохождение сигналов состояний от ПчУ2 через группу 167 входов - группу 163 элементов И - магистраль 25 данных в БУ 1. Дальнейшими микрокомандами БУ 1 анализирует полученный сигнал, и в случае, если начальная установка в ПчУ2 не окончена, вновь повторяется опрос 11чУ2 и анализ полученного сигнала. Так продолжается до тех пор, пока процесс начальной установки в ПчУ2 не окончится, после чего БУ 1 переходит к выполнению следующей команды процессора ЭВМ.

Отметим, что предварительно сбрсываются триггера 141 и 147 в блок 16 и 17 с помощью микрокоманды прима информации от процессора, хотя никакой информации в данном случае БУ 1 не принимает.

Аналогичным образом будут опрашиваться ПчУ1 или ПчУЗ, причем код сигнала состояния будет поступать из них в магистраль 25 через группу 166 входов и группу 162 элементов И или через группу 168 входов и группу 164 элементов И при наличии соответствующего адреса на адресных входах дешифратора

10

15

20

206788

165. Так обстоит дело при работе одного канала вывода.

Рассмотрим подробнее одновременную работу двух каналов при обра-

, ботке команд ПБ из процессора (пусть это будут первый и третий каналы).

Вначале процессор устанавливае- связь с устройством по первому каналу, для чего выставляет код 12 на информационной магистрали 43, посылает сигнал Вызов по шине 77 и команду УС по магистрали 76. Срабатывает блок 10 вьщеления адреса устройства, триггер 53 устанавливается в состояние 1 и вьфабаты- ваются сигналы на шинах 79-82. Под воздействием этих сигналов в регистр 12 номера канала заносится код 00 и начинает работу блок 13 дешифрации состояний. Высокий потенциал на шине 80 разрешает работу дешифратору 94, на информационные входы которого по шинам 114 поступает код 00 из ре25 гистра 12. Дешифратор срабатывает и сигнал с его выхода открывает элементы И 99, 100, 105 и 106. Так как сигнал на шине 118 отсутствует, то два последних элемента не срабатывают. Сигнал BF1 на шине 115 также отсутствует, поэтому срабатывает элемент 100 И (от сигнала с элемента НЕ 111), сигнал с выхода которого через элемент ИЛИ 98 поступает на D-вход триггера 86. На С-вход этого триггера одновременно поступает сигнал RJSOB по шине 77, так что по переднему фронту этого сигнала в триггер 96 заносится 1. В результате сигнал KB (Команда выполнена) с выхода триггера 96 по шине 122 поступает в блок 14 формирования сигналов на элемент И 126, который открыт сигналом по шине 81. Сиг нал с выхода последнего поступает

5 на второй разряд магистрали состояния и воспринимается процессором ЭВМ при наличии сигнала Ответ в качестве реакции устройства, которое - может вырабатывать коды следующих

50 состояний:

код 000 - состояние Авария ; код 001 - состояние КВП (Команда выполняется);

код 010 - состояние KB (Команда

55 выполнена)$

код 111 - состояние КВТС (Ко30

35

40

манда выполнена, тояние).

есть текущее соеЗаметим, что в ответ на команды процессора НУ, ППБ, ПБ и ПБП устройство отвечает состояниями КВП или КВТС, на команду ВС - состояниями КБ, КВП или КВТС, на команды УС и ВТС - состоянием КВ.

Процессор ЭВМ, получив ат устройства состояние КБ, выставляет на информационной магистрали 43 код символа, который должен-быть напечатан ПчУ1, например, код цифры 7, команду ПБ на магистрали 76 и сигнал Вызов на шине 77. В ответ на это блок 8 формирует сигналы на шинах 81 и 82, причем последний (Ответ) поступает в процессор ЭВМ. Сигн ал по шине 81 riocTy пает в блок 14, который при наличии команды ПБ вырабатывает сигнал на шине 128. При наличии сигналов на шинах 81 и 128 и коде 00 на информационных входах дешифратора 130 (шины 114) блок 15 дешифрации канальных команд вырабатывает сигнал STB1 на шине 44. Последний поступае в блок 16, устанавливая в 1 триггер 140, и в блок 7 приема данных, разрешая занесение кода цифры 7 из магистрали 43 в регистр 35. В блоке 13 дешифрации состояний дешифратор 94 открыт сигналов по шине 80 (триггер 53 остался в состоянии 1), а на его информационные входы по шинам 114 приходит код 00, так что сигнал с его выхода открывает элементы И 99, 100, 105 и 106. При .наличии сигнала IBF1 на шине 115 срабатывает элемент И 99, сигнал с его выхода через элемент 97 ИЛИ поступает на D-вход триггера 95. По переднему фронту.сигнала Вызов в последний заносится 1, сигнал КБП с его выхода по шине 121 поступает в блок 14 и через элемент И 125 - на магистраль 129 состояния. Таким образом, процессор ЭВМ в ответ на команду ПБ получает состояние КВП.

В свою очередь БУ 1 выполняет микрокоманду выборки сигналов активизации, в результате чего в нем окажется код 00000001. В результате анализа выясняется, что необходимо выполнить микрокоманду вриема информации от процессора ЭВМ. Для этого в первом цикле в регистр 9 направления обмена засылается код 01. Во втором цикле БУ 1 формирует адрес 0000 на шинах 176, который поступае

на адресную магистраль 47. В этом случае блок 10 вырабатывает сигнал ПИ1, который по шине 48 поступает в блок 7.- Одновременно в последний

поступает сигнал Прием по шине 26 и код 00 по группе адресных входов. В результате сигнал с вьпсода . дешифратора 41 открьшает группу 38 элементов И и поступает на шину 49.

Содержимое регистра 35 через группу 38 поступает на магистраль 25 данных, откуда через коммутатор 25 заносится в БУ 1. Сигнал по шине 49 поступает на нулевой вход триггера

140, устанавливая его в состояние О, прекращая тем самым сигнал BF1. ho заднему фронту этого сигнала (через шину 115 и элемент НЕ 152) осуществляется установка в О триггера 146, если он находился в состоянии 1.

Следующей микрокомандой БУ 1 перешлет принятый байт (код цифры 7) в блок 18. Для этого в первом цикле

в регистр 9 занесется код Ю. Во втором цикле БУ 1 выставляет адрес 0020 на магистрали 47, в результате чего блок 10 формирует сигнал ПИ5, которьй по шине 92 поступает в блок

18. Дешифратор 158, на адресные входы которого поступает код 00, сраба- тьшает и своим сигналом разрешает занесение в регистр 155. Так как одновременно БУ 1 выставляет на магистрали 25 данных код цифры 7,

то этот код заносится в регистр 155 и начинает поступать в ПчУ1 по группе 159 выходов.

Следующей микрокомандой БУ 1 выставляет код управляющего сигнала в регистр 169 блока 20 аналогичйо описайному выше, В результате в ПчУ1 поступает управляющий сигнал печати и код цифры 7, так что оно начинает печатать эту цифру.

В то же самое время, после снятия сигнала IBF1 в блок 13 дешифрации состояний по шине 115 поступает низкий уровень, так что из открытых элементов И 99, 100, 105 и 106 срабатывает элемент И 100 (на него приходит высокий уровень с элемента НЕ 111), высокий потенциал с выхода которого через элемент ИЛИ 98 поступает на D-вход триггера 96, Процессор

ЭВМ посылает очередную команду ВС по магистрали 76,и сигнал Вызов по шине 77 передним фронтом обеспечивает занесение 1 в триггер 96 и О в

триггер 95. Высокий потенциал с выхода триггера 96 по шине 122 поступает в блок 14, который при наличии сигнала на шине 81 с помощью элемента И 126 формирует на магистрали 129 код 010 - состояние КВ.

Процессор анализирует этот код и определив, что его команда вьтол- нена, активизирует третий канал и посылает в ПчУЗ код очередного сим- вола, напр имер, буквы Ф. Все эти действия полностью аналогичны предыдущим.

Вначале процессор выставляет на информационной магистрали 43 код 14 и посылает команду УС. В результате триггер 53 оказывается в состоянии 1, в регистр 12 номера канала заносится код 10, а блоки 13 и 14 вырабатывают состояние KB (при этом сигнал с дешифратора 94 открывает элементы И 103, 104, 109 и 110, из которых срабатывает первый под воздействием сигнала с элемента НЕ 113) Далее процессов ЭВМ выставляет на информационной магистрали 43 код буквы Ф и посыпает команду ПВ и сигнал Вызов. В результате совместной работы блоки 14 и 15 вырабатываю сигнал ТВЗ, который по шине 46 устанавливает в 1 триггер 142 и разрешает занесение в регистр 37. В этот момент блок 14 выставляет на магистрали 129 состояний код,состояния КВП.

В то же самое время, окончив работу с ПчУ1, БУ 1, как и ранее, выполняет микрокоманду выборки сигналов активизации, в результате чего в нем окажется код 00000100. Следовательно, надо выполнить микрокоманду приема информации от процессора. В результате ее выполнения в ВУ 1 окажется код буквы Ф, триггер 142 будет сброшен (а за ним и триггер 148 по цепи шина 117- элемент НЕ 154, если в нем была 1), так что по команде ВС процессор в качестве ответа получит состояние КВ. Далее МПЭ 1 выполнит еще две микрокоманды, по первой из которых код буквы Ф занесется в регистр 157 блока 18 выдачи данных, а по второй код управляющего сигнала занесется в регистр 171 блока 20. В результате в ПчУЗ начнут поступать управляющий сигнал печати и код бук

ВЫ

Ф.

так что оно начнет печатать

эту букву.

5 0 51

5

0

5

5

0

Вслед за этим БУ 1 может опросить второй канал (не появилось ли BF2) и при отсутствии его инициации заняться проверкой состояний ПчУ1 и ПчУЗ (аналогично описанному выше для ПчУ2).

Так как процессор ЭВМ получил состояние KB, то он может вновь установить связь с первым каналом и выдать код следующего символа для ПчУ1, затем для ПчУЗ и т.д. Работа каждого из каналов аналогична друг другу. При этом МПЭ 1 анализирует сигналы IBF1-IBF3, НУ1-НУЗ и состояния ПчУ, обеспечивая одновременное функционирование последних.Процессор ЭВМ, анализируя состояния устройства, посылает очередной символ в данный канал только при наличии состояния КВ.

Однако в процессе работы устройства вывода могут возникать непредвиденные ситуации. Так, например, в ПчУ может закончиться или оборваться бумажный носитель. В этом случае ПчУ выставит соответствующий ригнал на свои шины состояний. Пусть, например, это возникнет в ПчУЗ.

Тогда при очередном опросе состояния ПчУЗ в БУ 1 занесется код, из анализа которого будет следовать, что в ПчУЗ оборвалась или закончи- . лась бумага. В соответствии со своей программой БУ 1 выдает код текущего состояния. Для этого в первом цикле соответствующей микрокоманды в регистр 9 заносится код 10. Во втором цикле БУ 1 выставляет на магистрали 25 данных код текущего состояния, на шине 33 - сигнал Запись и на адресной магистрали 47 - адрес 0004. В соответствии с этим блок 10 дешифрации ввода-вывода формирует сигнал Ш12, который по шине 34 поступает в блок б вьщачи текущего состояния. Элемент И 30 срабатывает, сигнал с его выхода заносит 1 в триггер 29 и разрешает занесение кода текущего состояния из магистрали 25 данных в регистр 27 (заносится четыре младших разряда). С этого момента сигнал DBF с выхода триггера 29 поступает на разряд Д2 магистрали 25 данных. БУ 1 может выставить для ПчУЗ новый управляющий сигнал, например сигнал остановки. Однако, в отличии от ранее рассмотренных случаев выдачи управляю19

щего сигнала в ПчУ1 на этот раз в разряде .Д8 будет присутствовать

II 4 II

I

в первом цикле микрокоманды вьщачи управляющего сигнала, как и ранее, в регистр 9 заносится код 10. Во втором цикле БУ 1 выставляет на адресной магистрали 47 восьмеричный код 0012 и не формирует сигнал Прием -на шине 26, так что код 1ХХХХХХХ (где ХХХХХХХ - собственно управляющий сигнал для ПчУ) занесется в регистр 171 блока 20. В результате управляющий сигнал поступит в ПчУЗ по группе 175 выходов и вызовет его остановку, а старший, восьмой разряд с выхода регистра 171 по шине 120 поступит в блок 13 дешифрации состояний.

Далее, когда при очередной активизации третьего канала сигнал с выхода дешифратора 94 откроет эле- MSHtbi И 103, 104, 109 и ИО срабог тают элементы И 109 и 110, так что по переднему фронту сигнала Вызов на шине 77 установятся в 1 сразу оба триггера 95 и 96. Сигналы КВП и КВ с их выходов по шинам 121 и 122 поступают в блок 14, в рв зультате чего с помощью элемента И 127 в магистраль 129 будет вьщано состояние; КВТС.

Получив его, процессор ЭВМ посылает команду ВТС, дешифрируя которую, дешифратор 123 формирует сигнал по шине 32, который устанавливает в 0 триггер. 29 и открьшает группу 28 элементов И. В результате код текущего состояния из регистра 27 через группу 28 элементов И поступает на магистраль 31 текущего состояния.

20678820

В течение всего этого времени (от момента выдачи кода текущего состояния до гашения триггера 29) БУ 1 опрашивает магистраль 25 дан5 ных для проверки наличия 1 в разряде Д2 - сигнала DBF. Как только процессор ЭВМ заберет код текущего, состояния, триггер 29 установится в О, сигнал DBF исчезнет и при оче10 редном анализе содержимого магистрали 25 данных БУ 1 получит информацию об этом. Далее в соответствии с программой БУ 1 может, вновь проверить состояние ПчУЗ и повторить

15 все снова. Когда причина этого будет устранена (например, вставлена бумага) , при очередном анализе БУ 1 обнаружит это и вьщаст новый управляющий код в блок 20, который будет

20 иметь вид ОХХХХХХХ. В результате этого в магистраль 129 будет выдано состояние KB (при очередной команде ВС от процессора) и работа устройства продолжится дальше.

25

Очевидно, что в блоках приема данных 7, дешифрации состояний 13, триггеров 17 и регистровой памяти 18 второй и третий каналы функцио30 нируют аналогично первому.

Таким образом, изобретение обеспечивает одновременную работу нескольких устройств вывода, что повышает его пропускную способность по сравнению с известным устройством во столько же раз. Кроме того, оно обеспечивает одновременную ра- боту с устройствами вывода разного

35

/ типа, что следует из принципов

его функционирования и особенностей построения.

зВ

э

.

:tS

s

«М.4

Фиг.6

/22

36

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Устройство для отображения информации | 1986 |

|

SU1506478A1 |

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Устройство для сопряжения процессора с группой блоков памяти | 1987 |

|

SU1587518A1 |

| Многоканальное микропрограммное устройство ввода-вывода | 1983 |

|

SU1104500A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство для обмена информацией | 1982 |

|

SU1118992A1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

ПО

Ф{4г.7

т

8

.Ю

Фиг.12

Редактор В. Иванова

Составитель С. Пестмал

Техред Т.Тулик Корректор Л. Патай

Заказ 8714/50 Тираж 673 Подписное .-... ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Щ оектная,4

А«./5

| Устройство для сопряжения | 1980 |

|

SU947849A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения абонентов с цвм | 1974 |

|

SU567169A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| ,(54)(57) 1 | |||

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕ- НИЯ ПРОЦЕССОРА С УСТРОЙСТВАМИ ВЫВОДА, содержащее блок управления, коммутатор данных, блок приема данных, регистр направления обмена, блок вьщачи текущего состояния, блок вьщеления адреса устройства, блок постоянной памяти, блок опера- тивной памяти, группу элементов И, причем группа управляющих входов блока управления подключена к управляющему выходу процессора, группы информационных входов блока приема данных и блока выделения адреса устройства подключены к информационному выходу процессора, группа информационных выходов блока выдачи текущего состояния подключена к входу текущего состояния процессора, вход вызова блока вьщеления адреса устройства подключен к выходу запроса процессора, первый выход блока выделения адреса устройства подключен к входу ответа процессора, группа управляющих входов блока вьщеле- ния адреса устройства подключена к выходу команд процессора, при этом группа адресных выходов блока управления соединена с первыми входами элементов И группы, выходы которых соединены с группой адресных входов блока постоянной памяти, блока оперативной памяти и блока приема данных, группа командных входов-выходов блока управления соединена с первой группой информационных входов-выходов коммутатора данных, вторая группа информационных входов- выходов которого соединена с группой информационных выходов блока постоянной памяти, блока приема данных, группой информационных входов регистра направления обмена, блока выдачи текущего состояния, группой информационных входов-выходов блока оперативной памяти, вх од записи которого соединен с первым управляющим входом блока выдачи текущего состояния и выходом записи блока управления, выход отсутствия захвата которого соединен с вторыми входами элементов И группы, выход синхронизации направления обмена соединен с входом занесения регистра, выход приема блока управления соединен с разрешающим входом блока постоянной памяти, управляющим входом коммутатора данных и первым управляющим входом блока приема данных, отличающееся тем, что, с целью повьшения пропускной способности устройства за счет его одновременной работы с несколькими устройствами вывода одного или разного типа, в него введены блок дешифрации ввода-вывода, дешифратор памяти, регистр номера канала, блок деto о Од sl 00 00 | |||

Авторы

Даты

1986-01-23—Публикация

1984-06-06—Подача