Преобразователь предназначен для использования в системах автоматики и относится к области вычислительной техники.

Известны преобразователи двоичного кода в десятичный, содержащие сдвиговый регистр опроса, регистр двоичного кода, собирательные схемы перевода весовых значений каждого двоичного разряда в соответствующее весовое значение десятичного разряда, собирательные схемы разрещения формирования соответствующего десятичного разряда, генератор импульсов и последовательный десятичный декадный счетчик. Однако эти преобразователи имеют большое время преобразования, которое определяется временем последовательного преобразования младщих разрядов.

Цель изобретения - уменьщение времени преобразования двоичного кода в десятичный. Для этого в преобразователь введены по числу декад десятичного счетчика управляемые электронные ключи, первые входы которых соединены с вторым входом преобразователя и с входом делителя частоты, вторые входы - с соответствующими выходами собирательных схем разрещения формирования соответствующего десятичного разряда, третьи входы - с соответствующими выходами дополнительных сдвиговых регистров, а выходы - с соответствующими входами декад последовательного десятичного декадного счетчика и шинами

сдвига дополнительных сдвиговых регистров. Установочные входы последних подключены соответственно к выходам собирательных схем перевода весовых значений каждого двоичного разряда в соответствующее весовое значение десятичного разряда.

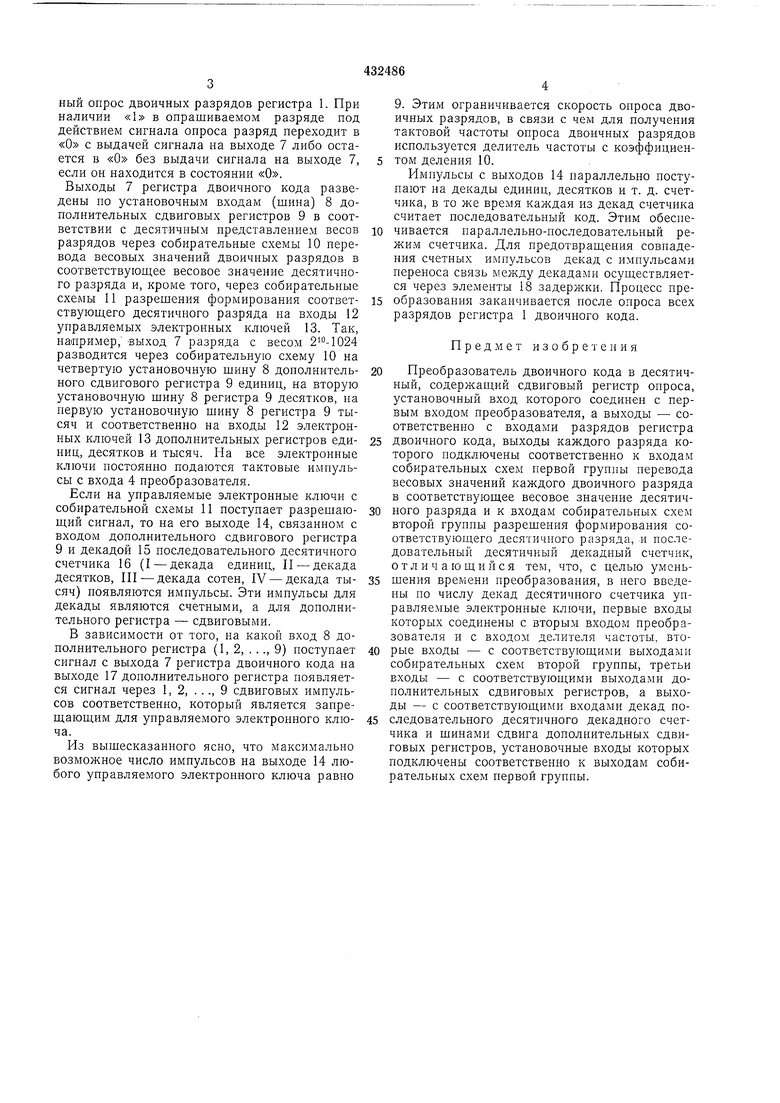

На чертеже показана схема предлагаемого преобразователя.

Сущность изобретения состоит в том, что значение веса опрашиваемого двоичного разряда параллельно переносится в десятичном коде по установочным входам в дополнительные регистры сдвига, после чего с выходов управляемых электронных ключей импульсы, количество которых определяется числом, занесенным Б данный регистр, поступают на входы соответствующих декад десятичного счетчика для суммирования. Поскольку суммирование декадами счетчика производится одновременно, то для исключения совпадения счетных импульсов с импульсами переноса последние подаются через элементы задержки.

Преобразуемое число вводится в регистр 1 двоичного кода. На сдвиговый регистр 2 опроса через вход 3 преобразователя подается команда «пуск. Под действием сдвиговых импульсов, поступающих через вход 4 преобразователя и делитель 5 частоты на регистр 2, на каждом из его выходов 6 поочередно появляются сигналы, производящие последовательный опрос двоичных разрядов регистра 1. При наличии «1 в опрашиваемом разряде под действием сигнала опроса разряд переходит в «О с выдачей сигнала на выходе 7 либо остается в «О без выдачи сигнала на выходе 7, если он находится в состоянии «О. Выходы 7 регистра двоичного кода разведены по установочным входам (шина) 8 дополнительных сдвиговых регистров 9 в соответствии с десятичным представлением весов разрядов через собирательные схемы 10 перевода весовых значений двоичных разрядов в соответствующее весовое значение десятичного разряда и, кроме того, через собирательные схемы 11 разрешения формирования соответствующего десятичного разряда на входы 12 управляемых электронных ключей 13. Так, например; -выход 7 разряда с весом разводится через собирательную схему 10 на четвертую установочную шину 8 дополнительного сдвигового регистра 9 единиц, на вторую установочную шину 8 регистра 9 десятков, па первую установочную шину 8 регистра 9 тысяч и соответственно на входы 12 электронных ключей 13 дополнительных регистров единиц, десятков и тысяч. На все электронные ключи постоянно подаются тактовые импульсы с входа 4 преобразователя.

Если на управляемые электронные ключи с собирательной схемы 11 поступает разрешающий сигнал, то на его выходе 14, связанном с входом дополнительного сдвигового регистра 9 и декадой 15 последовательного десятичного счетчика 16 (I - декада единиц, II - декада десятков, III-декада сотен, IV - декада тысяч) иоявляются импульсы. Эти импульсы для декады являются счетными, а для дополнительного регистра - сдвиговыми.

В зависимости от того, па какой вход 8 дополнительного регистра (1, 2, . .., 9) поступает сигнал с выхода 7 регистра двоичного кода на выходе 17 дополнительного регистра появляется сигнал через 1, 2, . .., 9 сдвиговых импульсов соответственно, который является запрещающим для управляемого электронного ключа.

Из вышесказанного ясно, что максимально возможное число импульсов на выходе 14 любого управляемого электронного ключа равно

9. Этим ограничивается скорость опроса двоичных разрядов, в связи с чем для получения тактовой частоты опроса двоичных разрядов используется делитель частоты с коэффициентом деления 10.

Импульсы с выходов 14 параллельно поступают на декады единиц, десятков и т. д. счетчика, в то же время каждая из декад счетчика считает последовательный код. Этим обеспечивается параллельно-последовательный режим счетчика. Для предотвращения совпадения счетных импульсов декад с импульсами переноса связь между декадами осуществляется через элементы 18 задержки. Ироцесс преобразования заканчивается после опроса всех разрядов регистра 1 двоичного кода.

Иредмет изобретения

Преобразователь двоичного кода в десятичный, содержащий сдвиговый регистр опроса, установочный вход которого соединен с первым входом преобразователя, а выходы - соответственно с входами разрядов регистра

двоичного кода, выходы каждого разряда которого подключены соответственно к входам собирательных схем первой группы перевода весовых значений каждого двоичного разряда в соответствующее весовое значение десятичного разряда и к входам собирательных схем второй группы разрешения формирования соответствующего десятичного разряда, и последовательный десятичный декадный счетчик, отличающийся тем, что, с целью уменьщения времени преобразования, в него введены по числу декад десятичного счетчика управляемые электронные ключи, первые входы которых соединены с вторым входом преобразователя и с входом делителя частоты, вторые входы - с соответствующими выходами собирательпых схем второй группы, третьи входы - с соответствующими выходами дополнительных сдвиговых регистров, а выходы - с соответствующими входами декад последовательного десятичного декадного счетчика и шинами сдвига дополнительных сдвиговых регистров, установочные входы которых подключены соответственно к выходам собирательных схем первой группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования двоичного кода в двоично-десятичный | 1976 |

|

SU641441A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1978 |

|

SU771660A1 |

| Устройство для преобразования кодов | 1977 |

|

SU744544A1 |

| Устройство для преобразования двоичного кода в двоично-десятичный | 1977 |

|

SU898417A2 |

| Преобразователь двоичного кода в двоично-десятичный | 1983 |

|

SU1130858A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1976 |

|

SU646327A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1981 |

|

SU993244A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1997 |

|

RU2130199C1 |

| Преобразователь перемещения в код | 1982 |

|

SU1043701A1 |

Авторы

Даты

1974-06-15—Публикация

1971-12-21—Подача