СП

ьэ

о

tsD

00

«чД

I Изобретение относится к вычисли- Цельной технике и предназначено для построения запоминающих устройств в Цифровой вычислительной технике (ЦВМ : Целью изобретения является повыше 1ия быстродействия запоминающего уст Ьойства.

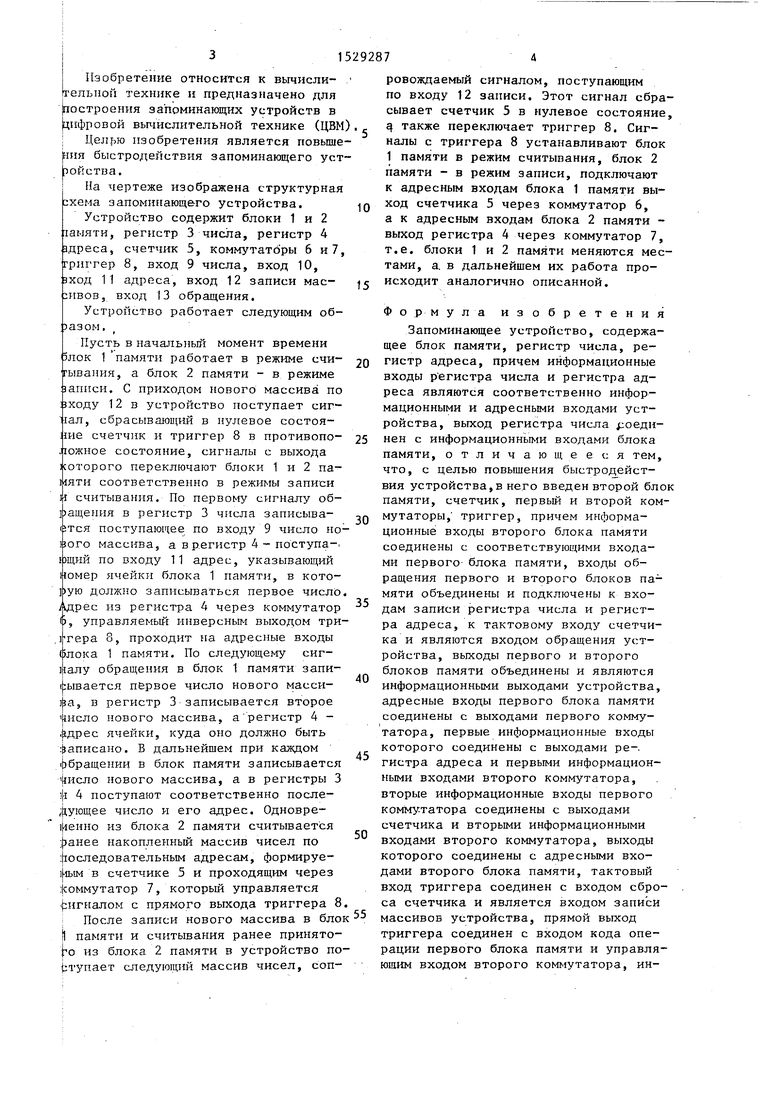

На чертеже изображена структурная :хема запоми ающего устройства.

Устройство содержит блоки 1 и 2 памяти, регистр 3 числа, регистр 4 адреса, счетчик 5, коммутаторы 6 и 7, триггер 8, вход 9 числа, вход 10, зход 11 адреса, вход 12 записи массивов, вход 13 обращения.

Устройство работает следующим об- эазом.

Пусть в началь}1ЬП1 момент времени 5лок 1 памяти работает в режиме счи- ъшания, а блок 2 памяти - в режиме тписи. С приходом нового массива по :зходу 12 в устройство поступает сиг- шл, сбрасывающий в нулевое состоя- ше счетчик и триггер 8 в противопо-

соторого переключают блоки 1 и 2 памяти соответственно в режимы записи I считывания. По первому сигналу об- ащения в регистр 3 числа записывается поступающее по входу 9 число но- ого массива, а в регистр 4 - поступа-. иций по входу 11 адрес, указывающий номер ячейки блока 1 памяти, в кото- )ую должно записываться первое число у1дрес из регистра 4 через коммутатор Ф, управляемый инверсным выходом три- |гера 8, проходит на адресные входы флока 1 памяти. По следующему сиг- алу обращения в блок 1 памяти запи- (Ьывается первое число нового масси- фа, в регистр 3 записывается второе |1исло нового массива, а регистр 4 - |1дрес ячейки, куда оно должно быть :Иписано. В дальнейшем при каддом (Обращении в блок памяти записывается нового массива, а в регистры 3 :|i 4 поступают соответственно после- ;|1ующее число и его адрес. Одновре- из блока 2 памяти считывается :j)aHee накопленньй массив чисел по :11оследовательным адресам, формируе- в счетчике 5 и проходящим через }|соммутатор 7, который управляется Сигналом с прямого выхода триггера 8 После записи нового массива в бло || памяти и считывания ранее принято- f o из блока 2 памяти в устройство по Ьтупает следующий массив чисел, соп5

0

5

0

5

0

5

0

5

0

5

ровождаемый сигналом, поступающим по входу 12 записи. Этот сигнал сбрасывает счетчик 5 в нулевое состояние, щ также переключает триггер 8. Сигналы с триггера 8 устанавливают блок 1 памяти в режим считывания, блок 2 памяти - в режим записи, подключают к адресным входам блока 1 памяти выход счетчика 5 через коммутатор 6, а к адресным входам блока 2 памяти - выход регистра 4 через коммутатор 7, т.е. блоки 1 и 2 памяти меняются местами, а. в дальнейшем их работа происходит аналогично описанной.

Формула изобретения Запоминающее устройство, содержащее блок памяти, регистр числа, регистр адреса, причем информационные входы р егистра числа и регистра адреса являются соответственно информационными и адресными входами устройства, выход регистра числа ;оеди- нен с информационными входами блока памяти, отличающееся тем, что, с целью повышения быстродействия устройства,в него введен второй блок памяти, счетчик, первый и второй коммутаторы, триггер, причем информационные входы второго блока памяти соединены с соответствующими входами первого блока памяти, входы обращения первого и второго блоков памяти объединены и подключены к входам записи регистра числа и регистра адреса, к тактовому входу счетчика и являются входом обращения устройства, выходы первого и второго блоков памяти объединены и являются информационными выходами устройства, адресные входы первого блока памяти соединены с выходами первого коммутатора, первые информационные входы которого соединены с выходами ре-, гистра адреса и первыми информационными входами второго коммутатора, вторые информационные входы первого коммутатора соединены с выходами счетчика и вторыми информационными входами второго коммутатора, выходы которого соединены с адресными входами второго блока памяти, тактовый вход триггера соединен с входом сброса счетчика и является входом записи массивов устройства, прямой выход триггера соединен с входом кода операции первого блока памяти и управляющим входом второго коммутатора, ин515292876

версный выход триггера соединен с памяти и управляющим входом второго входом кода операции второго блока коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1987 |

|

SU1479954A1 |

| Устройство для упорядочивания чисел | 1983 |

|

SU1144103A1 |

| Запоминающее устройство с коррекцией программы | 1986 |

|

SU1347097A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для связи процессора с запоминающим устройством | 1983 |

|

SU1083196A1 |

| Устройство управления | 1984 |

|

SU1171790A1 |

| Оперативное запоминающее устройство | 1983 |

|

SU1095233A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1987 |

|

SU1462408A1 |

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам. Цель изобретения - повышение быстродействия устройства за счет возможности одновременной записи и считывания информации. Устройство содержит блоки памяти 1 и 2, регистр числа 3, регистр адреса 4, счетчик 5, коммутаторы 6 и 7, триггер 8. В устройство введены второй блок памяти, два коммутатора, счетчик и триггер, что позволяет одновременно записывать информацию в один из блоков памяти и считывать ранее записанную из другого блока памяти. 1 ил.

| Каган Б.М.Электронные вычислительные машины | |||

| М., 1979, с.112 | |||

| Шигин А.Г | |||

| и Дерюгин А,А | |||

| Цифровые вычислительные машины | |||

| М., 1975, с | |||

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

Авторы

Даты

1989-12-15—Публикация

1987-11-17—Подача