которого и нулевой вход триггера являются входами блока,

3. Устройство по пп. 1 и 2, отличающееся тем, что блок анализа режимов содержит сумматор по модулю два и элементы И с первого по третий, выходы которых подключены

к одним из входов сумматора по модулю два, другие входы которого и первые входы элементов И с первого по третий являются одними из входов блока, другими входами и выходами которого являются соответственно вторые входы элементов И и выходы сумматора по модулю два.

| название | год | авторы | номер документа |

|---|---|---|---|

| Долговременное запоминающее устройство | 1979 |

|

SU765878A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для обмена информацией | 1982 |

|

SU1118992A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

| Запоминающее устройство | 1979 |

|

SU849301A1 |

| Микро-ЭВМ | 1982 |

|

SU1124316A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Устройство для обучения | 1987 |

|

SU1559366A1 |

| Запоминающее устройство | 1987 |

|

SU1495849A1 |

1. ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее первый дешифратор адреса, одни из входов которого подключены к выходам старших разрядов первого регистра адреса, а выходы - к адресным входам накопителей, информационные входы которых соединены с выходами формирователей разрядных токов, а выходы - с входами усилителей считывания, регистр числа, одни из входов которого соединены с выходами усилителей считывания, а выходы - с информационными входами коммутатора и формирователей разрядных токов, и блок управления, первый выход которого подключен к управляющим входам усилителей считывания и первому управляющему входу первого дешифратора адреса, причем второй и третий выходы блока управления соединены соответственно с управляющими входами усилителей считывания и с первым управляющим входом регистра числа, а четвертый и пятый выходы блока управления - соответственно с одним из управляющих входов коммутатора и с управляющим входом первого регистра числа, входы с первого по третий и шестой выход блока управления являются соответственно входами обращения, записи, считывания и выходом готовности устройства, информационными входами и выходами которого являются соответственно другие входы регистра числа и выходы коммутатора, адресными входами устройства являются входы первого регистра адреса, отличающееся тем, -что, с целью повышения быстродействия устройства, в него введены второй регистр адреса, блок сравнения и второй дешифратор адреса, причем входы второго регистра адреса подключеныеК выходам старших разрядов первого регистра адреса и одним из входов блока сравнения, другие входы которого соединены с выходами второго регистра адреса и другими входами первого дешифратора адреса, второй управляющий вход которого и выход блока сравнения соединены соответственно с вторым выходом и с четвертым входом блока управления, седьмой выход которого подключен к управляющему входу второго регистра числа, а восьмой выход - к управляющему входу второго дешифратора адреса, выход которого соединен с вторым управляющим входом регистра числа, а входы подключены к выходам младших разрядов первого регистра адреса и другим уп(Л равляющим входам коммутатора. 2. Устройство по п. 1, отличающееся тем, что блок управления содержит накопитель микрокоманд, блок анализа режимов, формирователь сигнала блокировки, триггер, элемент ИЛИ-НЕ, группу элементов И, элемент задержки и дешифратор микрокоманд, выходы с первого по восьмой которого являются ел ю выхода.ми блока, а входы соединены с одними из выходов накопителя микрокоманд, другие выходы которого подключены к одним 00 из входов блока анализа режимов, причем оо единичный вход триггера соединен с выходом формирователя сигнала блокировки, вход которого подключен к шестому выходу дешифратора, микрокоманд, выходы которого, кроме шестого, соединены соответственно с первыми входами элементов И группы, вторые входы которых подключены к выходам элемента задержки, а выходы - к первому входу элемента ИЛИ-НЕ, второй вход которого соединен с прямым выходом триггера, а выход - с входом элемента задержки и управляющим входом накопителя микрокоманд, входы которого подключены к выходам блока анализа режимов, другие входы

Изобретение относится к вычислительной технике и может быть использовано для построения многоблочной системы оперативной памяти ЦВМ. Известно запоминающее устройство, которое содержит накопитель, усилители воспроизведения, регистры адреса и числа регистра признаков операций, дешифраторы адреса и признаков операций, формирователи разрядных токов, блок управления, генератор, распределитель, триггеры, элементы ИЛИ, элементы И-ИЛИ, элементы И, элементы задержки 1. Недостатком известного устройства является низкое быстродействие. Наиболее близким к изобретению является оперативное запоминающее устройство (ОЗУ), содержащее блоки памяти, дешифратор номера блока памяти, входы-и выходы которого соединены соответственно с адресными входами и с управляющими входами блоков памяти, и блок управления 2. Однако прототипу присуще низкое быстродействие, обусловленное необходимостью производить регенерацию при каждом обращении к устройству. Цель изобретения - повышение быстродействия оперативного запоминающего устройства. Поставленная цель достигается тем, что в оперативное запоминающее устройство, со держащее первый дешифратор адреса, одни из входов которого подключены к выходам старщих разрядов первого регистра адреса, а выходы - к адресным входам накопителей информационные входы которых соединены с выходами формирователей разрядных токов, а выходы - с входами усилителей считывания, регистр числа, одни из входов которого соединены с выходами усилителей считывания, а выходы - с информационными входами коммутатора и формирователей разрядных токов, и блок управления, первый выход которого подключен к управляющим входам усилителей считывания и первому управляющему входу первого дешифратора адреса, причем второй и третий выходы блока управления соединены соответственно с управляющими входами усилителей считывания и с первым управляющим входом регистра числа, а четвертый и пятый выходы блока управления - соответственно с одним из управляющих входов коммутатора и с управляющим входом первого регистра числа, входы с первого по третий и щестой выход блока управления являются соответственно входами обращения, записи, считывания и выходом готовности устройства, информационными входами и выходами которого являются соответственно другие входы регистра числа и выходы коммутатора адресными входами устройства являются входы первого регистра адреса, введены второй регистр адреса, блок сравнения и второй дешифратор адреса, причем входы второго регистраадреса подключены к выходам старщих разрядов первого регистра адреса и одним из входов блока сравнения, другие входы которого соединены с выходами второго регистра адреса и другими входами первого дещифратора адреса, второй управляющим вход которого и выход блока сравнения соединены соответственно с вторым выходом и с четвертым входом блока управления, седьмой выход которого подключен к управляющему входу второго регистра числа, а восьмой выход - к управляющему входу второго дешифратора адреса, выход которого соединен с вторым управляющим входом регистра числа, а входы подключены к выходам младщих разрядов первого регистра адреса и другим управляющим входам коммутатора. Блок управления содержит накопитель микрокоманд, блок анализа режимов, формирователь сигнала блокировки, триггер, элемент ИЛИ-НЕ, группу элементов И, элемент задержки и дешифратор микрокоманд, выходы с первого по восьмой которого являются выходами блока, а входы соединены с одними из выходов накопителя микрокоманд, другие выходы которого подключены к одним из входов блока анализа режимов, причем единичный вход триггера соединен с выходом формирователя сигнала блокировки, вход которого подключен к щестому выходу дещифратора микрокоманд, выходы которого, кроме щестого, соединены соответственно с первыми входами элементов И группы, вторые входы которых подключены к выходам элемента задержки, а выходы - к первому входу элемента ИЛИ-НЕ, второй вход которого соединен с прямым выходом триггера, а выход - с входом элемента задержки и управляющим входом накопителя микрокоманд, входы которого подключены к выходам блока анализа режимов, другие входы которого и нулевой вход триггера являются входами блока.

Блок анализа режимов содержит сумматор по модулю два и элементы И с первого по третий, выходы которых подключены к одним из входов сумматора по модулю два, другие входы которого и первые входы элементов И с первого по третий являются одними из входов блока, другими входами и выходами которого являются соответственно вторые входы элементов И и выходы сумматора, по модулю два.

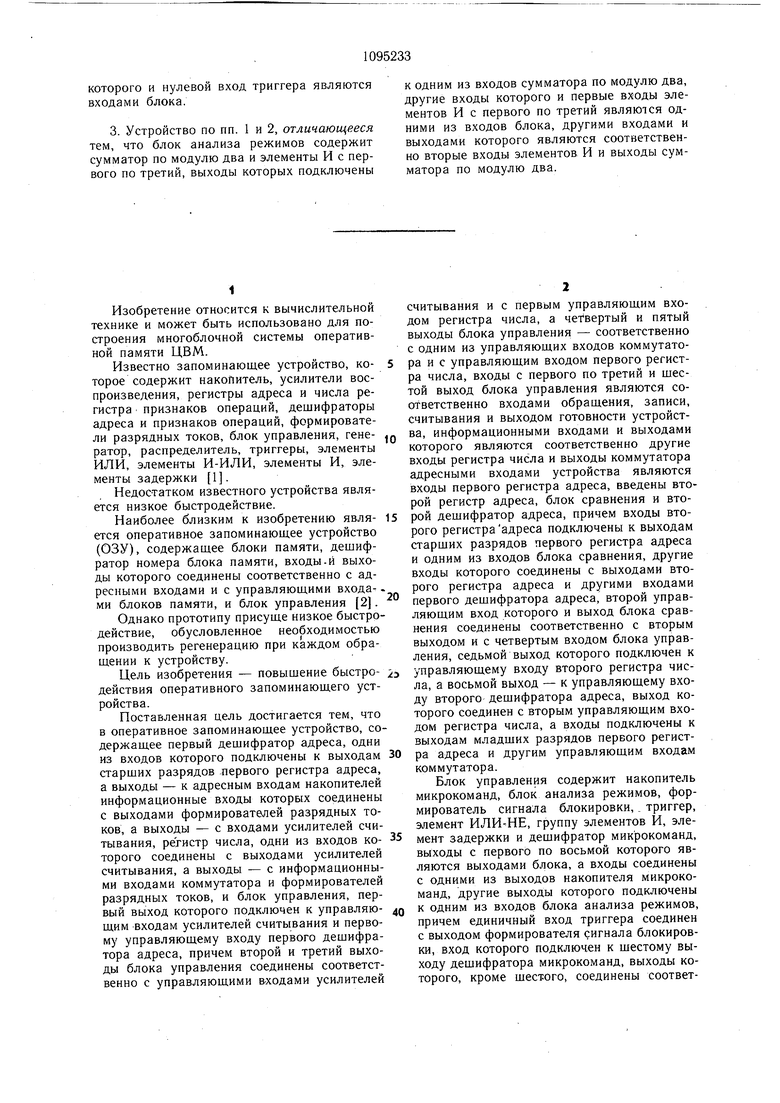

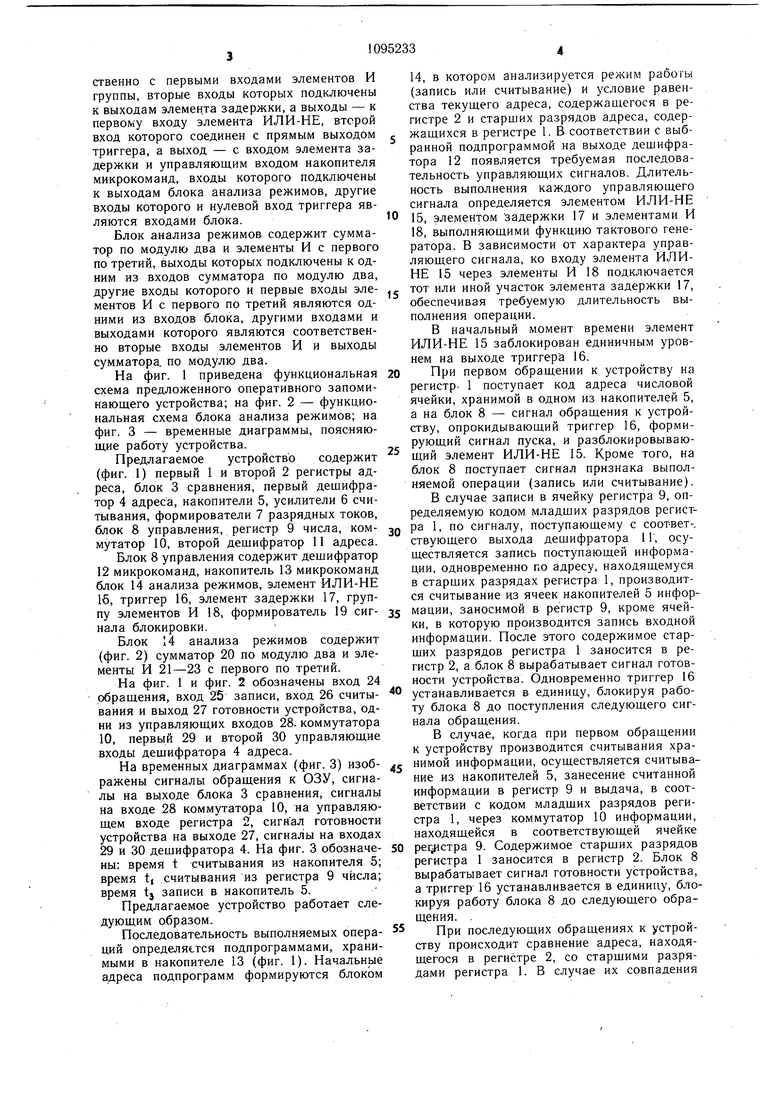

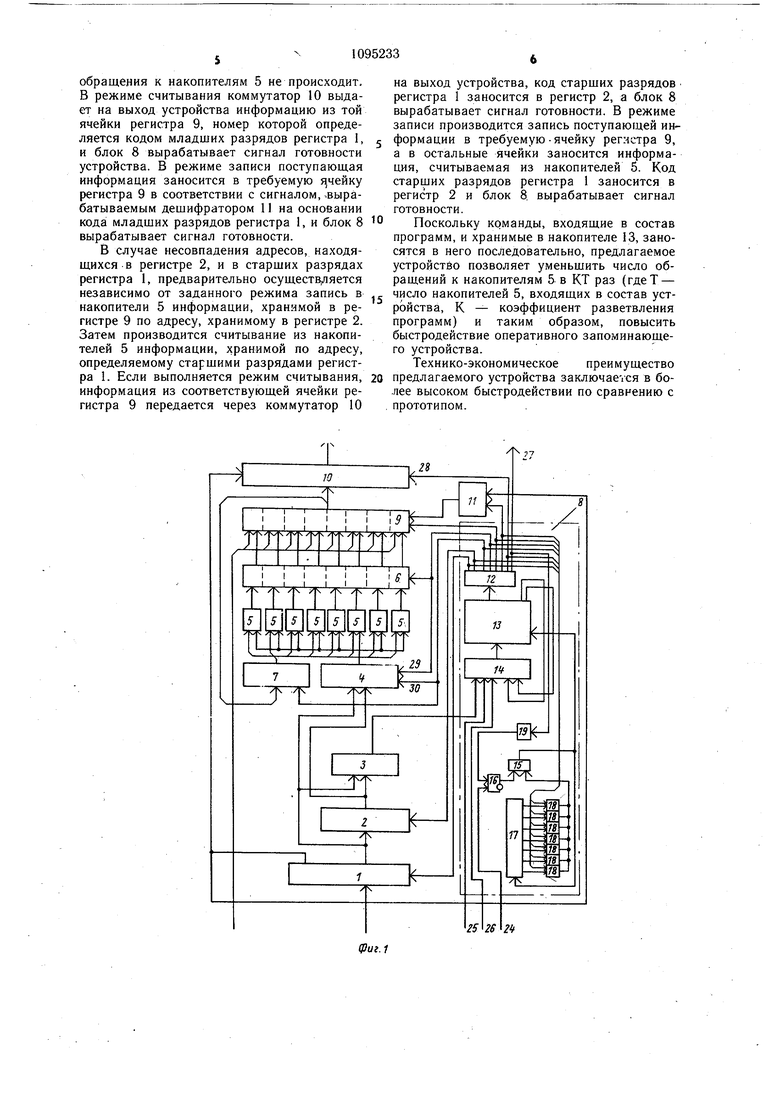

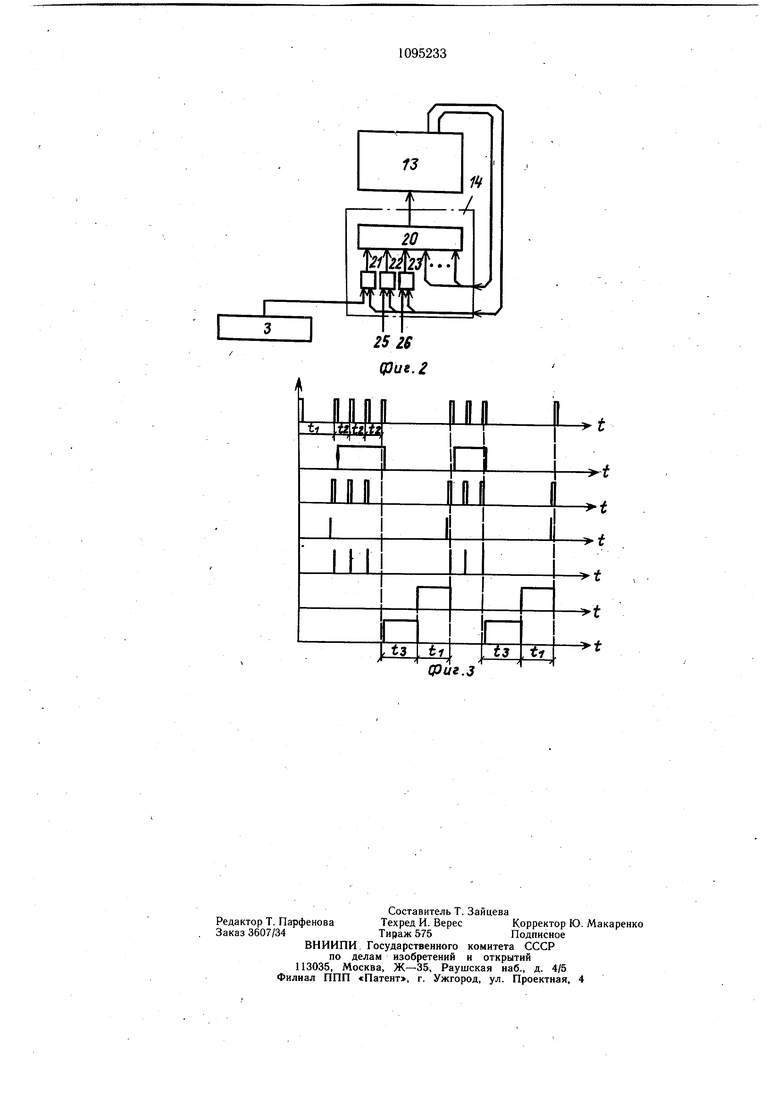

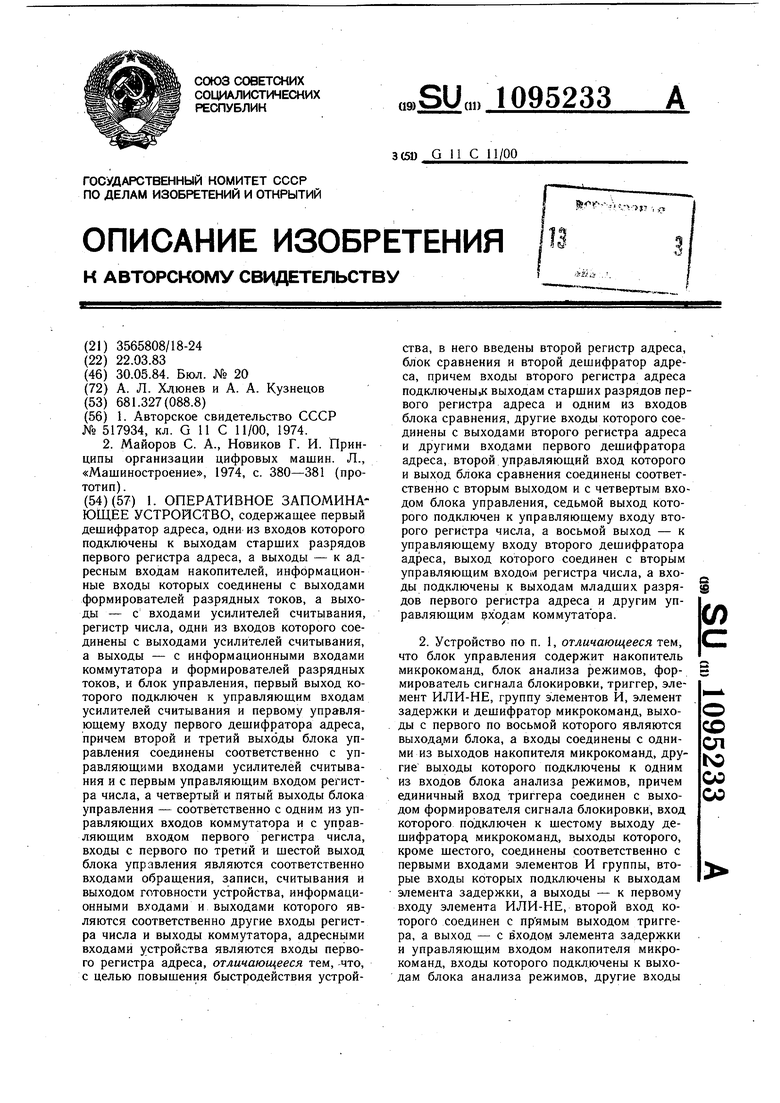

На фиг. 1 приведена функциональная схема предложенного оперативного запоминающего устройства; на фиг. 2 - функциональная схема блока анализа режимов; на фиг. 3 - временные диаграммы, поясняющие работу устройства.

Предлагаемое устройство содержит (фиг. 1) первый 1 и второй 2 регистры адреса, блок 3 сравнения, первый дешифратор 4 адреса, накопители 5, усилители 6 считывания, формирователи 7 разрядных токов, блок 8 управления, регистр 9 числа, коммутатор 10, второй дешифратор 11 адреса.

Блок 8 управления содержит дешифратор 12 микрокоманд, накопитель 13 микрокоманд блок 14 анализа режимов, элемент ИЛИ-НЕ 16, триггер 16, элемент задержки 17, группу элементов И 18, формирователь 19 сигнала блокировки.

Блок 14 анализа режимов содержит (фиг. 2) сумматор 20 по модулю два и элементы И 21-23 с первого по третий.

На фиг. 1 и фиг. 2 обозначены вход 24 обращения, вход 25 записи, вход 26 считывания и выход 27 готовности устройства, одни из управляющих входов 28. коммутатора 10, первый 29 и второй 30 управляющие входы дещифратора 4 адреса.

На временных диаграммах (фиг. 3) изображены сигналы обращения к ОЗУ, сигналы на выходе блока 3 сравнения, сигналы на входе 28 коммутатора 10, на управляющем входе регистра 2, сигнал готовности устройства на выходе 27, сигналы на входах 29 и 30 дешифратора 4. На фиг. 3 обозначены: время t считывания из накопителя 5; время tj считывания из регистра 9 числа; время tj записи в накопитель 5.

Предлагаемое устройство работает следуюш,им образом.

Последовательность выполняемых операций определяется подпрограммами, хранимыми в накопителе 13 (фиг. 1). Начальньш адреса подпрограмм формируются блоком

14,в котором анализируется режим работы (запись или считывание) и условие равенства текущего адреса, содержащегося в регистре 2 и старших разрядов адреса, содержащихся в регистре 1. В соответствии с выбранной подпрограммой на выходе дешифратора 12 появляется требуемая последовательность управляющих сигналов. Длительность выполнения каждого управляющего сигнала определяется элементом ИЛИ-НЕ

15,элементом задержки 17 и элементами И 18, выполняющими функцию тактового генератора. В зависимости от характера управляющего сигнала, ко входу элемента ИЛИНЕ 15 через элементы И 18 подключается тот или иной участок элемента задержки 17, обеспечивая требуемую длительность выполнения операции.

В начальный момент времени элемент ИЛИ-НЕ 15 заблокирован единичным уровнем на выходе триггера 16.

При первом обращении к устройству на регистр. 1 поступает код адреса числовой ячейки, хранимой в одном из накопителей 5, а на блок 8 - сигнал обращения к устройству, опрокидывающий триггер 16, формирующий сигнал пуска, и разблокировывающий элемент ИЛИ-Н1Е 15. Кроме того, на блок 8 поступает сигнал признака выполняемой операции (запись или считывание).

В случае записи в ячейку регистра 9, определяемую кодом младщих разрядов регистра 1, по сигналу, поступающему с соответ-. ствующего выхода дешифратора 1 Г, осуществляется запись поступающей информации, одновременно по адресу, находящемуся в старших разрядах регистра 1, производится считывание из ячеек накопителей 5 информации, заносимой в регистр 9, кроме ячейки, в которую производится запись входной информации. После этого содержимое старших разрядов регистра 1 заносится в регистр 2, а блок 8 вырабатывает сигнал готовности устройства. Одновременно триггер 16 устанавливается в единицу, блокируя работу блока 8 до поступления следующего сигнала обращения.

В случае, когда при первом обращении к устройству производится считывания хранимой информации, осуществляется считывание из накопителей 5, занесение считанной информации в регистр 9 и выдача, в соответствии с кодом младщих разрядов регистра 1, через коммутатор 10 информации, находящейся в соответствующей ячейке рег истра 9. Содержимое старших разрядов регистра 1 заносится в регистр 2. Блок 8 вырабатывает сигнал готовности устройства, а триггер 16 устанавливается в единицу, блокируя работу блока 8 до следующего обращения. .

При последующих обращениях к устройству происходит сравнение адреса, находящегося в регистре 2, со старщими разрядами регистра 1. В случае их совпадения

обращения к накопителям 5 не происходит, В режиме считывания коммутатор 10 выдает на выход устройства информацию из той ячейки регистра 9, номер которой определяется кодом младших разрядов регистра 1, и блок 8 вырабатывает сигнал готовности устройства. В режиме записи поступающая информация заносится в требуемую 5 чейку регистра 9 в соответствии с сигналом, .вырабатываемым дешифратором 11 на основании кода младших разрядов регистра 1, и блок 8 вырабатывает сигнал готовности.

В случае несовпадения адресов, находящихся в регистре 2, и в старших разрядах регистра 1, предварительно осуществ,ляется независимо от заданного режима запись в накопители 5 информации, хранимой в регистре 9 по адресу, хранимому в регистре 2. Затем производится считывание из накопителей 5 информации, хранимой по адресу, определяемому старщими разрядами регистра 1. Если выполняется режим считывания, информация из соответствующей ячейки регистра 9 передается через коммутатор 10

на выход устройства, код старщих разрядов регистра 1 заносится в регистр 2, а блок 8 вырабатывает сигнал готовности. В режиме записи производится запись поступающей информации в требуемую ячейку регистра 9, а в остальные ячейки заносится информация, считываемая из накопителей 5. Код старших разрядов регистра 1 заносится в регистр 2 и блок 8. вырабатывает сигнал готовности.

Поскольку команды, входящие в состав программ, и хранимые в накопителе 13, заносятся в него последовательно, предлагаемое устройство позволяет уменьшить число обращений к накопителям 5 в КТ раз (где Т - число накопителей 5, входящих в состав устройства, К - коэффициент разветвления программ) и таким образом, повысить быстродействие оперативного запоминающего устройства.

Технико-экономическое преимущество

предлагаемого устройства заключае1ся в более высоком быстродействии по сравнению с , прототипом.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающее устройство | 1973 |

|

SU517934A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Майоров С | |||

| А., Новиков Г | |||

| И | |||

| Принципы организации цифровых машин | |||

| Л., «Машиностроение, 1974, с | |||

| Велосипед, приводимый в движение силой тяжести едущего | 1922 |

|

SU380A1 |

Авторы

Даты

1984-05-30—Публикация

1983-03-22—Подача