to

СО

ю

о

Изобретение относится к вычисли- телыгой технике и может быть использовано при построении универсальных узлов цифровых вычислительных машин.

Целью изобретения является повышение достоверности функционирования блока путем введения в его логическую структуру средств функционального контроля и восстановления рабо- тоспособности.

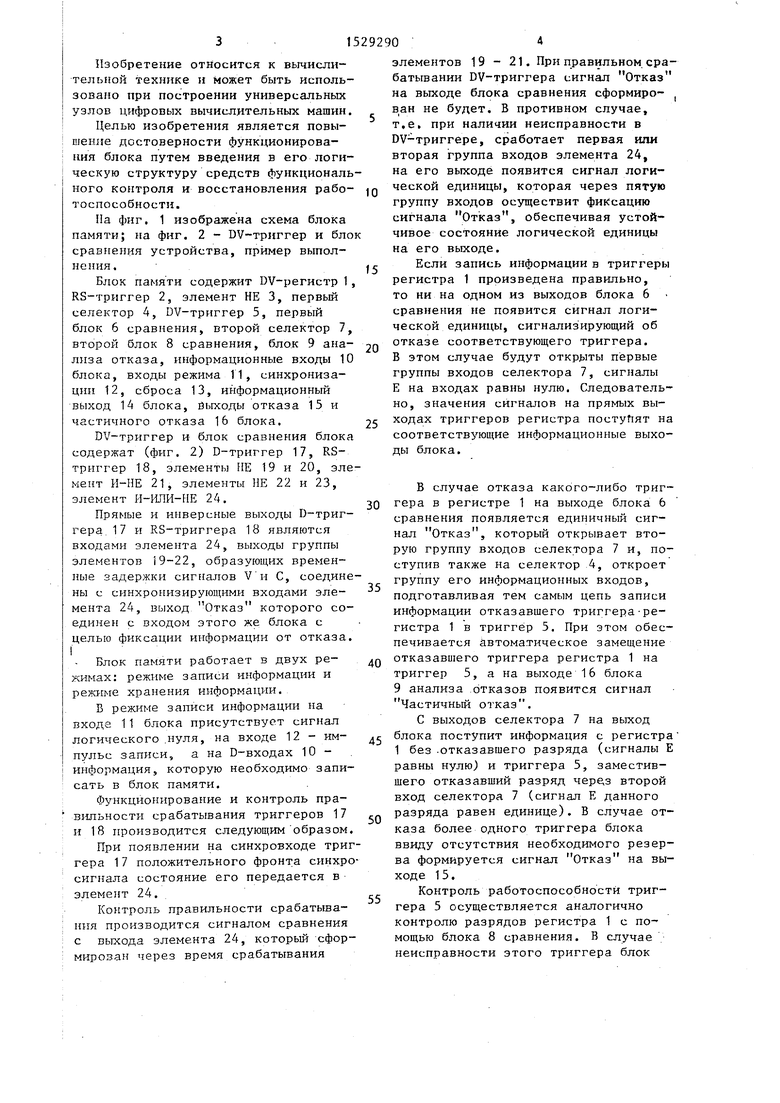

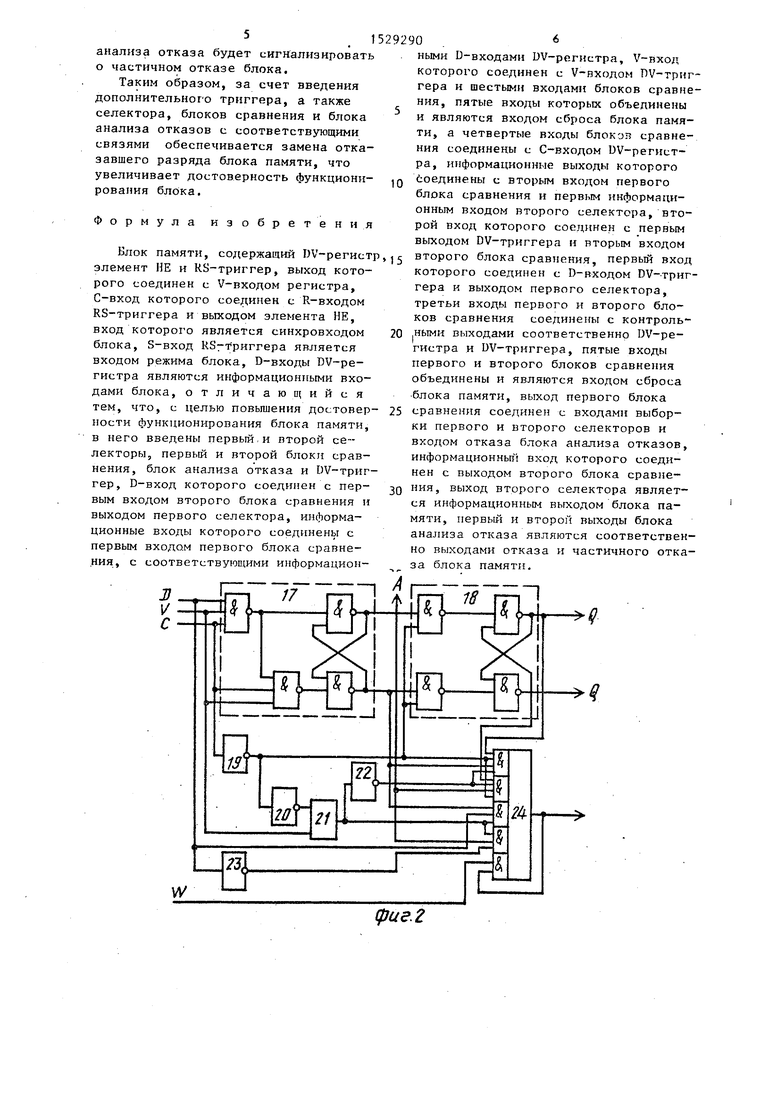

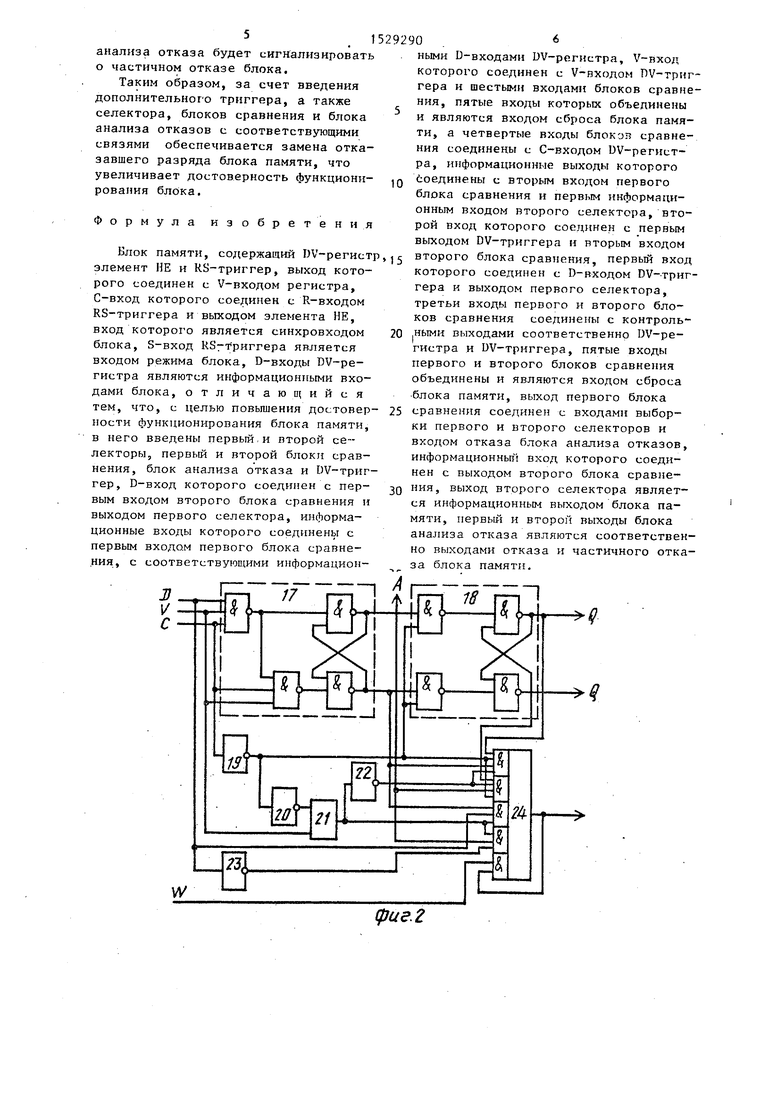

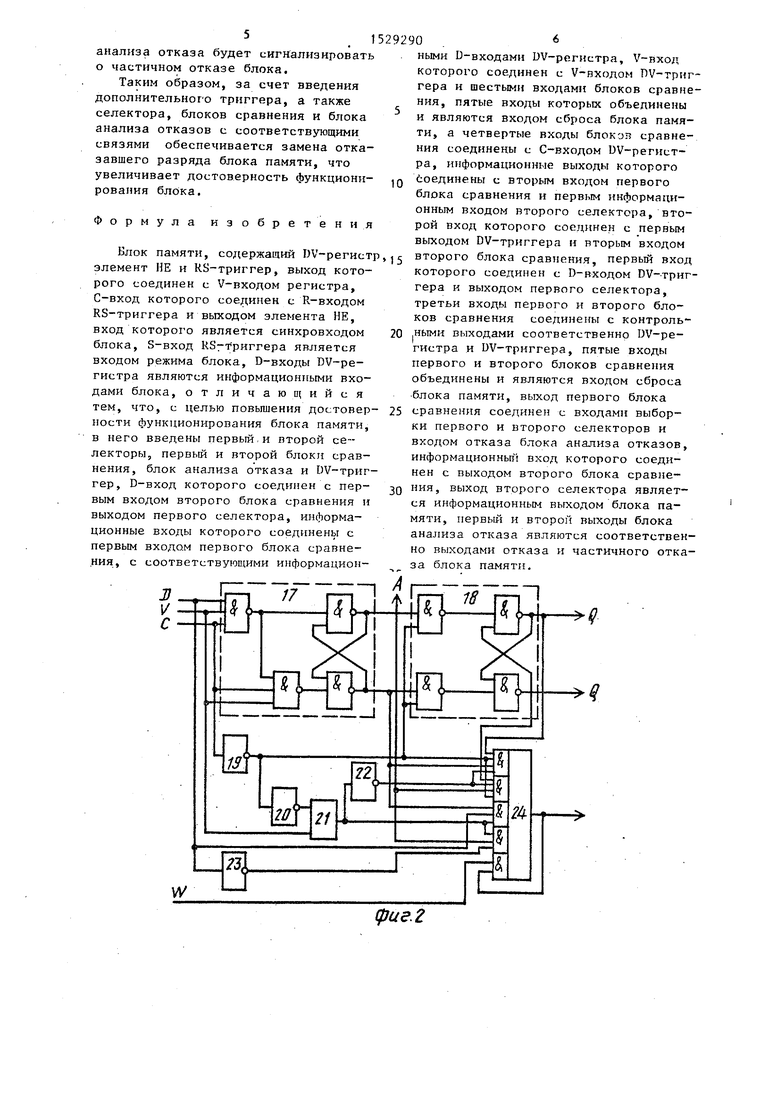

Па фиг, 1 изображена схема блока памяти; на фиг. 2 - DV-триггер и бло сравнения устройства, пример выполнения.

Блок памяти содержит DV-регистр 1 , RS-триггер 2, элемент НЕ 3, первый селектор 4, DV-триггер 5, первый блок 6 сравнения, второй селектор 7, второй блок 8 сравнения, блок 9 анализа отказа, информационные входы 10 блока, входы режима 11, синхронизации 12, сброса 13, информационный выход 14 блока. Выходы отказа 15 и частичного отказа 16 блока.

DV-триггер и блок сравнения блока содержат (фиг. 2) D-триггер 17, RS- триггер 18, элементы НЕ 19 и 20, элемент И-ИЕ 21, элементы НЕ 22 и 23, элемент И-ИЛИ-НЕ 24.

Прямые и инверсные выходы D-триг- гера.17 и RS-триггера 18 являются входами элемента 24, выходы группы элементов , образующих временные задержки сигналов Ун С, соединены с синхронизирующими входами элемента 24, выход Отказ которого соединен с входом этого же блока с целью фиксации информации от отказа.

Блок памяти работает в двух ре- кимах: режиме записи информации и режиме хранения информации.

В режиме записи информации на входе 11 блока присутствует сигнал логического .нуля, на входе 12 - импульс записи, а на D-входах 10 - информация, которую необходимо записать в блок памяти.

Функционирование и контроль пра- BifflbHocTH срабатывания триггеров 17 и 18 производится следующим образом.

При появлении на синхровходе триггера 17 положительного фронта синхросигнала состояние его передается в элемент 24. .

Контроль правильности срабатывания производится сигналом сравнения с выхода элемента 24, который сформирован через время срабатывания

Q

92904

элементов 19 - 21. При правильном срабатывании DV-триггера сигнал Отказ на выходе блока сравнения сформиро- не будет. В противном случае, т.е. при наличии неисправности в DV-триггере, сработает первая или вторая группа входов элемента 24, на его выходе появится сигнал логической единицы, которая через пятую группу входов осуществит фиксацию

5

0

5

0

5

0

5

0

5

сигнала Отказ , обеспечивая устойчивое состояние логической единицы на его выходе.

Если запись информации в триггеры регистра 1 произведена правильно, то ни на одном из выходов блока 6 сравнения не появится сигнал логической единицы, сигнализирующий об отказе соответствующего триггера.

8этом случае будут открыты первые группы входов селектора 7, сигналы

Е на входах равны нулю. Следовательно, значения сигналов на прямых выходах триггеров регистра поступят на соответствующие информационные выходы блока.

В случае отказа какого-либо триггера в регистре 1 на выходе блока 6 сравнения появляется единичный сигнал Отказ, который открывает вторую группу входов селектора 7 и, поступив также на селектор 4, откроет группу его информационных входов, подготавливая тем самым цепь записи информации отказавшего триггера-регистра 1 в триггер 5. При этом обеспечивается автоматическое замещение отказавшего триггера регистра 1 на триггер 5, а на выходе 16 блока

9анализа отказов появится сигнал Частичный отказ.

С выходов селектора 7 на выход блока поступит информация с регистра 1 без .отказавшего разряда (сигналы Е равны нулю) и триггера 5, заместив- щего отказавший разряд второй вход селектора 7 (сигнал Е данного разряда равен единице). В случае отказа более одного триггера блока ввиду отсутствия необходимого резерва формируется сигнал Отказ на выходе 15,

Контроль работоспособности триггера 5 осуществляется аналогично контролю разрядов регистра 1 с помощью блока 8 сравнения. В случае неисправности этого триггера блок

анализа отказа будет сигнализировать о частичном отказе блока.

Таким образом, за счет введения дополнительного триггера, а также селектора, блоков сравнения и блока анализа отказов с соответствующими связями обеспечивается замена отказавшего разряда блока памяти, что увеличивает достоверность функционирования блока.

Формула изобретения

ными D-входами DV-регистра, V-вход которого соединен с V-нходом ПУ-триг- гера и шестыми входами блоков сравнения, пятые входы которых объединены и являются входом сброса блока памяти, а четвертые входы блокэг сравнения соединены с С-входом DV-регистра, информационные выходы которого соединены с вторым входом первого блока сравнения и первым информационным входом второго селектора, второй вход которого соединен с первым

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения экстремума | 1988 |

|

SU1603341A1 |

| Устройство для контроля дублированной системы | 1985 |

|

SU1293861A1 |

| Устройство для контроля параллельной вычислительной системы | 1987 |

|

SU1451697A1 |

| Устройство для контроля интегральных схем | 1986 |

|

SU1377785A1 |

| Система коммутации | 1986 |

|

SU1359783A1 |

| Устройство для контроля плоских однородных поверхностей | 1988 |

|

SU1619311A1 |

| DV-триггер | 1987 |

|

SU1465936A1 |

| Многоканальный резервированный радиоцентр | 1983 |

|

SU1228322A1 |

| УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ | 2001 |

|

RU2207616C2 |

| Двоичный счетчик | 1989 |

|

SU1598170A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении универсальных узлов цифровых вычислительных машин. Целью изобретения является повышение достоверности функционирования блока памяти. Поставленная цель достигается за счет введения селекторов 4, 7, блоков сравнения 6,8, блока 9 анализа отказа, DV-триггера 5, что обеспечивает замену отказавшего разряда блока памяти и выработку сигнала об отказе. 2 ил.

выходом DV-триггера и вторым входом Блок памяти, содержащий DV-регистр,,5 второго блока сравнения, первый вход

элемент НЕ и RS-триггер, выход которого соединен с V-входом регистра, С-вход которого соединен с R-входом RS-триггера и выходом элемента НЕ, вход которого является синхровходом блока, S-вход КЗгт риггера является входом режима блока, D-входы DV-регистра являются информационными входами блока, отличаюп(ийся

которого соединен с D-входом DV-тpиг- гера и выходом первого селектора, третьи входы первого и второго блоков сравнения соединены с контроль- 20 |НЫми выходами соответственно DV-регистра и DV-триггера, пятые входы первого и второго блоков сравнения объединены и являются входом сброса блока памяти, выход первого блока

тем, что, с целью повышения достовер- 25 сравнения соединен с входами выборности функционирования блока памяти, ки первого и второго селекторов и в него введены первьй.и второй се- входом отказа блока анализа отказов,

информационный вход которого соединен с выходом второго блока сравнелекторы, первый и второй блоки сравнения, блок анализа отказа и DV-триг- гер, D-вход которого соединен с первым входом второго блока сравнения и выходом первого селектора, информационные входы которого соединены с первым входам первого блока сравнения, с соответствующими информацион3Q ния, выход второго селектора является информационнь м выходом блока памяти, первый и второй выходы блока анализа отказа являются соответственно выходами отказа и частичного отказа блока памяти.

которого соединен с D-входом DV-тpиг- гера и выходом первого селектора, третьи входы первого и второго блоков сравнения соединены с контроль- 20 |НЫми выходами соответственно DV-регистра и DV-триггера, пятые входы первого и второго блоков сравнения объединены и являются входом сброса блока памяти, выход первого блока

3Q ния, выход второго селектора является информационнь м выходом блока памяти, первый и второй выходы блока анализа отказа являются соответственно выходами отказа и частичного отказа блока памяти.

| Регистр | 1981 |

|

SU1024989A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Файзуллаев Б.Н | |||

| и др | |||

| Применение интегральных микросхем в электронной вычислительной технике: Справочник | |||

| М | |||

| : Радио и связь, 1987, с | |||

| Способ изготовления звездочек для французской бороны-катка | 1922 |

|

SU46A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление с иглой для прочистки кухонь типа "Примус" | 1923 |

|

SU40A1 |

Авторы

Даты

1989-12-15—Публикация

1987-07-06—Подача