|В-случае нарушения условий функцио- |нирования, представленньпс в вьфаже- |НИИ (3),, на выходе селектора-тригге |ра 14 также вьфабатывается сигнал | 0тказ DV-триггера.

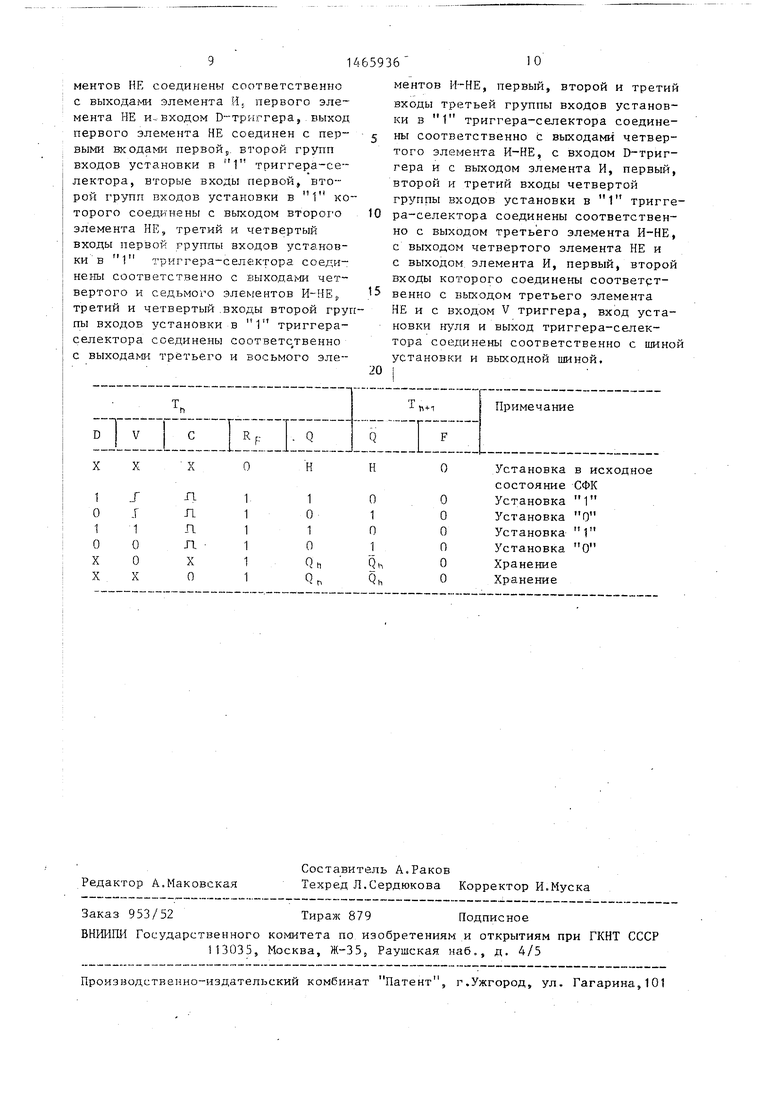

Рассмотрим последовательность ср батыватя всех элементов логической |Структуры предлагаемого DV-триггера iB его трех основных режимах функцио- :нирования: хранение, установка 1, |установка П.

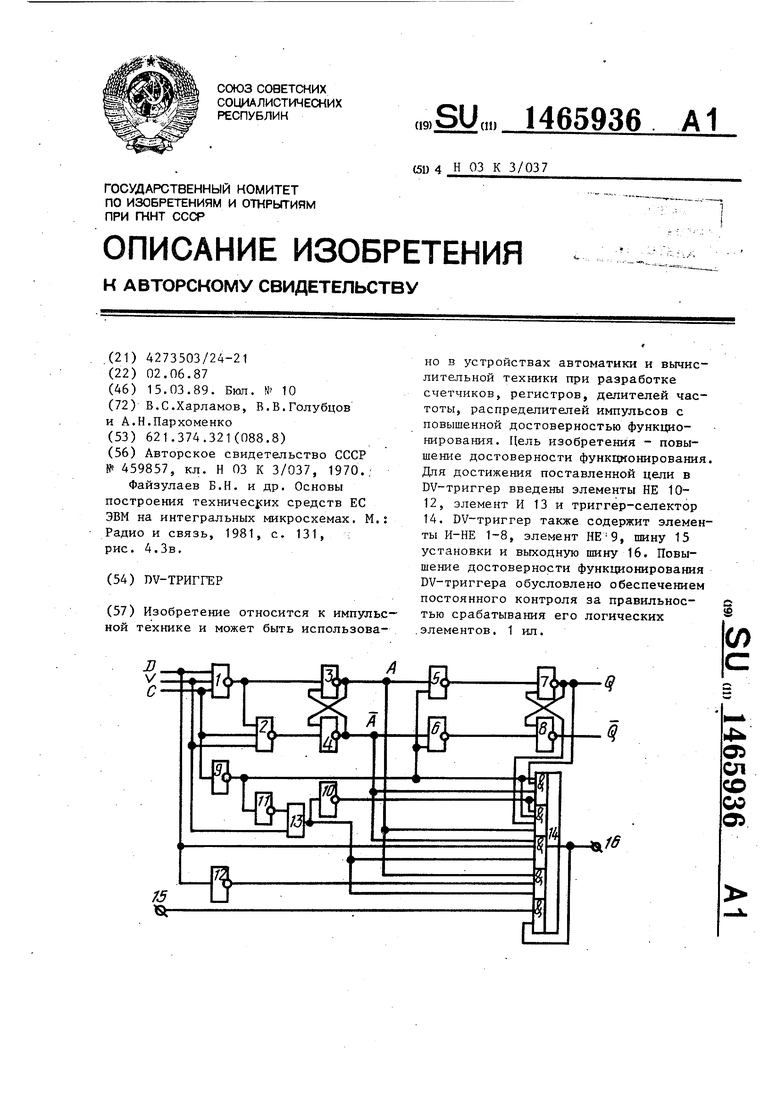

В режиме Установка 1 (таблица, |п. 4) по D-входу с поступлением поло |жительного фронта синхросигнала на jC-вход триггера на выходе первого Ьлемента И-НЕ 1 через вре1.1Я сра- батывашит элемента И-НЕ 1 установит- |ся сигнал логического нуля. Следова- :тельно5 через время 21 срабаты- вания с момента поступления положительного фронта сигнала на С-вход на вьгкодах второго и третьего элементов И-НЕ 2 и 3 установятся сигналы логической единицы; через время ЗТрр срабатывания на выходе четвертого элемента И-НЕ 4 - сигнал логического нуля. Таким образом, через время ЗТ(,р в точке А (см, чертеж) будет установлено состояш-ie логической единицы, а в точке А - состоя- те логического нуля. Контроль правильности срабатывания элементов первой ступени DV-триггера осуществляется стробом сравнения с выхода элемента И 13, который появляется также через время ЗТср срабатывания элементов НЕ 9, 11 и самого элемента И 13, Если в ходе контроля будет

ние логического нуля, а шестой элемент И-НЕ 6 останется в состоя1 ии логической единицы на своем выходе. Следовательно, через время срабатывания с момента поступле шя отрицательного фронта синхроимпульса на выходе седьмого элемента И-НЕ 7 установится сигнал логической едини- цы а через время 4Тср на выходе элемента И-НЕ 8 - сигнал логического нуля. Контроль правильности срабатывания логических элементов второй ступени производится стробом сравнения, который появляется на выходе

2 элемента НЕ 10 через время 4Т(.р сра- батыва1-гия с момента появления отрицательного фронта на синхровходе DV-триггера. При выполнении условий (3) на выходе селектора-триггера

0 14 сигнал .Отказ не сформируется. В противном случае, т.е. при вьтол- нении условий (5), на его выходе будет сформирован сигнал Отказ одного или нескольких логических элемен5 тон второй ступени DV-триггера.

В режиме Установка О (таблица, п. 5) по D-входу с приходом положительного фронта синхросигнала на выходе элемента И-НЕ 1 установится

сигнал логической единицы, а на выходе элемента И-НЕ 2 - сигнал логического нуля, который через время 2Т(;р, срабатывания с момента появления положительного фронта синхроим5 пульса приведет к формированию на выходе элемента И-НЕ 4 сигнала логической €1ДИ1Шцы. Через время на выходе элемента И-НЕ 3 будет мирован сигнал логического нуля.

10

1465936

Контроль правильности срабатывания логических элементов первой ступени будет проведен на входах третьей и , четвертой групп входов селектора- триггера 14 сигналом сравнения с выхода элемента И 13, который будет сформирован через время ЗТср срабатывания элементов НЕ 9 и 11, а также самого элемента И 13. При вьтолнении условий (2) сигнал Отказ на выходе селектора-триггера 14 не появится; в противном случае он будет сформирован, сигнализируя об отказе одного или нескольких логических элементов первой ступени DV-триггера. ,

Функционирование и контроль правильности срабатывания логических элементов второй ступени производится следующим образом.

При появлении на синхровходе DV- триггера отрицательного фронта синхросигнала состояние основного триггера (первой ступени) будет передано во вторую ступень по следующей логи-25 ческой ветви: через 2Ttp на выходе элемента И-НЕ 6 будет сформирован сигнал логического нуля; через время

15

20

В этом случае контроль правильности хранения предыдущего состояния производится следующим образом.

Через время Тер срабатывания эле- .мента НЕ 9 производится сравнение состояний в точке А с состоянием на прямом выходе DV-триггера и в точке А - с состоянием сигнала на инверсном выходе DV-триггера. Такое же сравнение производится через время 4Тср с момента появления сигнала логического нуля на синхровходе D- триггера стробом сравнения с выхода элемента НЕ 10.

Функционирова1ше и контроль правильности срабатывания логических элементов структуры DV-триг ера в остальных режимах его работы (таблица, пп. 2, 3 и 7) осуществляются аналогичным образом.

о р м у л а

зобретения

DV-триггер, содержащий первый элемент НЕ и восемь элементов И-НЕ, входы D, V и С триггера соединены с входами первого элемента И-НЕ, выход которого соединен с первым вхоответственно с входами V и С триггера, выходы первого и второго элементов И-НЕ соединены соответственно с

динены соответственно с вторыми входами четвертого и третьего элементов И-НЕ и соединены соответственно

ЗТср на выходе элемента И-НЕ 8 - сигнал логической единицы и через время 30 дом второго элемента И-НЕ, второй и 4Т,, на выходе элемента И-НЕ 7 - сиг- третий входы которого соеди 1ны совал логического нуля. Контроль пра-i-оединены со вильности срабатывания будет произведен сигналом сравнения с выхода

чпрмрн-га нв- in V-- сл. .- ,. „ «-исдинены соответственно с

элемента НЕ 10, которьш будет сформи-з5 первыми входами третьего и четвертого рован также через время 41, сраба-элементов И-НЕ, выходы которьГсо тывания элементов НЕ 9, 11, И 13 икоторых сое

самого элемента НЕ 10. При выполнении условий (3) сигнал Отказ на

вьпсоде селектора-триггера 14 оформи- 40 с первыми входами пятого и шестого рован не будет. В противном случае,элементов И-НЕ, вьпсоды которы соединены соответственно, с первыми входами седьмого и восьмого элементов И-НЕ, выходы которых соединены со- 45 ответственно с вторыми входами восьмого и седьмого элементов И-НЕ, вход С триггера соединен с входом первого элемента НЕ, выход которого соединен с вторыми входами пятого и 50 шестого элементов И-НЕ, отличающийся тем, что, с целью повышения достоверности функционирования, в него введены второй, третий, четвертый элементы НЕ, элемент 55 И и триггер-селектор, имеющий вход установки нуля, и четыре группы вхот.е. при выполнении условий (5), сигнал Отказ формируется на выходе селектора-триггера 14, сигнализируя об -отказе одного или нескольких логических элементов второй ступени DV-триггера.

В режиме хранения (таблица, п.7), т.е. при наличии нулевого потенциала на синхровходе DV-триггера, с выходов элементов И-НЕ 1 и 2 на входы элементов И-НЕ 3 и 4 поступают сигналы логической единицы, подтверждая предьщущее состояние триггера первой ступени. С выходов элементов И-НЕ 5 и 6 на входы элементов И-НЕ 7 и 8 также поступают сигналы логической единицы, подтверждая предыдущее состояние триггера второй ступени.

дов установки в 1, в каждой из которых входы объединены по И, входы второго, третьего и четвертого эле10

5

5

0

В этом случае контроль правильности хранения предыдущего состояния производится следующим образом.

Через время Тер срабатывания эле- .мента НЕ 9 производится сравнение состояний в точке А с состоянием на прямом выходе DV-триггера и в точке А - с состоянием сигнала на инверсном выходе DV-триггера. Такое же сравнение производится через время 4Тср с момента появления сигнала логического нуля на синхровходе D- триггера стробом сравнения с выхода элемента НЕ 10.

Функционирова1ше и контроль правильности срабатывания логических элементов структуры DV-триг ера в остальных режимах его работы (таблица, пп. 2, 3 и 7) осуществляются аналогичным образом.

о р м у л а

зобретения

DV-триггер, содержащий первый элемент НЕ и восемь элементов И-НЕ, входы D, V и С триггера соединены с входами первого элемента И-НЕ, выход которого соединен с первым входом второго элемента И-НЕ, второй и третий входы которого соеди 1ны соi-оединены со

ответственно с входами V и С триггера, выходы первого и второго элементов И-НЕ соединены соответственно с

дом второго элемента И-НЕ, второй и третий входы которого соеди 1ны соi-оединены со

.- ,. „ «-исдинены соответственно с

первыми входами третьего и четвертого элементов И-НЕ, выходы которьГсо динены соответственно с вторыми входами четвертого и третьего элементов И-НЕ и соединены соответственно

первыми входами третьего и четвертого элементов И-НЕ, выходы которьГсо которых сое

с первыми входами пятого и шестого элементов И-НЕ, вьпсоды которы соединены соответственно, с первыми входами седьмого и восьмого элементов И-НЕ, выходы которых соединены со- ответственно с вторыми входами восьмого и седьмого элементов И-НЕ, вход С триггера соединен с входом первого элемента НЕ, выход которого соединен с вторыми входами пятого и шестого элементов И-НЕ, отличающийся тем, что, с целью повышения достоверности функционирования, в него введены второй, третий, четвертый элементы НЕ, элемент И и триггер-селектор, имеющий вход установки нуля, и четыре группы входов установки в 1, в каждой из которых входы объединены по И, входы второго, третьего и четвертого элементов НЕ соединены соответственно с выходами элемента И. первого элемента НЕ И-входом О-триггера,.выход первого элемента НЕ соединен с первыми входами первойS,, второй групп входов установки в 1 триггера-селектора, вторые входы первой, второй групп входов установки в 1 которого соединены с выходом второго элемента НЕ, третий и четвертый входы первой группы входов установки в 1 триггера-селектора соединены соответственно с выходами четвертого и седьмого элементов И-НЕ третий и четвертый .входы второй группы входов установки в Г триггера- селектора соединены соответственно с выходами третьего и восьмого эле

ментов И-НЕ, первый, второй и третий входы третьей группы входов установки в 1 триггера-селектора соединены соответственно с выходами четвертого элемента И-НЕ, с входом D-триг- гера и с выходом элемента И, первый, второй и третий входы четвертой группы Езходов установки в 1 триггера-селектора соединены соответственно с выходом треть его элемента И-НЕ, с выходом четвертого элемента НЕ и с выходом элемента И, первый, второй входы которого соединены соответрт- венно с выходом третьего элемента НЕ и с входом V триггера, вход установки нуля и выход триггера-селектора соединены соответственно с шиной установки и выходной шиной.

| название | год | авторы | номер документа |

|---|---|---|---|

| DV-триггер | 1988 |

|

SU1564714A1 |

| ДV-триггер | 1989 |

|

SU1629963A1 |

| Двоичный счетчик | 1988 |

|

SU1684927A1 |

| Двоично-десятичный счетчик | 1989 |

|

SU1676098A1 |

| Управляемый делитель частоты следования импульсов | 1990 |

|

SU1757097A1 |

| Двоичный счетчик | 1989 |

|

SU1644374A1 |

| Блок памяти | 1987 |

|

SU1529290A1 |

| Двоично-десятичный счетчик | 1989 |

|

SU1693724A1 |

| Двоичный счетчик | 1988 |

|

SU1555857A1 |

| Двоичный счетчик | 1989 |

|

SU1598170A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники при разработке счетчиков, регистров, делителей частоты, распределителей импульсов с повышенной достоверностью функционирования. Цель изобретения - повышение достоверности функционирования. Для достижения поставленной цели в DV-триггер введены элементы НЕ 10- 12, элемент И 13 и триггер-селектор 14. DV-триггер также содержит элементы И-НЕ 1-8, элемент НЕ 9, шину 15 установки и выходную шину 16. Повышение достоверности функционирования DV-триггера обусловлено обеспечением постоянного контроля за правильностью срабатывания его логических .элементов. 1 ил. (Л

| Триггер =типа | 1970 |

|

SU459857A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| и др | |||

| Основы построения техничес сих средств ЕС ЭВМ на интегральных микросхемах | |||

| М.: Радио и связь, 1981, с | |||

| Способ получения продукта конденсации бетанафтола с формальдегидом | 1923 |

|

SU131A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-03-15—Публикация

1987-06-02—Подача