Изобретение относится к импульсной технике и может быть использовано в вычислительных устройствах и системах автоматики.

Целью изобретения является повышение достоверности функционирования путем включения в структуру устройства средств функционального контроля и автоматизации процесса восстановления работоспособности.

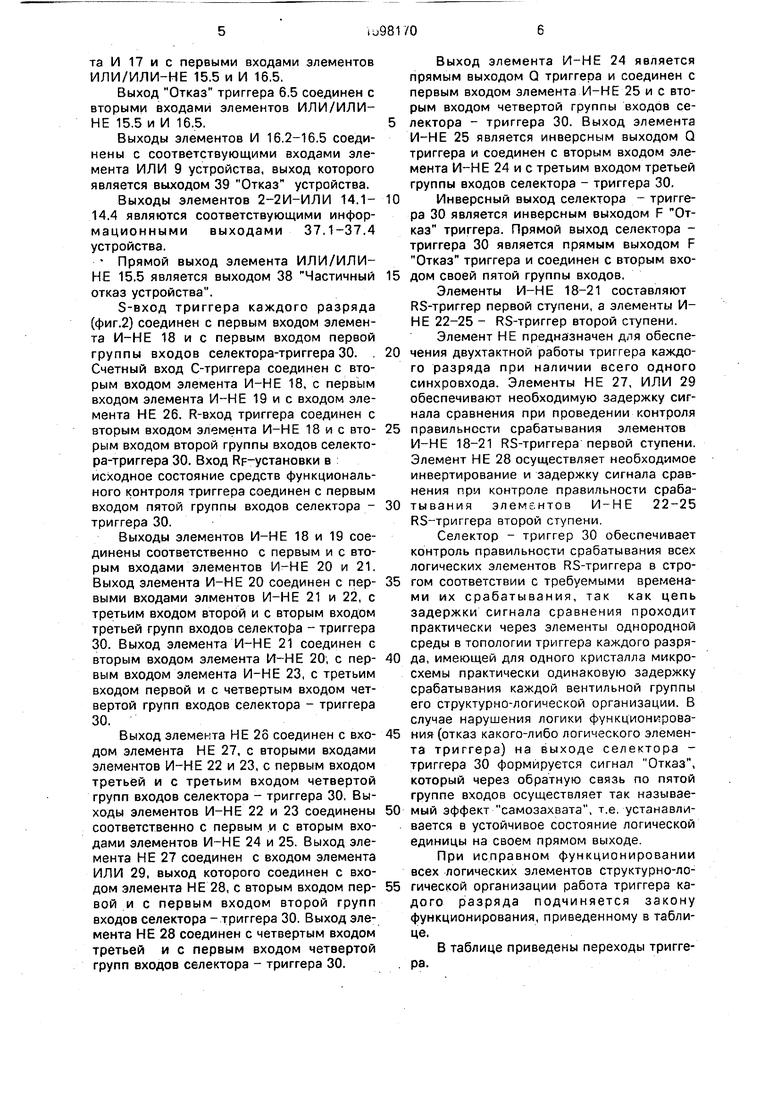

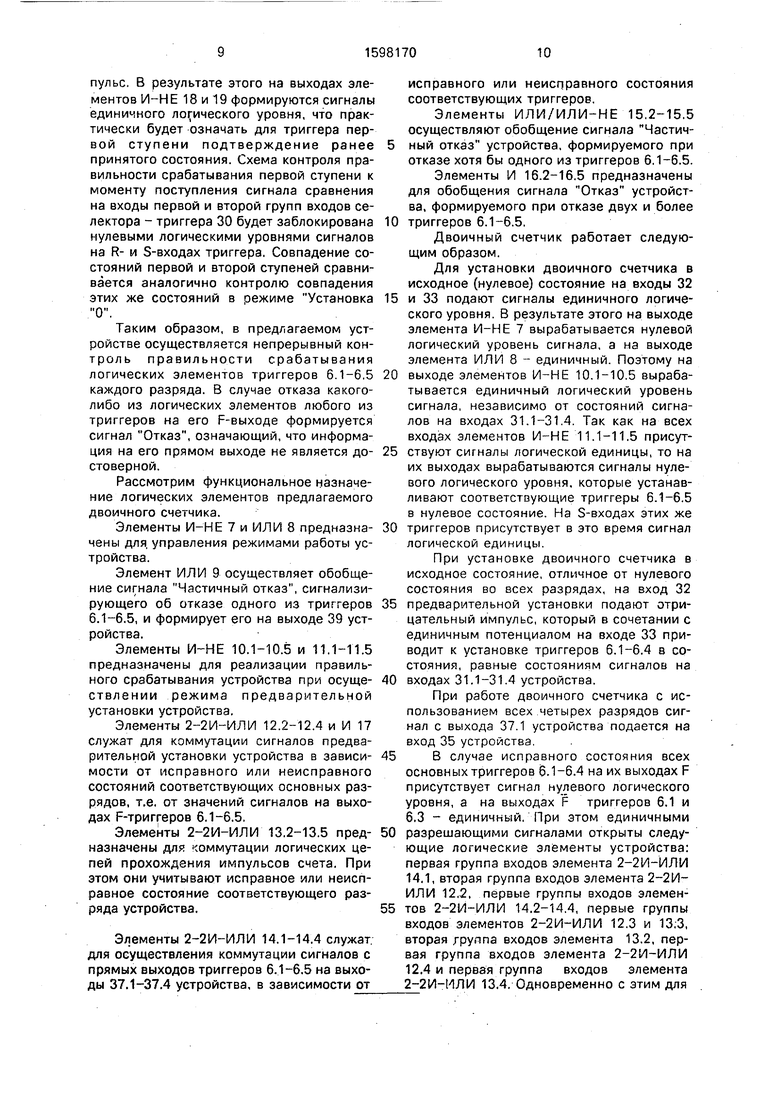

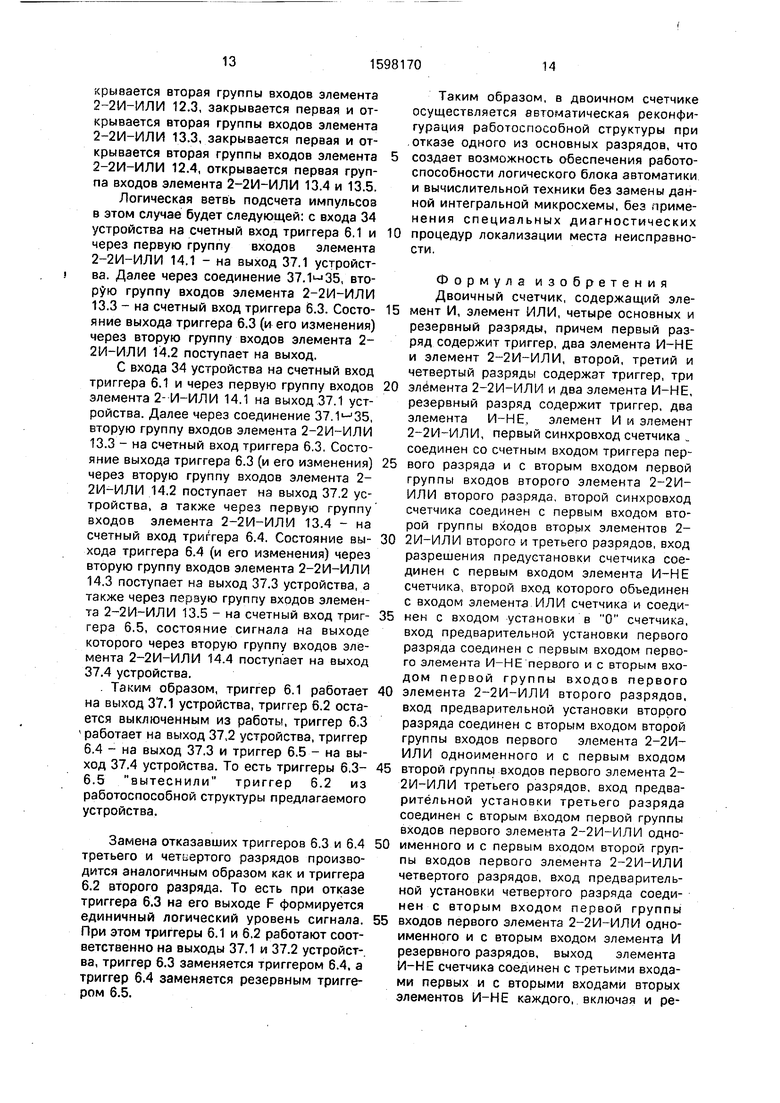

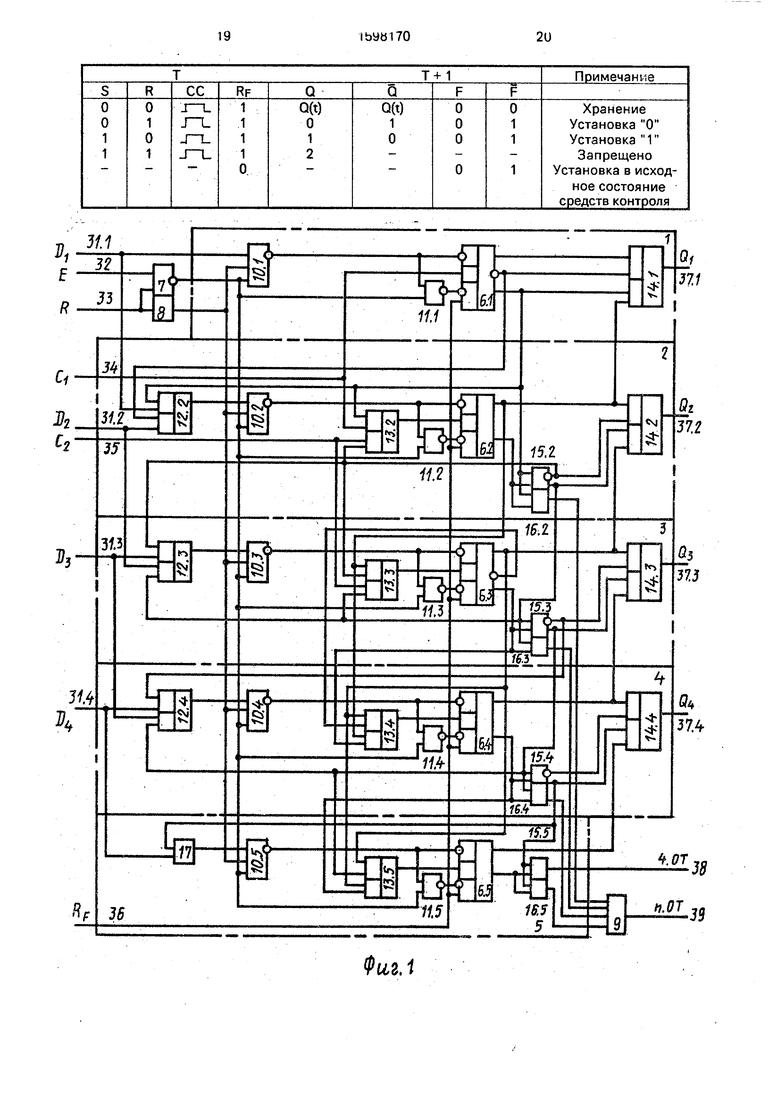

Нафиг.1 представлена функциональ-. ная схема предлагаемого двоичного счетчика; на фиг.2 - схема лриггера каждого разряда.

Устройство содержит (фиг.1) основные разряды 1-4, резервный разряд 5, триггеры 6.1-6.5 разрядов, элемент И-НЕ 7 устройства, первый 8 и второй 9 элементы

ИЛИ устройства, первые 10.1-10.5 и вторые 11П-11.5 элементы И-НЕ разрядов, первые 12.2-12.4, вторые 13.2-13.5 и третьи 14.1-14.4 элементы 2-2И-ИЛИ разрядов, элементы ИЛИ/ИЛИ-НЕ 15.2-15.5 разрядов, элементы И 16.2-16.5 разрядов и элемент И 17 резервного разряда.

Триггер каждого разряда (фиг.2) содержит элементы И-НЕ 18-25, элементы НЕ 26-28, элемент ИЛИ 29 и селектор - триггер 30.

Вход 31.1 предварительной установки первого разряда соединен с первым входом элемента И-НЕ 10.1 и с вторым входом первой группы входов элемента 2-2И-ИЛИ 12.2. Вход 31.2 предварительной установки второго разряда соединен с вторым входом второй группы входов

ю сх

N4 О

мента 2-2И-ЙЛ / 12.2 ы с первым входом второй группы входов элемента 2-2И-ИЛИ 12.3. Вход 31.3 предварительной установки третьего разряда соединен с вторым входом первой группы входов элемента 2-2И-ИЛИ 12.3 и с первым входом второй группы входов элемента 2-2И-ИЛИ 12.4. Вход 31.4 предварительной установки четвертого разряда соединен с вторым входом первой группы входов элемента 2-2И-ИЛИ 12.4 и с вторым входом элемента И 17.

Вход 32 разрешения предварительной установки устройства соединен с первым входом элемента И-НЕ 7 устройства. Вход 33 установки в О устройства соединен с вторым входом элемента И-НЕ 7 и с входом элемента ИЛИ 8 устройства. Первый синхровход 34 устройства соединен со счетным входом триггера 6.1 и с вторым входом первой rpynnbf входов элемента 2-2И-ИЛИ 13.2. Второй 35 синхровход устройства соединен с первым входом второй труппы входов элемента 2-2И-ИЛИ 13.2 и с первым входом второй группы вхо- дов элемента 2-2И-ИЛИ 13.3. Вход 36 установки в исходное состояние средств функционального контроля устройства соединен с Рр-входами триггеров 6.1-6.5 разрядов.

Выход элемента И-НЕ 7 устройства соединен с третьими входами элементов И-НЕ 10.1-10.5 и с вторыми входами элементов И-НЕ 11.1-11.5. Выход элемента ИЛИ 8 устройства соединен с вторыми входами элементов И-НЕ 10.1-10.5,

Выходы элементов 2-2И-ИЛИ 12.2- 12.5 и элемента И 17 соединены соответственно с первыми входами соответствующих им элементов И-НЕ 10.2-10.5.

Выходы элементов И-НЕ 10,1-10.5 соединены с S-входами триггеров 6.1-6.5 и с первыми входами элементов И-НЕ 11.1- 11.5 одноименных разрядов.

Выходы элементов И-НЕ 11.1-11.5 со- 4 единены с R-входами триггеров 6.1-6.5 одноименных разрядов.

Выходы элементов 2-2И-ИЛИ 13.2- 13.5 соединены со счетными входами триггеров 6.1-6.5 одноименных разрядов.5

Прямой выход триггера 6.1 соединен с первым входом первой группы входов элемента 2-2И-ИЛИ 14.1. Прямые выходы триггеров 6.2-6.4 соединены с первыми входами первых групп входов .элементов 2-2И-ИЛИ 14.2-14.4 одноименных и с вторыми входами вторых групп входов элементов 2-2И-ИЛИ 14.1-14.3 предшествующих разрядов. ПРИМОЙ выход триггера 6.5

соединен с вторым входом второй группы входов элемента 2-2И-ИЛИ 14.4.

Инверсный выход Отказ триггера 6 1 соединен с вторым входом первой группы входов элемента 2-2И-ИЛИ 14.1 и с первым входом второй группы входов элемента 2-2И-ИЛИ 12.2. Прямой выход Отказ- триггера 6.1 соединен с первым входом второй группы входов элемента 2-2И-ИЛИ 14.1, с первыми входами первых групп входов элементов 2-2И-ИЛИ 12.2 и 13.2 и с первыми входами элементов ИЛИ/ИЛИ- НЕ 15.2 и И 16.2.

Прямой выход Отказ триггера 6.2 соединен с вторыми входами элементов ИЛИ/ИЛИ-НЕ 15.2 и И 16.2. Инверсный выход элемента ИЛИ/ИЛИ-НЕ 15.2 соединен с первым входом первой группы входов элемента 2-2И-ИЛИ 12.3, с вторыми входами первой и второй групп входов соответствующих элементов 2-2И-ИЛИ 13.3 и 13.2 и с вторым входом первой группы входов элемента 2-2И-ИЛИ 14.2. Прямой выход элемента ИЛИ/ИЛИ-НЕ 15.2 соединен с первым входом второй группы входов элемента 2-2И-ИЛИ 14 .2, с вторыми входами вторых групп входов элементов 2-2И-ИЛИ 12.3 и 13.3 и с первыми входа- Г Ли элементов ИЛИ/ИЛИ-НЕ 15.3 и И 16.3. Инверсный выход Отказ триггера 6.3 соединен с вторым входом первой группы входов элемента 2-2И-ИЛИ 13.5. Прямой выход Отказ триггера 6.3 соединен с вторыми входами элементов ИЛИ/ИЛИ-НЕ 15.3 и И 16.3 и с вторым входом второй группы входов элемента 2-2И-ИЛИ 13.4. Инверсный выход элемента ИЛИ/ИЛИ-НЕ

15.3соединен с вторым входом первой группы входов элемента 2-2И-ИЛИ 14.3 и с первым входом первой группы входов элемента 2-2И-ИЛИ 12.4. Прямой выход элемента ИЛИ/ИЛИ-НЕ 15.3 соединен с первым входом второй группы входов элемента 2-2И-ИЛИ 14.3, с первыми входами элементов ИЛИ/ИЛИ-НЕ 15.4 и И 16.4, с вторыми входами соответственно второй и первой групп входов элементов 2-2И-ИЛИ

12.4и 13.5.

Прямой выход Отказ триггера 6.4 соединен с вторыми входами элементов ИЛИ/ИЛИ-НЕ 15.4 и И 16.4 и с вторым сходом второй группы входов элемента 2-2И-ИЛИ 13.5. Инверсный выход элемента ИЛИ/ИЛИ-НЕ 15.4 соединен с вторым входом первой группы входов элемента 2-2И-ИЛИ 14.4. Прямой выход элемента ИЛИ/ИЛИ-НЕ 15.4 соединен с первым входом второй группы входов элемента 2.-2И-ИЛИ 14,4, с первым входом элемента И 17 и с первыми входами элементов ИЛИ/ИЛИ-НЕ 15.5 и И 16.5.

Выход Отказ триггера 6.5 соединен с вторыми входами элементов ИЛИ/ИЛИ- НЕ 15.5 и И 16.5.

Выходы элементов И 16.2-16.5 соединены с соответствующими входами элемента ИЛИ 9 устройства, выход которого является выходом 39 Отказ устройства.

Выходы элементов 2-2И-ИЛИ 14.1- 14.4 являются соответствующими информационными выходами 37.1-37.4 устройства.

Прямой выход элемента ИЛИ/ИЛИ- НЕ 15.5 является выходом 38 Частичный отказ устройства.

S-вход триггера каждого разряда (фиг.2) соединен с первым входом элемента И-НЕ 18 и с первым входом первой группы входов селектора-триггера 30. . Счетный вход С-триггера соединен с вторым входом элемента И-НЕ 18, с первым входом элемента И-НЕ 19 и с входом элемента НЕ 26. R-вход триггера соединен с вторым входом элемента И-НЕ 18 и с вторым входом второй группы входов селектора-триггера 30. Вход Яр-установки в : исходное состояние средств функционального контроля триггера соединен с первым входом пятой группы входов селектора - триггера 30.

Выходы элементов И-НЕ 18 и 19 соединены соответственно с первым и с вторым входами элементов И-НЕ 20 и 21. Выход элемента И-НЕ 20 соединен с первыми входами элментов И-НЕ 21 и 22, с третьим входом второй и с вторым входом третьей групп входов селектора - триггера 30. Выход элемента И-НЕ 21 соединен с вторым входом элемента И-НЕ 20, с первым входом элемента И-НЕ 23, с третьим входом первой и с четвертым входом четвертой групп входов селектора - триггера 30.

Выход элемента НЕ 26 соединен с входом элемента НЕ 27, с вторыми входами элементов И-НЕ 22 и 23, с первым входом третьей и с третьим входом четвертой групп входов селектора - триггера 30. Выходы элементов И-НЕ 22 и 23 соединены соответственно с первым .и с вторым входами элементов И-НЕ 24 и 25. Выход элемента НЕ 27 соединен с входом элемента ИЛИ 29, выход которого соединен с входом элемента НЕ 28, с вторым входом первой и с первым входом второй групп входов селектора - триггера 30. Выход элемента НЕ 28 соединен с четвертым входом третьей и с первым входом четвертой групп входов селектора - триггера 30.

Выход элемента И-НЕ 24 является прямым выходом О триггера и соединен с первым входом элемента И-НЕ 25 и с вторым входом четвертой группы входов селектора - триггера 30. Выход элемента И-НЕ 25 является инверсным выходом Q триггера и соединен с вторым входом элемента И-НЕ 24 и с третьим входом третьей группы входов селектора - триггера 30.

0 Инверсный выход селектора - триггера 30 является инверсным выходом F Отказ триггера. Прямой выход селектора - триггера 30 является прямым выходом F Отказ триггера и соединен с вторым вхо5 дом своей пятой группы входов.

Элементы И-НЕ 18-21 составляют RS-триггер первой ступени, а элементы И- НЕ 22-25 - RS-триггер второй ступени. Элемент НЕ предназначен для обеспе0 чения двухтактной работы триггера каждого разряда при наличии всего одного синхровхода. Элементы НЕ 27, ИЛИ 29 обеспечивают необходимую задержку сигнала сравнения при проведении контроля

5 правильности срабатывания элементов И-НЕ 18-21 RS-триггера первой ступени. Элемент НЕ 28 осуществляет необходимое инвертирование и задержку сигнала сравнения при контроле правильности сраба0 тывания элементов И-НЕ 22-25 RS-триггера второй ступени.

Селектор - триггер 30 обеспечивает контроль правильности срабатывания всех логических элементов RS-триггера в стро5 гом соответствии с требуемыми временами их срабатывания, так как цепь задержки сигнала сравнения проходит практически через элементы однородной среды в топологии триггера каждого разря0 да, имеющей для одного кристалла микросхемы практически одинаковую задержку срабатывания каждой вентильной группы его структурно-логической организации. В случае нарушения логики функционирова5 ния (отказ какого-либо логического элемента триггера) на выходе селектора - триггера 30 формируется сигнал Отказ, который через обратную связь по пятой группе входов осуществляет так называе0 мый эффект самозахвата, т.е. устанавли- вается в устойчивое состояние логической единицы на своем прямом выходе.

При исправном функционировании всех логических элементов структурно-ло5 гической организации работа триггера ка- дого разряда подчиняется закону функционирования, приведенному в таблице.

В таблице приведены переходы тригге- . ра.

Рассмотрим основные режимы работы триггера каждого разряда.

В режиме установки О на S-входе триггера присутствует сигнал логического О, а на С, R и Рр-входах - сигналы логи- ческой 1. В результате этого на выходах элементов И-НЕ 18 и 19 устанавливаются сигналы логической единицы и логического нуля соответственно. На выходе элемента И-НЕ 21 формируется сигнал логической единицы, что приводит к установке сигнала логического нуля на выходе элемента И-НЕ 20. Таким образом, переходные процессы в RS-триггере первой ступени завершаются после срабатывания трех логических элементов И-НЕ 19-20, В результате на выходах элемента И-НЕ 20 должен быть установлен сигнал логического нуля, а на выходе элемента И-НЕ 21 - сигнал логической единицы. Именно через такое же время срабатывания трёх логических элементов НЕ 26. 27 и ИЛИ 29 на втором входе первой и на первом входе второй групп входов селектора - триггера 30 появляется сигнал разрешения сравне- ния состояний сигналов на S- и R-входах триггера с состояниями на противоположных плечах триггера первой ступени (выход элемента И-НЕ 21 и выход элемента И-НЕ 20). Так как при правильном сраба- тывании логических элементов И-НЕ 18- 21 сигналы н а входах триггера и соответствующих плечах триггера первой ступени дожны быть разнополярными, то первая и вто рая группы входов селектора - триггера остаются закрытыми м на прямом выходе селектора - триггера 30 не формируется сигнал логической единицы. Третья и четвертая группы входов селектора - триггера 30 на время действия высокого уровня синхроимпульса остаются закрыты- ми нулевым потенциалом с выхода элемента НЕ 26. В случае отказа любого из четырех логических элементов И-НЕ 18-21 на выходе селектора - триггера 30 форми- руется сигнал логической единицы, сигнализирующий об отказе триггера первой ступени.

По окончании действия высокого уровня сигнала синхроимпульса высокий уро- вень сигнала с выхода элемента НЕ 26 разрешает перенос состояния RS-триггера первой ступени в RS-триггер второй ступени, который состоит из элементов И-НЕ 22-25, путем открытия элементов И-НЕ 22 и 23. Нулевой потенциал с выхода элемента И-НЕ 23 устанавливает в единичное состояние выход элемента И-НЕ 25 и затем в нулевое состояние сигнал на выходе элемента И-НЕ 24.

Контроль правильности срабатывания элементов И-НЕ 22-25 производится путем сравнения состояний сигналов на выходах триггера первой ступени с состоянием сигналов на противоположных выходах триггера второй ступени. Сигнал разрешения сравнения этих состояний сигналов вырабатывается на выходе элемента НЕ 28 и поступает на четвертый вход третьей и на первый вход четвертой групп входов селектора - триггера 30 через время срабатывания следующих трех логических элементов НЕ 27, ИЛИ 29 и НЕ 28. То есть правильность срабатывания элементов триггера второй ступени контролируется также через время ЗТср срабатывания с момента окончания воздействия синхроимпульса на С-входе триггера.

При правильном срабатывании всех логических элементов триггера второй ступени третья и четвертая группы входов селектора - триггера 30 остаются закрытыми и на его прямом выходе будет присутствовать нулевой логический уровень сигнала, так как первая и вторая группы его входов будут также закрыты нулевым потенциалом с выхода элемента ИЛИ 29. В случае отказа одного из логических элементов И-НЕ 22-25 триггера второй ступени на выходе селектора - триггера 30 будет сформирован единичный логический уровень сигнала, который установит селектор - триггер 30 в устойчивое состояние логической единицы на его прямом выходе через обратную связь по пятой группе входов.

В режиме установки в 1 на S- и RF- входах триггера присутствуют сигналы единичного логического уровня, а на R - входе - сигнал нулевого логического уровня (на С-входе триггера - синхроимпульс). В результате этого в момент действия синхроимпульса производится запись единичного состояния в триггер первой ступени, а триггер второй ступени в этот момент времени будет находиться в режиме хранения предыдущего состояния, так как на,вторые входы элементов И-НЕ. 22 и 23 поступает нулевой потенциал с выхода элемента НЕ 26. По окончании действия синхроимпульса производится установка единичного состояния в триггер второй ступени. Контроль правильности срабатывания логических элементов триггеров первой и второй ступени осуществляется аналогичным образом, что и в режиме Установка О.

В режиме хранения на S- и R-входы триггера подаются сигналы нулевого логического уровня, а на входе С-синхроимпульс, в результате этого на выходах элементов И-НЕ 18 и 19 формируются сигналы единичного ло ического уровня, что практически будет означать для триггера первой ступени подтверждение ранее принятого состояния. Схема контроля правильности срабатывания первой ступени к моменту поступления сигнала сравнения на входы первой и второй групп входов селектора - триггера 30 будет заблокирована нулевыми логическими уровнями сигналов на R- и S-входах триггера. Совпадение состояний первой и второй ступеней сравнивается аналогично контролю совпадения этих же состояний в режиме Установка О.

Таким образом, в предлагаемом устройстве осуществляется непрерывный контроль правильности срабатывания логических элементов триггеров 6.1-6.5 каждого разряда. В случае отказа какого- либо из логических элементов любого из триггеров на его F-выходе формируется сигнал Отказ, означающий, что информация на его прямом выходе не является до- стоверной.

Рассмотрим функциональное назначение логических элементов предлагаемого двоичного счетчика.

Элементы И-НЕ 7 и ИЛИ 8 предназна- чены для, управления режимами работы устройства.

Элемент ИЛИ 9 осуществляет обобщение сигнала Частичный отказ, сигнализирующего об отказе одного из триггеров 6.1-6.5, и формирует его на выходе 39 устройства.

Элементы И-НЕ 10.1-10.5 и 11.1-11.5 предназначены для реализации правильного срабатывания устройства при осуще- ствлении режима предварительной установки устройства.

Элементы 2-2И-ИЛИ 12.2-12.4 и И 17 служат для коммутации сигналов предварительной установки устройства в зависи- мости от исправного или неисправного состояний соответствующих основных разрядов, т.е. от значений сигналов на выходах F-триггеров 6.1-6.5.

Элементы 2-2И-ИЛИ 13.2-13.5 пред- назначены для .оммутации логических цепей прохождения импульсов счета. При этом они учитывают исправное или неисправное состояние соответствующего разряда устройства.

Элементы 2-2И-ИЛИ 14.1-14.4 служат, для осуществления коммутации сигналов с прямых выходов триггеров 6.1-6.5 на выходы 37.1-37.4 устройства, в зависимости от

исправного или неисправного состояния соответствующих триггеров.

Элементы ИЛИ/ИЛИ-НЕ 15.2-15.5 осуществляют обобщение сигнала Частичный отказ устройства, формируемого при отказе хотя бы одного из триггеров 6.1-6.5.

Элементы И 16.2-16.5 предназначены для обобщения сигнала Отказ устройства, формируемого при отказе двух и более триггеров 6.1-6.5.

Двоичный счетчик работает следующим образом.

Для установки двоичного счетчика в исходное (нулевое) состояние на входы 32 и 33 подают сигналы единичного логического уровня. В результате этого на выходе элемента И-НЕ 7 вырабатывается нулевой логический уровень сигнала, а на выходе элемента ИЛИ 8 - единичный. Поэтому на выходе элементов И-НЕ 10.1-10.5 вырабатывается единичный логический уровень сигнала, независимо от состояний сигналов на входах 31.1-31.4. Так как на всех входах элементов И-НЕ 11.1-11.5 присутствуют сигналы логической единицы, то на их выходах вырабатываются сигналы нулевого логического уровня, которые устанавливают соответствующие триггеры 6.1-6.5 в нулевое состояние. На S-входах этих же триггеров присутствует в это время сигнал логической единицы.

При установке двоичного счетчика в исходное состояние, отличное от нулевого состояния во всех разрядах, на вход 32 предварительной установки подают отрицательный импульс, который в сочетании с единичным потенциалом на входе 33 приводит к установке триггеров 6.1-6.4 в состояния, равные состояниям сигналов на входах 31.1-31.4 устройства.

При работе двоичного счетчика с использованием всех четырех разрядов сигнал с выхода 37.1 устройства подается на вход 35 устройства.

В случае исправного состояния всех основных триггеров 6.1-6.4 на их выходах F присутствует сигнал нулевого логического уровня, а на выходах F триггеров 6.1 и 6.3 - единичный. При этом единичными разрешающими сигналами открыты следующие логические элементы устройства: первая группа входов элемента 2-2И-ИЛИ 14.1, вторая группа входов элемента 2-2И- ИЛИ 12.2, первые группы входов элементов 2-2И-ИЛИ 14.2-14.4, первые группы входов элементов 2-2И-ИЛИ 12.3 и 13.3, вторая группа входов элемента 13.2, первая группа входов элемента 2-2И-ИЛИ 12.4 и первая группа входов элемента 2-2И-ИЛИ 13.4. Одновременно с этим для

прохождения синхроимпульсов счета закрываются следующие логические элементы устройства; вторые группы входов элементов 2-2И-ИЛИ 14.1-14.4, первые группы входов элементов 2-2И-1/1ЛИ 12.2 м 13.2, вторые группы входов элементов 2-2И-ИЛИ 12.3 и 13.3, вторые, группы входов элементов 2-2И-ИЛИ 12.4 и 13.4, элемент И 17 и элемент 2-2И-ЙЛИ 13.5 по обеим группам входов.

Подсчет импульсов, поступающих на первый синхровход 34 устройства, производится по следующей логической ветви предлагаемого двоичного счетчика,

Импульсы поступают на счетный вход 34 и счтеный вход триггера 6.1, а состояние его выхода через открытую первую группу входов элемента 2-2И-ИЛИ 14.1 на первый выход 37.1 счетчика и через соединение 37., открытую вторую группу входов элемента 2-2И-ИЛИ 13.2 - на счетный вход триггера 6.2. Состояние выхода (и его изменения) триггера 6.2 через открытую первую группу входов элемента 2-2И- ИЛИ 14.2 поступает на выход 37.2 и через первую группу входов элемента 2-2И-ИЛИ 13,3 на счетный вход триггера 6.3. Состояние сигнала на выходе триггера 6.3 (и его изменения) через первую группу входов элемента 2-2И-ИЛИ 14.3 поступает на выход 37.3, счетчика и через первую группу входов элемента 2-2И-ИЛИ 13.4 - на счетный вход триггера 6.4. Значение состояний (и их изменение) с выхода резервного триггера 6,5 на выход счетчмка в этом случае не поступает. та,к как вторая группа входов элемента 2-2И-ИЛИ 14.4 закрыта.

При отказе какого-либо основного триггера разряда на соответствующем выходе F формируется сигнал единичного логического уровня и данный триггер исключается из режима функционирования двоичного счетчика. При реконфигурации работоспособностм структуры двоичного счетчика используется функция не замещения любого из основных триггеров резервным, а функция вытеснения.

Рассмотрим пример, когда отказал триггер 6.1 первого разряда. В этом случае двоичный счетчик будет функционировать следующим образом. На выходе F триггера 6.1 формируется сигнал логического нуля, а на выходе F - сигнал логической единицы. Сигнал логического нуля с выхода F закрывает следующие логические элементы: первую группу входов элемента 2-2И- ИЛИ 14,1 и вторую группу входов элемента 2-2И-ИЛИ 12.2. Единичный логический уровень с выхода F открывает следующие логические элементы двоичного счетчика:

вторую группу входов элемента 2-2И-ИЛИ 14.1, первые группы входов элементов 2- 2И-ИЛИ 12.2 и 13.2, вторые группы входов элементов 2-2И-ИЛИ 14.2-14.4, 12.3 и 5 13,3, 12.4, первые группы входов элементов 2-2И-ИЛИ 13.4 и 13.5 и элемент И 17 Одновременно с этим закрываются следу- . ющие логические элементы двоичного п первые группы входов элементов 10 2-2И-ИЛИ 14.2, 14.4, 12.3. 13.3, 12.4. вто рые группы входов элементов 2-2И-ИЛИ 13.2, 13.4. Таким образом, к выходу 37.1 устройства подключен выход триггера 6 2 к 37.2 - 6.3 к 37,3 - 6.4 и к 37,4 - 6.5, 15 Импульсы счета в этом случае проходят по следующей логической ветви- со счетного входа 34 устройства через первую группу входов элемента 2-2И-ИЛИ 13 2 на счетный вход триггера 6,2. Состояние вы- 20 хода триггера 6.2 (и его изменения) через вторую группу входов элемента 2-2И-ИЛИ

14.1поступают на выхоц 37.1 устройства Далее через связь 37.1и.35, вторую группу входов элемента 2-2И-ИЛ1/1 13.3 - на счет25 ный вход триггера 6.3. Состояние выхода триггера 6.3 (и его изменения) через вто- . рую-группу входов элемента 2-2И-ИЛИ

14.2поступает на выход 37.2 устройства, а также через первую группу входов элемен30 та 2-2И-ИЛИ 13.4 - на счетный вход триггера 6.4. Состояние выхода триггера 6,4 (и его изменения) через вторую группу входов элемента 2-2И-ИЛ И 14.3 поступает на выход 37.3 устройства и через первую

35 группу входов элемента 2-2И-ИЛИ 13,5 на счетный вход триггера 6.5. Состояние выхода триггера 6,5 (и его изменения) через вторую группу входов элемента 2-2И-ИЛ И 14.4 поступает на выход 37.4 устройства

40 обеспечивая работоспособность двоичного счетчика без дополнительной переком- мутацим 1онтажных соединений между . элементами логической структуры предлагаемого устройства,

45 Наиболее показательным примером, иллюстрирующим принцип вытеснения, является случай отказа триггера второгсз разряда. В этом случае, на выходе F триггера 6.2 формируется сигнал логической

0 единицы, а на выходах F триггеров 6.1 6.3. 6,4 и 6.5 - остаются сигналы логического нуля.

Единичный потенциал на выходе триггера 6.2 F приводит к следующему измене- 5 нию в структуре двоичного счетчика. Закрываются первые группы входов элементов 2-2И-ИЛМ 14.2-14.4 и открываются их вторые группы входов, закрываются первая и вторая группы входов элемента 2г2И-ИЛИ 13.2. закрывается первая и открыаается вторая группы входов элемента 2-2И-ИЛИ 12.3, закрывается первая и открывается вторая группы входов элемента 2-2И-ИЛИ 13.3, закрывается первая и открывается вторая группы входов элемента 2-2И-ИЛИ 12.4, открывается первая группа входов элемента 2-2И-ИЛИ 13.4 и 13.5. Логическая ветвь подсчета импульсов в этом случае будет следующей: с входа 34 устройства на счетный вход триггера 6.1 и через первую группу входов элемента 2-2И-ИЛИ 14.1 - на выход 37.1 устройст- ва. Далее через соединение 37.1-35, вто- группу входов элемента 2-2И-ИЛИ 13.3 - на счетный вход триггера 6.3. Состояние выхода триггера 6.3 (и его изменения) через вторую группу входов элемента 2- 2И-ИЛИ 14.2 поступает на выход.

С входа 34 устройства на счетный вход триггера 6.1 и через первую группу входов элемента 2- И-ИЛИ 14.1 на выход 37.1 устройства. Далее через соединение 37., вторую группу входов элемента 2-2И-ИЛИ 13.3 - на счетный вход триггера 6.3. Состояние выхода триггера 6.3 (и его изменения) через вторую группу входов элемента 2- 2И-ИЛИ 14.2 поступает на выход 37.2 устройства, а также через первую группу входов элемента 2-2И-ИЛИ 13.4 - на счетный вход триггера 6.4. Состояние выхода триггера 6.4 (и его изменения) через вторую группу входов элемента 2-2И-ИЛИ

14.3поступает на выход 37.3 устройства, а также через первую группу входов элемента 2-2И-ИЛИ 13.5 - на счетный вход триггера 6.5, состояние сигнала на выходе которого через вторую группу входов элемента 2-2И-ИЛИ 14.4 поступает на выход

37.4устройства.

Таким образом, триггер 6.1 работает на выход 37.1 устройства, триггер 6.2 остается выключенным из работы, триггер 6.3 работает на выход 37,2 устройства, триггер

6.4- на выход 37.3 и триггер 6.5 - на выход 37.4 устройства. То есть триггеры 6.36.5 вытеснили триггер 6.2 из работоспособной структуры пре,цлагаемого устройства.

Замена отказавших триггеров 6.3 и 6.4 третьего и четвертого разрядов производится аналогичным образом как и триггера 6.2 второго разряда. То есть при отказе триггера 6.3 на его выходе F формируется единичный логический уровень сигнала. При этом триггеры 6.1 и 6.2 работают соответственно на выходы 37.1 и 37.2 устройства, триггер 6.3 заменяется триггером 6.4. а триггер 6.4 заменяется резервным триггером 6.5.

Таким образом, в двоичном счетчике осуществляется автоматическая реконфигурация работоспособной структуры при .отказе одного из основных разрядов, что

создает возможность обеспечения работоспособности логического блока автоматики и вычислительной техники без замены данной интегральной микросхемы, без применения специальных диагностических

процедур локализации места неисправности.

Формула изобретения Двоичный счетчик, содержащий эле- 15 мент И, элемент ИЛИ, четыре основных и резервный разряды, причем первый разряд содержит триггер, два элемента И-НЕ и элемент 2-2И-ИЛИ, второй, третий и четвертый разряды содержат триггер, три 20 элемента 2-2И-ИЛИ и два элемента И-НЕ, резервный разряд содержит триггер, два элемента И-НЕ, элемент И и элемент 2-2И-1/1ЛИ, первый синхровход счетчика . соединен со счетным входом триггера пер- 25 вого разряда и с вторым входом первой группы входов второго элемента 2-2И- ИЛИ второго разряда, второй синхровход счетчика соединен с первым входом второй группы входов вторых элементов 2- 30 2И-ИЛИ второго и третьего разрядов, вход разрешения предустановки счетчика соединен с первым входом элемента И-НЕ счетчика, второй вход которого объединен с входом элемента ИЛИ счетчика и соеди- 35 ней с входом установки в О счетчика, вход предварительной установки первого разряда соединен с первым входом первого элемента И-НЕ первого и с вторым входом первой группы входов первого 40 элемента 2-2И-ИЛИ второго разрядов, вход предварительной установки второго разряда соединен с вторым входом второй группы входов первого элемента 2-2И- ИЛИ одноименного и с первым входом 5 второй группь) входов первого элемента 2- 2И-ИЛИ третьего разрядов, вход предварительной установки третьего разряда соединен с вторым входом первой группы входов первого элемента 2-2И-ИЛИ одно- 0 именного и с первым входом второй группы входов первого элемента 2-2И-ИЛИ четвертого разрядов, вход предварительной установки четвертого разряда соединен с вторым входом первой группы 5 входов первого элемента 2-2И-ИЛИ одноименного и с вторым входом элемента И резервного разрядов, выход элемента И-НЕ счетчика соединен с третьими входами первых и с вторыми входами вторых элементов И-НЕ каждого, включая и резерз - ый, разряда, выход элемента ИЛИ счетчика соединен с вторыми входами , первых элементов И-НЕ каждого, включая и резервный, разряда, выходы которых соединены с 5-8ходами триггеров и с первы- ми входами вторых элементов И-НЕ одноименного разряда, выход второго элемента И-НЕ каждого, включая и резервный, разряда соединен с R-входом триггера одноименного разряда, выход первого элемента 2-2И-ИЛИ второго, третьего и четвертого разрядов соединен с первым входом первого элемента И-НЕ одноименного разряда, выход первого элемента И резервного разряда соединен с первым входом первого элемента И-НЕ одноименного разряда, выход второго элемента 2-2И-ИЛИ каждого, кроме первого, разряда соединен со счетным входом триггера одноименного разряда, прямой выход триггера первого разряда соединен с первым входом первой группы входов элемента 2-2И-ИЛИ одноименного разря-. да, выход которого является первым информационным выходом счетчика, прямой выход триггера второго разряда соединен с вторым входом второй группы входов элемента 2-2И-ИЛ1Л первого разряда, с первым входом первой группы входов второго элемента 2-2И-ИЛ1/1 второго разряда, с первым входом второй группы входов второго элемента 2-2И-ИЛИ третьего разряда и с первым входом первой группы входов третьего элемента 2-2И-ИЛИ второго разряда, выход которого является вто- рым информационным выходом счетчика, прямой выход триггера третьего разряда соединен с вторым вхо дом второй группы входов третьего элемента 2-2И-ИЛИ второго разряда, с первым входом первой группы входов второго элемента 2-2И- ИЛИ четвертого разряда, с первым входом второй группы входов второго элемента 2И-ИЛИ резервного разряда и с первым входом первой группы входов третьего элемента 2-2И-ИЛИ третьего разряда, выход которого является третьим информационным выходом счетчика, прямой выход триггера четвертого разряда соединен с вторым входом второй группы входов третьего злемента 2 2И-ИЛИ третьего разряда, с первым входом первой группы входов элемента 2-2И-ИЛИ резервного разряда и с первым входом первой группы входов третьего элемента 2-2И-ИЛИ чет- вертого разряда, выход которого является четвертым информационным выходом счетчика, прямой выход триггера резервного разряда соединен с вторым входом второй группы входов третьего элемента

2-2И-ИЛИ четвертого разряда, отличающийся тем, что, с целью повышения достоверности функционирования путем включения в структуру счетчика средств функционального контроля и автоматизации процесса восстановления работоспособности, он дополнительно содержит второй элемент ИЛИ, а в каждом, кроме первого, разряде дополнительно содержит элемент ИЛИ/ИЛИ-НЕ и элемент И, причем вход установки в исходное состояние средств функционального контроля счетчика соединен с RF-ВХОДО М триггера каждого, включая и резервный, разряда, инверсный выход Отказ триггера первого разряда соединен с вторым входом первой группы входов элемента 2-2И-ИЛИ одноименного разряда и с первым входом второй группы входов первого элемента 2-2И-ИЛИ второго разряда, прямой выход Отказ триггера первого разряда соединен с первым входом второй группы входов элемента 2-2И-ИЛИ одноименного, с первым входом первой группы входов первого элемента 2-2И-ИЛИ, с первым входом первой группы входов второго элемента 2-2И-ИЛИ и с первыми входами элементов ИЛИ/ИЛИ-НЕ и И второго разрядов, прямой выход Отказ триггера второго разряда соединен с вторыми входами элементов ИЛИ/ИЛИ-НЕ и И одноименного разряда, инверсный выход элемента ИЛИ/ИЛИ-НЕ второго разряда соединен с вторым входом первой группы входов третьего элемента 2-2И-ИЛИ, с вторым входом второй группы входов второго элемента 2-2И-ИЛИ одноименного и с первым входом первой группы входов первого элемента 2-2И-ИЛИ третьего разрядов, прямой выход элемента ИЛИ/ИЛИ-НЕ второго разряда соединен с первым входом второй группы входов третьего элемента 2-2И-ИЛИ одноименного, с вторым входом второй группы входов первого и второго элементов 2-2И-ИЛИ и с первыми входами элементов ИЛИ/ИЛИ-НЕ и И третьего разрядов, инверсный выход элемента ИЛИ/ИЛИ-НЕ второго разряда дополнительно соединен с вторым входом первой группы входов второго элемента 2- 2И-ИЛИ третьего разряда, выход элемента И второго разряда соединен с первым входом второго элемента ИЛИ счетчика, инверсный выход Отказ триггера третьего разряда соединен с вторым входом первой группы входов второго элемента 2-2И- ИЛИ четвертого разряда, прямой выход Отказ триггера третьего разряда соединен с вторыми входами элементов И/ИЛИ-НЕ и И одноименного и с вторым входом второй группы входов второго элемента 2-2И-ИЛИ четвертого разрядов, инверсны выход элемента ИЛИ/ИЛИ-НЕ третьего разряда соединен с вторым входом первой группы входов третьего элемента 2-2И-ИЛИ одноименного и с первым входом первой группы входов первого элемента 2-2И-ИЛИ четвертого разрядов, прямой выход элемента ИЛИ/ИЛИ-НЕ третьего разряда соединен с первым входом второй группы входов третьего элемента 2-2И-ИЛИ одноименного, с вторым входом второй группы входов первого элемента 2-2И-ИЛИ, с первыми входами элементов ИЛИ/ИЛИ-НЕ и И четвертого и с вторым входом первой группы входов элементов 2-2И-ИЛИ резервного разрядов, выход элемента И третьего разряда соединен с вторым входом второго элемента ИЛИ счетчика, прямой выход Отказ триггера четвертого разряда соединен с вторыми входами элементов ИЛИ/ИЛИ-НЕ и И одноименного и с вторым входом второй группы входов элемента 2-2И-ИЛИ резервного разрядов, инверсный выход элемента ИЛИ/ИЛИ- НЕ четвертого разряда соединен с вторым входом первой группы входов третьего элемента 2-2И-ИЛИ одноименного разряда, прямой выход элемента ИЛИ/ИЛИ-НЕ четвертого разряда соединен с первым входом второй группы входов третьего элемента 2-2И-ИЛИ одноименного, с первым входом первого элемента И, с первыми входами элементов ИЛИ-ИЛИ-НЕ и И резервного разрядов, выход элемента И четвертого разряда соединен с третьим входом второго элемента ИЛИ счетчика, прямой выход Отказ триггера резервного ра.зряда соединен с вторыми входами элементов ИЛИ/ИЛИ-НЕ и И одноименного разряда, выход элемента ИЛИ/ИЛИ-НЕ резервного разряда является выходом Частичный отказ счетчика, выход второго элемента И резервного разряда соединен с четвертым входом второго элемента ИЛИ счетчика, выход которого является выходом Отказ счетчика, а триггер каждого, включая и резервный, разряда содержит восемь элементов И-НЕ. три элемента НЕ. элемент ИЛИ и селектор-триггер, причем S-вход триггера соединен с первь1м входом первого элемента И-НЕ и с первым входом первой группы входов селектора-триггера, синхровход триггера

соединен с вторым входом первого, с первым входом второго элементов И-НЕ и с входом первого элемента НЕ, R-вход триггера соединен с вторым входом второго 5 элемента И-НЕ и с вторым входом второй группы входов селектора-триггера, выход первого элемента И-НЕ соединен с первым входом третьего элемента И-НЕ, выход второго элемента И-НЕ соединен с 10 вторым входом четвертого элемента И-НЕ, выход которого соединен с первым входом шестого элемента И-НЕ, с третьим входом первой и с четвертым входом четвертой групп входов селектора-триггера, а также с 15 вторым входом третьего элемента И-НЕ. выход которого соединен с первыми входами четвертого и пятого элементов И-НЕ, с третьим входом второй и с вторым входом третьей групп входов селектора-триггера, 20 выход первого элемента НЕ соединен с первым входом третьей и с третьим входом четвертой групп входов селектора-триггера, а также с вторыми входами пятого и шестого элементов И-НЕ, выходы которых 25 соединены соответственно с первым входом седьмого и с вторым входом восьмого элементов И-НЕ, выход первого элемента НЕ дополнительно соединен с входом второго элемента НЕ, выход которого соеди- 30 нен с входом элемента ИЛИ, выход элемента ИЛИ соединен с вторым входом первой, с первым входом второй групп входов селектора-триггера и с входом третьего элемента НЕ, выход которого сое- 5 динен с четвертым входом третьей и с первым входом четвертой групп входов селектора-триггера, вход установки а О средств функционального контроля триггера соединен с первым входом пятой груп- 0 пы входов селектора-триггера, выход седьмого элемента И-НЕ является прямым выходом триггера и соединен с первым входом восьмого элемента И-НЕ и с вторым входом четвертой группы входов се- 5 лектора-триггера, выход восьмого элемента И-НЕ является инверсным выходом триггера и соединен с вторым входом седьмого элемента И-НЕ.и с третьим входом третьей группы входов селектора-триг- 0 гера, прямой выход которого является прямым выходом Отказ триггера и соединен с вторым входом своей пятой группы входов, инверсный выход селектора-триггера является инверсным выходом Отказ 5 триггера.

39

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоично-десятичный счетчик | 1988 |

|

SU1517133A1 |

| Двоичный счетчик | 1988 |

|

SU1529447A1 |

| Счетчик-делитель | 1988 |

|

SU1529446A1 |

| Счетчик-делитель | 1989 |

|

SU1598169A1 |

| Двоично-десятичный счетчик | 1989 |

|

SU1676098A1 |

| Двоичный счетчик | 1988 |

|

SU1555857A1 |

| Двоичный счетчик | 1989 |

|

SU1644374A1 |

| Двоичный счетчик | 1988 |

|

SU1684927A1 |

| Двоично-десятичный счетчик | 1989 |

|

SU1622946A1 |

| Двоичный счетчик | 1991 |

|

SU1803975A1 |

Изобретение относится к импульсной и вычислительной технике, в частности к импульсным счетчикам, и может быть использовано в устройствах промышленной автоматики и вычислительной техники. Целью изобретения является повышение достоверности функционирования и автоматизации процесса восстановления работоспособности счетчика. Счетчик выполнен на самоконтролируемых триггерах и логических элементах И, ИЛИ, ИЛИ/ИЛИ-НЕ, И-НЕ 2-2И-ИЛИ и собран по многоразрядной схеме. При отказе одного из основных разрядов счетчик автоматически переходит на резервную работоспособную структуру. Структурно-логическая организация двоичного счетчика позволяет произвести самовосстановление работоспособности за счет резервного разряда, что повышает его отказоустойчивость и интенсивность восстановления работоспособности. 1 табл., 2 ил.

ФигЛ

Фиг. 2

| Применение интегральных микросхем в электронной вычислительной технике | |||

| Справочник | |||

| Под ред | |||

| Б.Н.Файзулаева, Б.В.Тарабрина | |||

| - М.: Радио и связь, 1987, с | |||

| Приспособление с иглой для прочистки кухонь типа "Примус" | 1923 |

|

SU40A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Двоичный счетчик | 1988 |

|

SU1529447A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-10-07—Публикация

1989-01-03—Подача