СП

1C

со

Фиг.}

Изобретение относится к радиотехнике и может быть использовано в технике средств связи ддя получения дискретного множества частот.

Цель изобретения - повьшение быстродействия и чистоты спектра выходного сигнала.

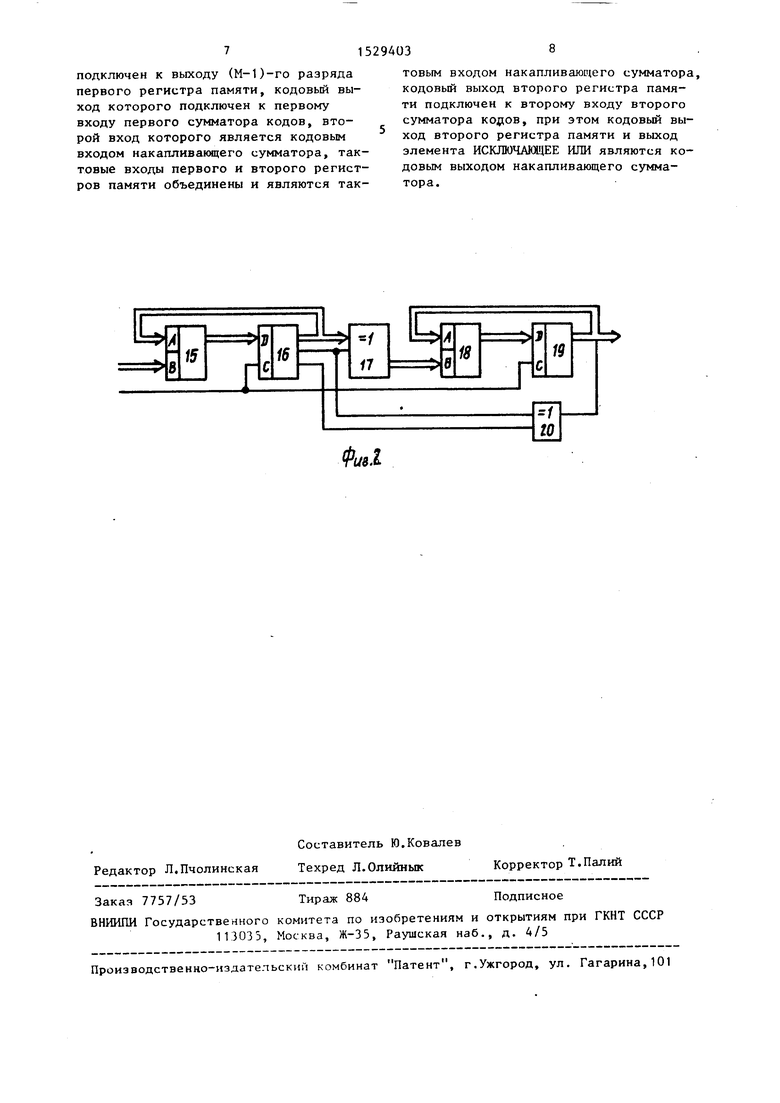

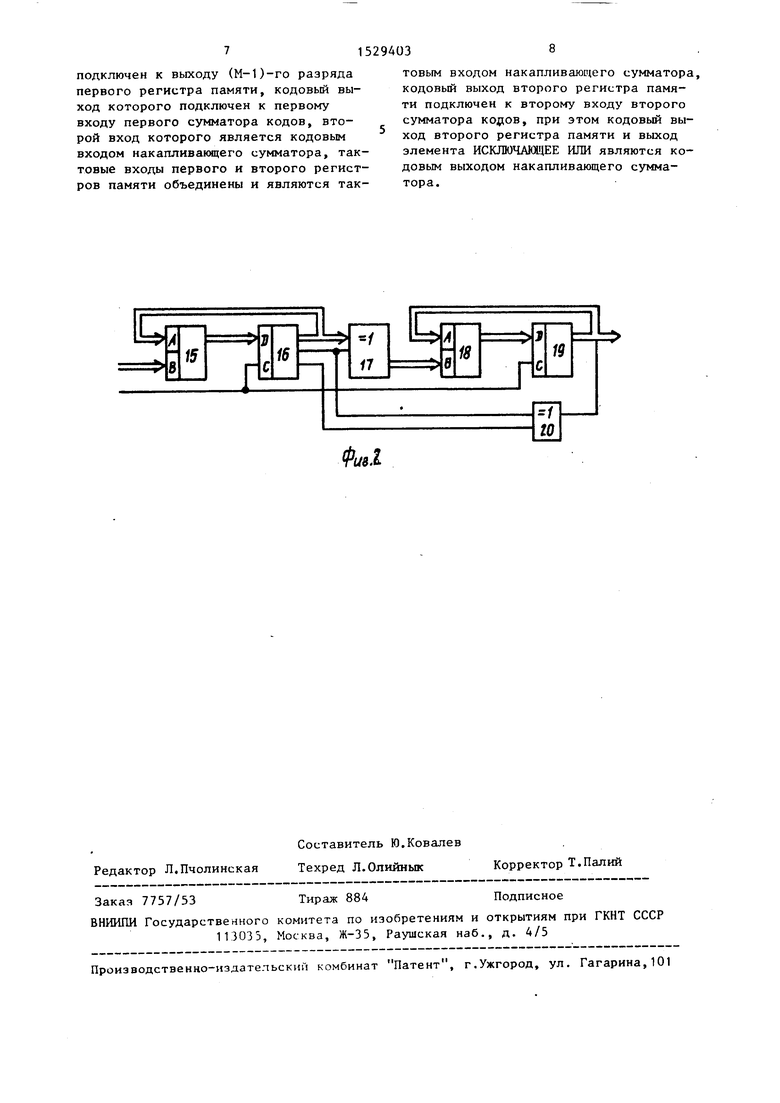

На фиг. 1 представлена электрическая структурная схема цифрового синтезатора частоты; на фиг. 2 - электрическая структурная схема накапливающего сумматора.

Цифровой синтезатор частоты содержит накапливающий сумматор (НС) 1, первый преобразователь 2 кода, ограничитель 3 с регулируемым порогом ограничения, коммутатор 4, цифроанало- говый преобразователь (ЦАП) 5, фильтр 6 нижних частот, генератор 7 опорной частоты, второй 8 и третий 9 преобразователи кода. При ограничитель 3 содержит регистр 10 кодов, первый 11 и второй 12 компараторы кодов, первый 13 и второй 14 JK-триг геры.

Накапливающий сумматор 1 образуют первый сумматор 15 кодов, первый регистр 16 памяти, блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 17, второй сумматор 18 кодов, второй регистр памяти 19 и элемент ИСКЛЮЧАМЦЕЕ ИЛИ 20.

Цифровой синтезатор частоты работает следующим образом.

В зависимости от входного кода на установочном входе цифрового синтезатора частоты на выходе НС 1 появляется текущее значение кода установленной частоты. Так как НС 1 выполнен в виде последоват ельно соединенных сумматора 15, регистра 16 памяти, блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 17, сумматора 18 и регистра 19 памяти, а также элемента ИСЮГОЧАЮЩЕЕ lUffl 20, изменение кода на его выходе опи

сывается параболической периодической функцией Y Х .

Если старший разряд выходного кода НС 1, который задается состоянием выхода второго блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 20, равен нулю, то код с его выхода проходит через первый преобразователь кода 2 без изменения, формируется отрицательная полуволна параболоиды, Если старший разряд выходного кода НС 1 равен единице, то код преобразуется в обратный и формируется положительная полуволна. В результате сигнал на

выходе первого преобразователя кода 2 описывается функцией:

+

Sin ЗХ

Ь

+...).

5

5

0

5

0

Если полученную параболоиду ограничить, то в гармонических составля- ющих параболоиды появится коэффициент, зависящий от порога ограничения. Me-г няя порог ограничения, можно менять соотнощения гармоник в спектре выходного сигнала вплоть до полного отсутствия какой-либо гармоники.

Код с выхода первого преобразователя 2 кода поступает в ограничителе 3 на входы регистра 10 и компараторов 11 и 12. Если значение данного кода меньше кода на выходе преобразователя 9 кода, но больше кода на выходе преобразователя 8, то на К- входах JK-триггеров 14 и 13 имеется значение 1, а на J-входах - О. По тактовому импульсу, поступающему с генератора 7, данный код записывается в регисто 10. а JK-триггеры 13 и 14 имеют на инверсных выходах уровень 1. При этом коммутатор 4 пропускает код с выхода регистра 10, который преобразуется в ЦАП 5 и фильтре 6 в аналоговое напряжение. Если код с выхода преобразователя 2 больше кода на выходе преобразователя 9, то на J-входе второго JK - триггера 14 присутствует уровень 1, а на К-вхо- де - уровень О, а на входах первого JK-триггера 13 наоборот. После тактового импульса второй JK-триггер 14 устанавливается в единичное состояние, а первый JK-триггер 13 - в нулевое, коммутатор 4 пропускает код, установленный на выходе третьего преобразователя 9 кода. Если код с выхода первого преобразователя 2 кода меньше кода, установленного на вы5 ходе второго преобразователя 8 кода, то состояние выходов JK-триггеров 13 и 14 меняется на обратное относительно второго варианта и коммутатор 4 пропускает код, установленный на вы0 ходе второго преобразователя 8 кода.

Формирование периодической параболической функции в НС 1 производится путем двойного интегрирования кода на кодовом входе НС 1. Первый интегратор состоит из сумматора 15 и регистра 16 памяти и формирует пилообразный сигнал. Если (М-1)-й разряд первого регистра памяти 16 равен нулю, то

блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 17 пропускает код с кодового выхода первого регистра 16 памяти без изменени если (м-1)-и разряд равен единице, т код инвертируется. Таким образом, на выходе блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 17 формируется сигнал с треугольной характеристикой, который подается на вход второго интегратора, со- держащего сумматор 18 и регистр 19 памяти. Для получения положительной полуволны параболоиды на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 20 формируется сигнал старшего разряда кодового сиг нала НС 1. Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 20 реализует функцию

F м (м-1) + м (м-.} где Х, Х(дд, - сигналы с М-го и

(М-1)-го старших разрядов первого регистра 16 памяти.

Определив оптимальный порог ограничения для различных значений входных кодов цифрового синтезатора частоты по минимальным паразитным спект- ральным составляющим в выходном сигнале и записав его в память преобразователей 8 и 9 кода, можно значительно улучшить храктеристики выходного спектра цифрового синтезатора частот.

Формула изобретения

1. Цифровой синтезатор частоты, содержащий последовательно соединенные генератор опорной частоты, накапливающий сумматор и первьш преобразователь кода, последовательно соединенные коммутатор, цифроаналоговый преобразователь и фильтр нижних частот, при этом кодовый вход накапливающего сумматора является установочным входом цифрового синтезатора частоты отличающийся тем, что, с целью повьщ1ения быстродействия и чистоты спектра выходного сигнала, введены второй преобразователь кода, третий преобразователь кода и ограничитель с регулируемым порогом огра- ничения, первый, второй, третий входы, первый и второй выходы которого соответственно соединены с выходом первого преобразователя кода, выходом второго преобразователя кода, вы- ходом третьего преобразователя кода, первым входом коммутатора и вторым входом коммутатора, третий и четвертый входы которого соответственно

д

0

5 о

с О 0

5

подключены к выходу второго преобразователя кода и к выходу третьего преобразователя кода, тактовый вход ограничителя с регулируемым порогом ограничения объединен с тактовыми входами коммутатора, цифроаналогово- го преобразователя, второго преобразователя кода и третьего преобразователя кода и подключен к выходу генератора опорной частоты, а кодовые входы второго и третьего преобразователей кода соединены с кодовым входом накапливающего сумматора.

2.Синтезатор по п. 1, отличающийся тем, что ограничитель с регулируемым порогом ограничения содержит первый компаратор кодов, второй компаратор кодов, первый JK- триггер, второй JK-триггер и регистр кодов, кодовый вход которого объединен с первым входом первого компаратора кодов и с вторым входом второго компаратора кодов и является первым входом ограничителя с регулируемым порогом ограничения, второй вход первого компаратора кодов и первьй вход второго компаратора кодов являются соответственно вторым и третьим входами ограничителя с регулируемым порогом ограничения, первый и второй выходы первого компаратора кодов подключены соответственно к J-входу и К- входу первого JK-триггера, первьп1 и второй выходы второго компаратора кода соединены соответственно с J- входом и К-входом второго JK-триггера, тактовый вход которого объединен

с тактовым входом первого JK-триггера и с тактовым входом регистра кода и является тактовым входом ограничителя с регулируемым порогом ограничения, первым и вторым выходами которого соответственно являются выход регистра кода и объединенные выходы первого и второго JK-триггеров.

3.Синтезатор по п. 1, о т л и - чающийся тем, что накапливающий сумматор содержит последовательно соединенные первьшсумматор кодов, nepBbifi регистр памяти, блок элементов ИСКЛЮЧАЮ1 1ЕЕ ИЛИ, второй сумматор кодов и второй регистр памяти, а также элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого подключен к выходу старшего М-го разряда первого регистра памяти, второй вход элемента ИСКЛЮЧАЛЛЦЕЕ ИЛИ объединен с вторым входом первого блока элементов ИС1ШОЧАЮ1ДЕЕ ИЛИ и

подключен к выходу (М-1)-го разряда первого регистра памяти, кодовый выход которого подключен к первому входу первого сумматора кодов, второй вход которого является кодовым входом накапливающего сумматора, тактовые входы первого и второго регистров памяти объединены и являются тактовым входом накапливающего сумматора, кодовый выход второго регистра памяти подключен к второму входу второго сумматора кодов, при этом кодовый выход второго регистра памяти и выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ являются кодовым выходом накапливающего сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор частот | 1985 |

|

SU1337989A1 |

| Синтезатор частот | 1986 |

|

SU1337990A1 |

| Цифровой синтезатор частот | 1985 |

|

SU1305823A1 |

| Синтезатор частот | 1988 |

|

SU1584105A2 |

| Частотный модулятор | 1989 |

|

SU1626320A1 |

| Цифровой синтезатор частот | 1986 |

|

SU1394393A1 |

| Цифровой синтезатор частот | 1984 |

|

SU1197043A1 |

| СИНТЕЗАТОР ЧАСТОТ | 1990 |

|

RU2030829C1 |

| Цифровой синтезатор частот | 1989 |

|

SU1704265A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

Изобретение относится к радиотехнике. Цель изобретения - повышение быстродействия и чистоты спектра выходного сигнала. Синтезатор содержит накапливающий сумматор (НС) 1, преобразователи 2,8 и 9 кода, ограничитель 3 с регулируемым порогом ограничения, коммутатор 4, ЦАП 5, фильтр 6 нижних частот и г-р 7 опорной частоты. Входной код после преобразования в преобразователях 8 и 9, а также в последовательно соединенных НС 1 и преобразователе 2 поступает на ограничитель 3. При этом в НС 1 формируется периодическая параболическая ф-ция путем двойного интегрирования кода. Если полученную параболоиду ограничить, то в гармонических составляющих параболоиды появится коэф., зависящий от порога ограничения. Меняя порог ограничения, можно менять соотношения гармоник в спектре выходного сигнала вплоть до полного отсутствия какой-либо гармоники. Определив оптимальный порог ограничения для различных значений входных кодов синтезатора по минимальным паразитным спектральным составляющим в выходном сигнале и записав его в память преобразователей 8 и 9, можно улучшить х-ки выходного спектра. В синтезаторе может быть различным выполнение ограничителя 3 и НС 1. 2 з.п.ф-лы, 2 ил.

| Цифровой синтезатор частоты | 1986 |

|

SU1374398A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифровой синтезатор частоты | 1980 |

|

SU966849A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-12-15—Публикация

1988-02-16—Подача