СлЭ «

4

СО

со

00

ГЧ)

113

. Изобретение относится к радиотехнике и может быть использовано для получения сетки частот в системах связи, гидролокации, в устройствах вычислительной и измерительной техники .

Цель изобретения - повышение спектральной чистоты выходного сигнала.

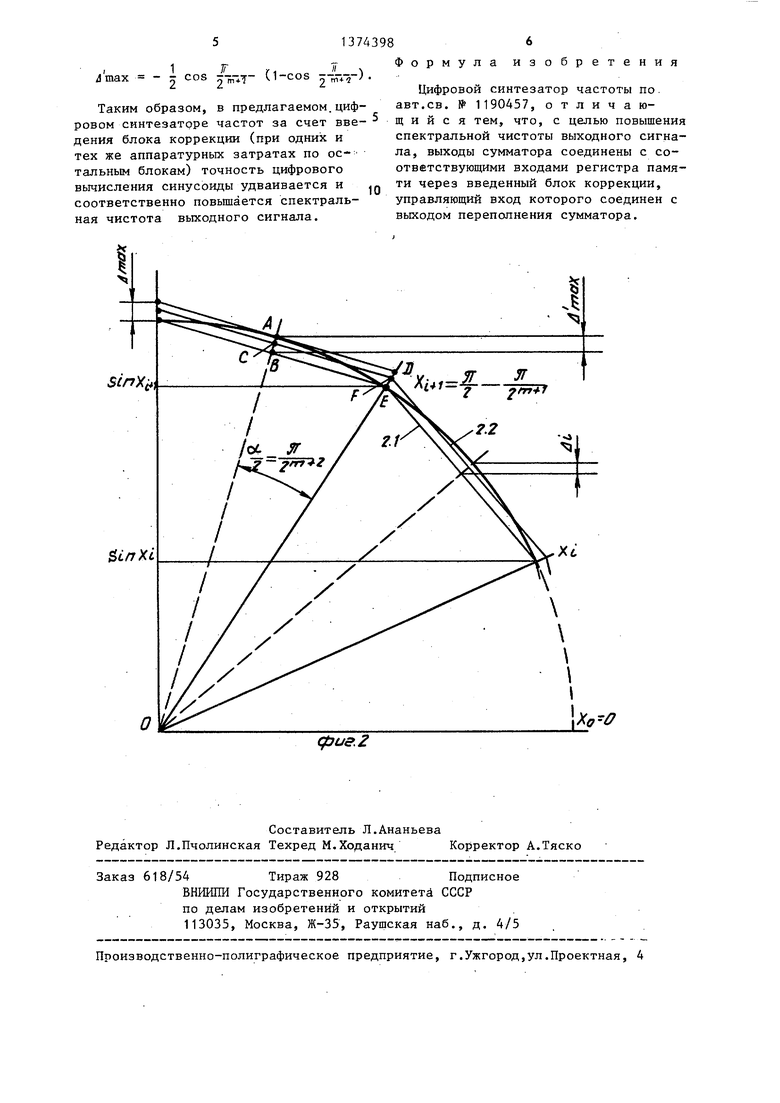

На фиг.1 представлена структурная электрическая схема цифрового синхронизатора частот; на фиг.2 - аппроксимация синусоиды,(первый квадрант) обычным способом - кусочно-линейная кривая 2.1 и по средним точкам - кусочно-линейная кривая 2.2.

Цифровой синтезатор частоты содержит блок 1 установки частоты, накопитель 2, блок 3 синхронизации, регистр 4 памяти, преобразователь 5 ко- дов, перемножитель 6 кодов, сумма- тор 7, первый 8 и второй 9 блоки памяти, блок 10 коррекции, цифроанало- говый преобразователь (ДАЛ) 11 и фильтр 12 нижних частот (ФНЧ).

Цифровой синтезатор частот работает следующим образом.

При помощи блока 1 установки частоты в двоичном коде устанавливается число а, определяющее значение выход ной частоты цифрового синтезатора частот. При работе на выходе накопителя 2 результирующие значения чисел обновляются с частотой синхронизации fc, задаваемой блоком 3 синхрониза- ции. Код числа В с выходов накопите- ля 2 поступает на входы преобразовате ля 5 кодов, который в зависимости от четности или нечетности числа переполнений накопителя 2 формирует пря- мой или дополнительный коды числа В.

Младшие из выходных разрядов преобразователя 5 кодов образуют 2 слов (по наибольшему возможному числу, ступенчатых приращений на каждый линейный участок аппроксимируемой синусоидальной функции). В результате в произвольный тактовый момент частоты fc на выходе преобразователя 5 кодов формируется i-й адрес обращения к блокам 8 и 9 памяти и множитель j, поступающий на вторые входы перемножителя 6 кодов (,1,...,2 -1; ,1,...,2 -1).

В -первый блок 8 памяти занесены 2 цифровых значений А; А +0,5 ui, соответствующих равномерно расположенным на дуге единичной окружности

аргументам Xj -

в пределах

одного квадранта (где А,- sin х-; 0,5 iJ i - поправка, связанная с аппроксимацией синусоиды линейными участками со знакопеременной погрешностью, т.е. аппроксимация по средним точ-. кам - кривая 2,2).

Значение ai находят из треугольника AOD (фиг.2): ,

д i Е D

ED OD-DE; OD.

sin al (i+1) , OA . cos .2

откуда ED

gA

- OE,

Для единичной окружности.

ED

cos ot/2

тогда

Ai ED-sinc (i+i) gi(i+i)

° В результате получают величину

А

С НО, 5

cos 01/2

sin of (i+1)

или

(1+0,5

1г22Ё 1/2

) А,.

Во второй блок 9 памяти занесены приращения синусоидальной функции от каждого линейного участка ее кусочно-линейной аппроксимации

,,,-А

откуда

W-Cij.n ; ol/2 V , . В-(НО,5-------7--,)(sin

или

в;

(i+l)-sin(/-i)

(но,5 )

COS /2 1

Таким образом, величины A , и В , предлагаемого устройства оказывают/ п с 1-COS ч ся в (.1+0,5ivT большими,чем

величины А; и В ., используемые в прототипе.

Значения Л;И В. одновременно выбираются из блоков 8 и 9 памяти адресными выходами старших разрядов преобразователя 5 кодов и поступают соответственно на первые входы перемножителя 6 кодов и вторые входы сум- .матора 7.

Величина В ., умноженная на двоичную кодовую комбинацию j /2 числа j, образующуюся на выходах младших разрядов преобразователя 5 кодов, дает положительную поправку к величине А. грубого угла х ,- при определении модуля функции А ., для любого

текущего аргумента

в;,

где сомножитель масштабный коэф- фициент, учитывающий, что операции умножения и сложения вьшолняются над двоичными числами меньше единицы.

В результате на выходе сумматора 7 формируется последовательность дне- кретных цифровых значений амплитуды линейной аппроксимации синусоидальной функции по средним точкам, которая поступает на информационный вход блока 10 коррекции.

Аппроксимация синусоиды по средним точкам влечет за собой появление значений А .. 1 на линейных участках, примыкающих к углам 2пТ + f/2, поэтому при переполнении суммато- ра 7 сигнал переноса поступает на управляющий вход блока 10 коррекции и устанавливает все его выходные разряды в единичное состояние. В обычном алгоритмическом режиме блок Ю коррекции пропускает двоичный код AV с выхода сумматора 7 на вход регистра 4 памяти без изменения.

На выходе SGN преобразователя 5 кодов состояние изменяется на каждом втором импульсе переполнения накопителя 2 в результате на выходе SGN формируется импульсная последовательность, соответствующая изменениям знака выходного сигнала. В регистре 4 памяти вычисленные значения модуля амплитуды и знака амплитуды хранятся в течение времени 1/fc, после чего сменяются новыми. Код синусоиды с выхода регистра 4 памяти поступает на разрядные входы ЦАП 11, причем сигнал с выхода SGN регистра 4 памяти поступает на знаковый вход ЦАП 11. В результате на выходе последнего формируется синусоидальный сигнал, KOTopbtft через ФНЧ 12 поступает на выход цифрового синтезатора частоты.

Частота выходного сигнала f. afc/4N, где емкость накопителя 2, которая численно совпадает с максимальным числом дискретных точек формирования синусоидального сигнала в пределах одного квадранта. Следовательно, если , то происходит синтез минимальной выходной частоты, равной fc/4N. Это же выражение определяет и шаг дискретности частоты на выходе синтезатора частоты. Часть младших k разрядов накопителя 2 можно не использовать, поэтому .

Наибольшее значение максимальной погрешности отклонения каждого линейного участка (из 2 возможных) от синусоиды / и max/ в пределах квадранта находится в точке х /2.

, , 0,5(1-cos о1/2)

/ /5 max/ - -7о

cos of/2

или

-.mtJx

, 0,5(1-COS

Значение погрешности /иmax/ зависит только от числа линейных участков на четверть периода, например, при (32 линейных участка) 0,001506, что соответствует двенадцати точным разрядам вычисления значений синусоиды.

Вычисленное сумматором 7 значение синусоиды в интервале аргументов

1Г/2 - f/2 первого квадранта превьш1ает не только истинное, но и единичное значение на величину S /атах /, двоичный код которой в результате переполнения сумматора 7 при отсутствии блока 10 коррекции мог бы попасть на ЦА11 11 через регистр 4 памяти, что привело бы к неалгоритмическому спаду синусоидальной функции практически с единицы до нуля.Блок 10 коррекции устраняет эти возможные искажения выходного сигнала за счет поддержания единичного кода на своем выходе по сигналу переполнения сумматора 7.

В результате использования блока 10 коррекции наибольшее значение максимальной погрешности | „ц имеется на середине линейного участка при х, /2 и определяется вьфажением

сузиг.г

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор частот | 1983 |

|

SU1190457A1 |

| Цифровой синтезатор частот | 1979 |

|

SU813677A1 |

| Цифровой синтезатор частот | 1978 |

|

SU813675A1 |

| Цифровой синтезатор частоты | 1987 |

|

SU1429285A1 |

| Цифровой синтезатор изменяющейся частоты | 1988 |

|

SU1525861A1 |

| СИНТЕЗАТОР ЧАСТОТ | 1997 |

|

RU2137287C1 |

| Цифровой генератор периодических функций | 1987 |

|

SU1441372A1 |

| СИНТЕЗАТОР ЧАСТОТ | 1995 |

|

RU2119238C1 |

| Цифровой синтезатор изменяющейся частоты | 1985 |

|

SU1298836A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 1991 |

|

RU2020728C1 |

Изобретение относится к радиотехнике. Цель изобретения - повьше- ние спектральной чистоты выходного сигнала. Цифровой синтезатор частоты содержит блок 1 установки частоты, накопитель 2, блок 3 синхронизации, регистр 4 памяти, преобразователь 5 кодов, перемножитель 6 кодов, сумматор 7, блоки памяти 8 и 9, ЦАП 11, фильтр нижних частот 12. Для достижения цели в устройство введен блок коррекции (БК) 10, устраняющий возможные искажения выходного сигнала за счет поддержания единичного кода на своем выходе по сигналу переполнения сумматора 7. В результатов использования БК 10 наибольшее значение макс, погрешности будет на середине линейного участка. Т.о., за счет введения БК 10 (при одних и тех же аппаратурньпс затратах по остальным блокам) точность цифрового вычисления синусоиды удваивается и соответственно повьшается спектральная чистота выходного сигнала. 2 ил. с S (Л

| Цифровой синтезатор частот | 1983 |

|

SU1190457A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-02-15—Публикация

1986-09-17—Подача