N

Изобретение относится к вычислительной технике и может быть использовано в зaпoминaю ц ix устройствах и является усовершенствованием изобретения по авт.св. № 11375АО.

Цель изобретения - расширение функциональных возможностей устройства за счет диагностики и локализации ошибок

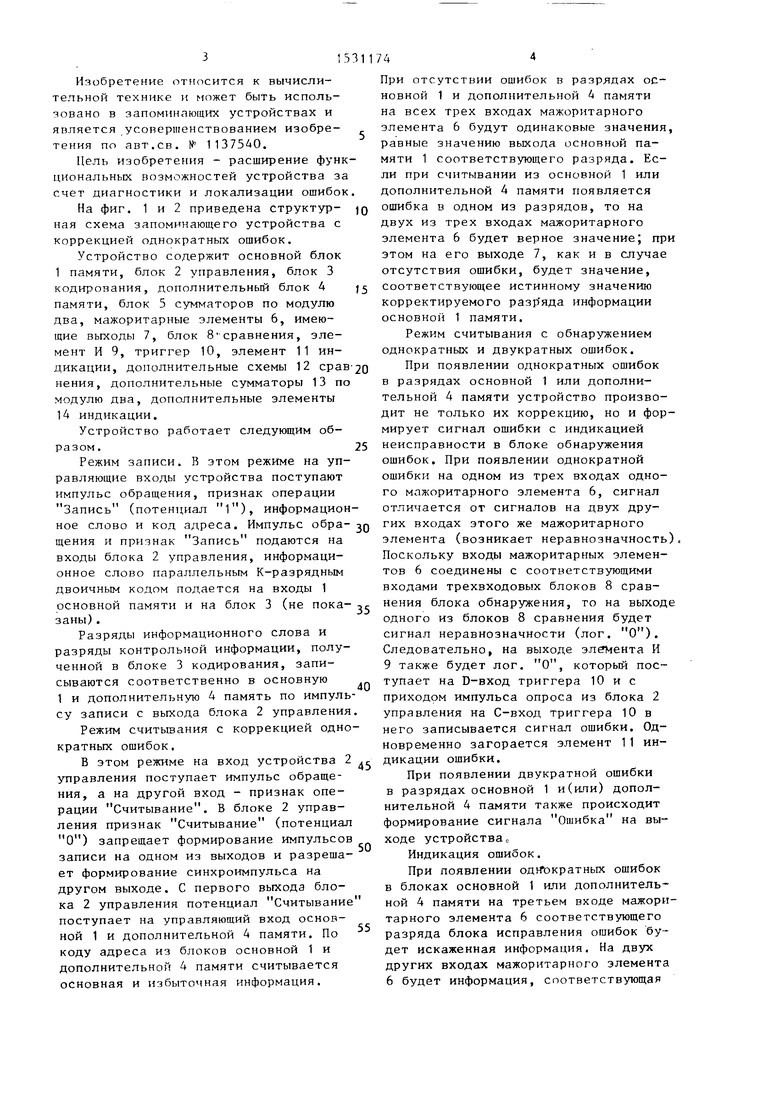

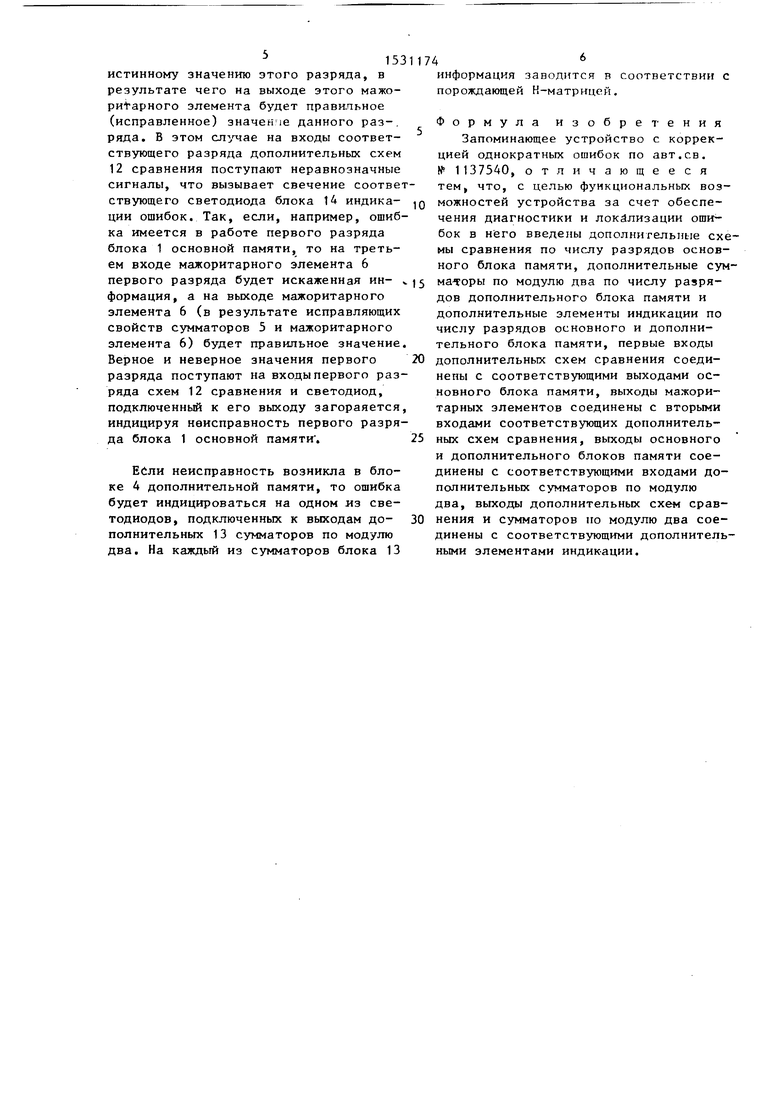

На фиг. 1 и 2 приведена структур- ная схема запоминающего устройства с коррекцией однократных ошибок.

Устройство содержит основной блок 1 памяти, блок 2 управления, блок 3 кодирования, дополнительный блок 4 памяти, блок 5 сумматоров по модулю два, мажоритарные элементы 6, имеющие выходы 7, блок 8 сравнения, элемент И 9, триггер 10, элемент 11 индикации, дополнительные схемы 12 срав нения, дополнительные сумматоры 13 по модулю два, дополнительные элементы 14 индикации.

Устройство работает следующим образом.

Режим записи. В этом режиме на управляющие входы устройства поступают импульс обращения, признак операции Запись (потенциал 1), информационное слово и код адреса. Импульс обра- щения и признак Запись подаются на входы блока 2 управления, информационное слово параллельным К-разрядным двоичным кодом подается на входы 1 основной памяти и на блок 3 (не пока- завы).

Разряды информационного слова и разряды контрольной информации, полученной в блоке 3 кодирования, записываются соответственно в основную 1 и дополнительную 4 память по импульсу записи с выхода блока 2 управления

Режим считьшания с коррекцией однократных ошибок.

В этом режиме на вход устройства 2 управления поступает импульс обращения, а на другой вход - признак операции Считывание. В блоке 2 управления признак Считывание (потенциал О) запрещает формирование импульсов записи на одном из выходов и разрешает формирование синхроимпульса на другом выходе. С первого выхода блока 2 управления потенциал Считывание поступает на управляющий вход основной 1 и дополнительной 4 памяти. По коду адреса из блоков основной 1 и дополнительной 4 памяти считывается основная и избыточная информация.

g

5 0

5

JQзг

.

0

0

5

При отсутствии ошибок в разрядах основной 1 и дополнительной 4 памяти на всех трех входах мажоритарного элемента 6 будут одинаковые значения, равные значению выхода основной памяти 1 соответствующего разряда. Если при считывании из основной 1 или дополнительной 4 памяти появляется ошибка в одном из разрядов, то на двух из трех входах мажоритарного элемента 6 будет верное значение; при этом на его выходе 7, как и в случае отсутствия ошибки, будет значение, соответствующее истинному значению корректируемого разр яда информации основной 1 памяти.

Режим считывания с обнаружением однократных и двукратных ошибок.

При появлении однократных ошибок в разрядах основной 1 или дополнительной 4 памяти устройство производит не только их коррекцию, но и формирует сигнал ошибки с индикацией неисправности в блоке обнаружения ошибок. При появлении однократной ошибки на одном из трех входах одного мажоритарного элемента 6, сигнал отличается от сигналов на двух других входах этого же мажоритарного элемента (возникает неравнозначность), Поскольку входы мажоритарных элементов 6 соединены с соответствующими входами трехвходовых блоков 8 сравнения блока обнаружения, то на выходе одного из блоков 8 сравнения будет сигнал неравнозначности (лог. О). Следовательно, на выходе элемента И 9 также будет лог. О, который поступает на D-вход триггера 10 и с приходом импульса опроса из блока 2 управления на С-вход триггера 10 в него записывается сигнал ошибки. Одновременно загорается элемент 11 индикации ошибки.

При появлении двукратной ошибки в разрядах основной 1 и(или) дополнительной 4 памяти также происходит формирование сигнала Ошибка на выходе устройства с

Индикация ошибок.

При появлении одЛэкратных ошибок в блоках основной 1 или дополнительной 4 памяти на третьем входе мажоритарного элемента 6 соответствующего разряда блока исправления ошибок будет искаженная информация. На двух других входах мажоритарного элемента 6 будет информация, соответствующая

истинному значению этого разряда, в результате чего на выходе этого мажо- pHtapHoro элемента будет правильное (исправленное) значение данного раз-, ряда, В этом сл:, на входы соответствующего разряда дополнительных схем 12 сравнения поступают неравнозначные сигналы, что вызывает свечение соответствующего светодиода блока 14 индика- ции ошибок. Так, если, например, ошибка имеется в работе первого разряда блока 1 основной памяти, то на третьем входе мажоритарного элемента 6 первого разряда будет искаженная ин- формация, а на выходе мажоритарного элемента 6 (в результате исправляющих свойств сумматоров 5 и мажоритарного элемента 6) будет правильное значение Верное и неверное значения первого разряда поступают на входы первого разряда схем 12 сравнения и светодиод, подключенный к его выходу загораяется индицируя неисправность первого разряда блока 1 основной памяти .

ЕСЛИ неисправность возникла в блоке 4 дополнительной памяти, то ошибка будет индицироваться на одном из све- тодиодов, подключенных к выходам до- полнительных 13 сумматоров по модулю два. На каждый из сумматоров блока 13

информация заводится в соответствии с порождающей Н-матрицей,

Формула изобретения Запоминающее устройство с коррекцией однократных ошибок по авт.св. № 1137540, отличающееся тем, что, с целью функциональных возможностей устройства за счет обеспечения диагностики и локализации ошибок в н его введены дополнительные схмы сравнения по числу разрядов основного блока памяти, дополнительные сум по модулю два по числу разрядов дополнительного блока памяти и дополнительные элементы индикации по числу разрядов основного и дополнительного блока памяти, первые входы дополнительных схем сравнения соединены с соответствующими выходами основного блока памяти, выходы мажоритарных элементов соединены с вторыми входами соответствующих дополнительных схем сравнения, выходы основного и дополнительного блоков памяти соединены с соответствующими входами дополнительных сумматоров по модулю два, выходы дополнительных схем сравнения и сумматоров по модулю два соединены с соответствующими дополнительными элементами индикации.

фиг. t

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с коррекцией однократных ошибок | 1983 |

|

SU1137540A2 |

| Запоминающее устройство с коррекцией однократных ошибок | 1982 |

|

SU1073799A1 |

| Оперативное запоминающее устройство с коррекцией информации | 1984 |

|

SU1203364A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1983 |

|

SU1141453A1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1987 |

|

SU1481863A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Устройство для кодирования | 1985 |

|

SU1287294A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах. Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения диагностики и локализации ошибок. Устройство содержит основной блок памяти 1, блок 2 управления, блок 3 кодирования, дополнительный блок 4 памяти, блок 5 сумматоров по модулю два, мажоритарные элементы 6, имеющие выходы 7, блок 8 сравнения, элемент И 9, триггер 10, элемент 11 индикации, дополнительные схемы сравнения, дополнительные сумматоры по модулю два, элементы индикации. 2 ил.

| Запоминающее устройство с коррекцией однократных ошибок | 1983 |

|

SU1137540A2 |

Авторы

Даты

1989-12-23—Публикация

1987-05-11—Подача