со

СП

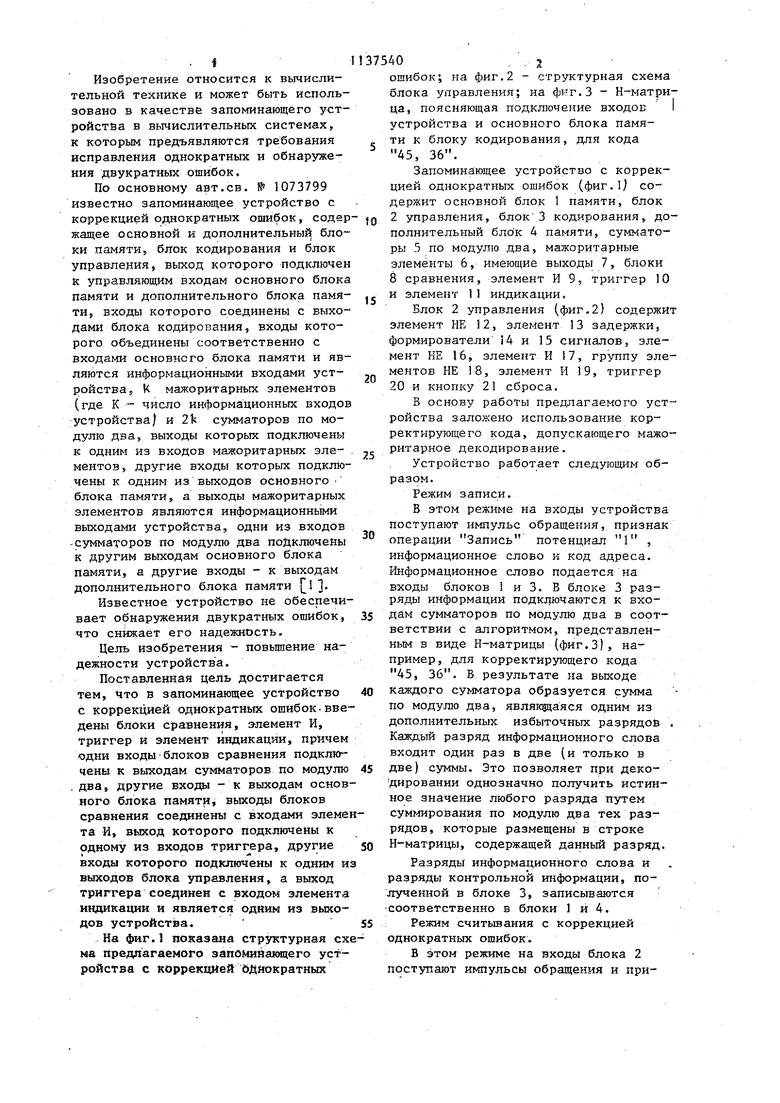

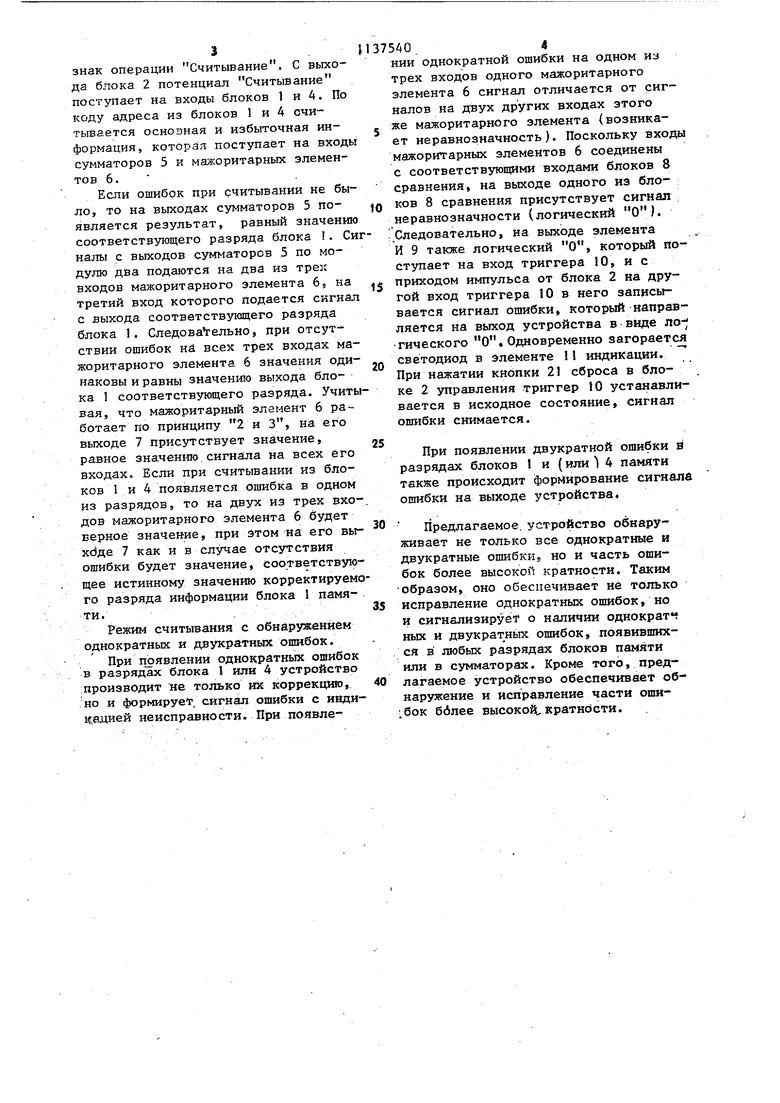

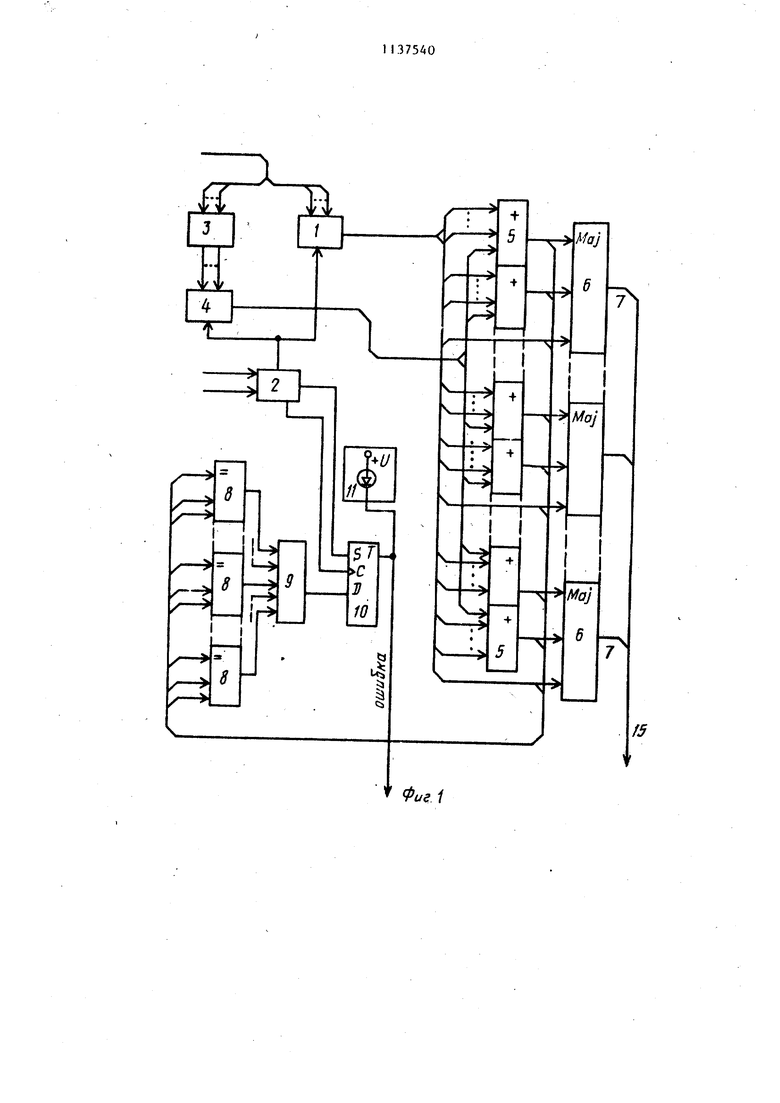

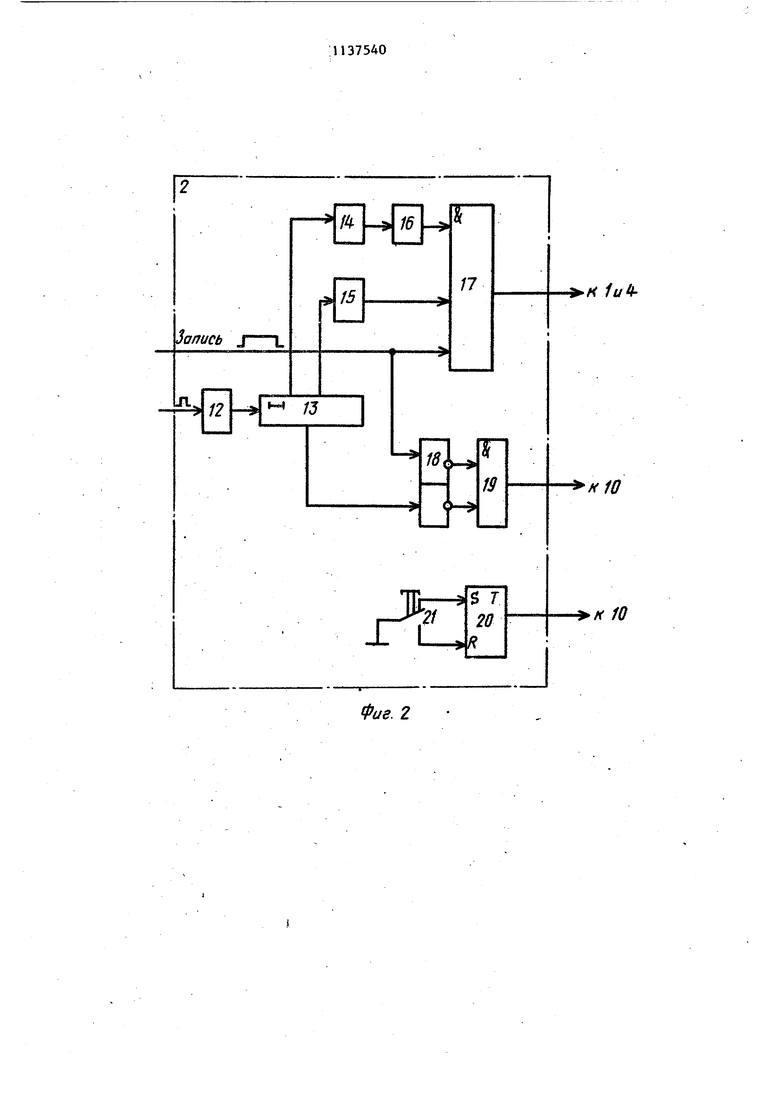

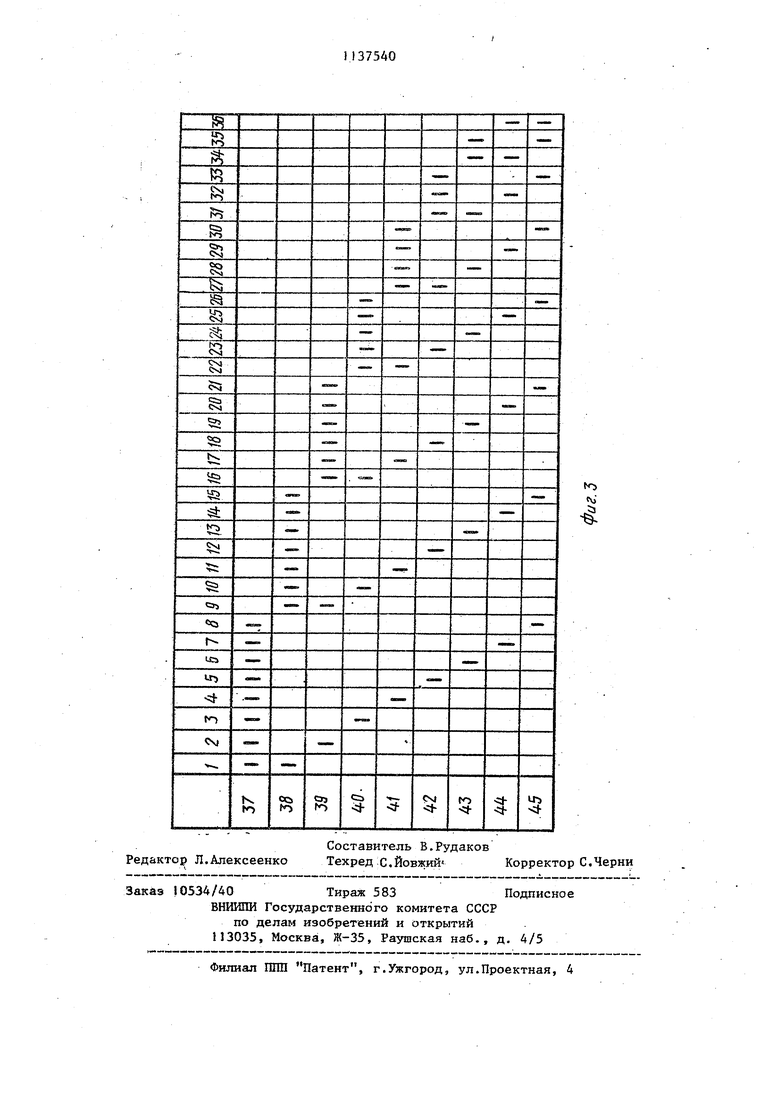

4 . I Изобретение относится к вычислительной технике и может быть использовано в качестве запоминающего устройства в вычислительных системах, к которым предъявляются требования исправления однократных и обнаружения двукратных ошибок. По основному авт.св. № 1073799 известно запоминающее устройство с коррекцией однократных ошибок, содер жащее основной и дополнительный блоки памяти, блок кодирования и блок управления, выход которого подключен к управляющим входам основного блока памяти и дополнительного блока памяти, входы которого соединены с выхо дами блока кодирования, входы которого объединены соответственно с входами основного блока памяти и являются информационными входами устройства s К мажоритарных элементов (где К - число информационных входов устройства) и 21с сумматоров по модулю два, выходы которых подключены к одним из Входов мажоритарных элементов S другие входы которых подключены к одним из выходов основного блока памяти, а выходы мажоритарных элементов являются информационными выходами устройства, одни из входов -сукЕматоров по модулю два подключены к другим выходам основного блока памяти, а другие входы - к выходам дополнительного блока памяти . Известное устройство не обеспечи вает обнаружения двукратных ошибок, что снижает его надежность. Цель изобретения - повышение надежности устройства. Поставленная цель достигается тем. Что в запоминающее устройство с коррекцией однократных ошибок-вве дены блоки сравнения, элемент И, триггер и элемент индикации, причем одни входы блоков сравнения подключены к выходам сумматоров по модулю . два, другие входа - к выходам основ ного блока памяти, выходы блоков сравнения соединены с входами элеме та И, выход которого подключены к одному из входов триггера, другие входы которого подключены к одним и выходов блока управления, а выход триггера соединен с входом элемента индикации и является одним из выходов устройст)ва. На фиг.1 показана структурная сх ма предлагаемого запоминающего устройства с коррекцией йДйократных 40. , 2 ошибок; на фиг.2 - структурная схема блока управления; на фиг.З - Н-матрица, поясняющая подключение входов I устройства и основного блока памяти к блоку кодирования, для кода 45, 36. Запоминающее устройство с коррекцией однократных ошибок (фиг.) содержит основной блок 1 памяти, блок 2 управления, блок3 кодирования, дополнительный блок 4 памяти, сумматоры 5 по модулю два, мажоритарные элементы 6, имеющие выходы 7, блоки 8 сравнения, элемент И 9, триггер 10 и элемент I1 индикации. Блок 2 управления (фиг.2) содержит элемент НЕ 2, элемент 13 задержки, формирователи 14 и 15 сигналов, элемент НЕ 16, элемент. И 17, группу элементов НЕ 18, элемент И 19, триггер 20 и кнопку 21 сброса. В основу работы предлагаемого устройства заложено использование корректирующего кода, допускающего мажоритарное декодирование. Устройство работает следующим образом. Режим записи. В этом режиме на входы устройства поступают импульс обращения, признак операции Запись потенциал 1 , информационное слово и код адреса, информационное слово подается на входы блоков 1 и 3. В блоке 3 разряды информации подключаются к входам сумматоров по модулю два в соответствии с алгоритмом, представленным в виде Н-матрицы (фиг.З), например, для корректирующего кода 45, 36. В результате на выходе каждого сумматора образуется сумма по модулю два, являкздаяся одним из дополнительных избыточных разрядов . Кажд;ый разряд информационного слова входит один раз в две (и только в две) суммы. Это позволяет при декодировании однозначно получить истинное значение любого разряда путем сум ирования по модулю два тех разрядов, которые размещены в строке Н-матрицы, содержащей данный разряд. Разряды информационного слова и разряды контрольной информации, поученной в блоке 3, записываются соответственно в блоки 1 и 4. Режим считьшания с коррекцией однократных ошибок. В этом режиме на входы блока 2 поступают импульсы обращения и признак операции Считывание , С выхода блока 2 потенциал Считывание поступает на входы блоков 1 и 4. По коду адреса из блоков 1 и 4 считывается основная и избыточная информация, которая поступает на входы сумматоров 5 и мажоритарных элементов 6. Если ошибок при считывании не было, то на выходах сумматоров 5 появляется результат, равный значению соответствующего разряда блока . Си налы с выходов сумматоров 5 по модулю два подаются на два из трех входов мажоритарного элемента 6, на третий вход которого подается сигнал с выхода соответствующего разряда блока 1. Следовагельно, при отсутствии ошибок ни всех трех входах мажоритарного элемента 6 значения одинаковы и равны значению выхода блока 1 соответствующего разряда. Учиты вая, что мажоритарный элемент 6 работает по принципу 2 и 3, на его выходе 7 присутствует значение, равное значению.сигнала на всех его входах. Если при считывании из блоков 1 и 4 появляется ошибка в одном из разрядов, то на двух из трех входов мажоритарного элемента 6 будет верное значение, при этом на его выхдде 7 как и в случае отсутствия ошибки будет значение, соответствующее истинному значению корректируемо го разряда информации блока 1 памяТИ. . ... Режим считывания с обнаружением однократных и двукратных ошибок. При появлении однократньпс ошибок в разрядах блока 1 или 4 устройство производит не только их коррекцию, но и формирует, сигнал ошибки с индиц;е,цией неисправности. При появле540.4 НИИ однократной ошибки на одном из трех входов одного мажоритарного элемента 6 сигнал отличается от сигналов на двух других входах этого же мажоритарного элемента (возникает неравнозначность). Поскольку входы мажоритарных элементов 6 соединены с соответствующими входами блоков 8 сравнения, на выходе одного И9 блоков 8 сравнения присутствует сигнал неравнозначности (логический О). Следовательно, на выходе элемента И 9 также логический О, который поступает на вход триггера 10, и с приходом импульса от блока 2 на другой вход триггера 10 в него записывается сигнал ошибки, который направляется на выход устройства в виде логического О, Одновременно загорается све:тодиод в элементе 11 индикации. При нажатии кнопки 21 сброса в блоке 2 управления триггер 10 устанавливается в исходное состояние, сигнал ошибки снимается. При появлении двукратной ошибки d разрядах блоков 1 и (или 4 памяти также происходит формирование сигнала ошибки на выходе устройства. Предлагаемое, устройство обнаруживает не только все однократные и двукратные ошибкиа но и часть ошибок более высокой кратности. Таким образом, оно обеспечивает не только исправление однократных ошибок, но и сигнализирует о наличии однократ ных и двукратных ошибок, появившихся в любых разрядах блоков памяти или в сумматорах. Кроме того, предлагаемое устройство обеспечивает обнаружение и исправление части ошибок бблее высоко: кратности.

/4

W

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с коррекцией однократных ошибок | 1987 |

|

SU1531174A1 |

| Запоминающее устройство с коррекцией однократных ошибок | 1982 |

|

SU1073799A1 |

| Устройство для кодирования | 1985 |

|

SU1287294A1 |

| Запоминающее устройство матричного типаС САМОКОНТРОлЕМ | 1979 |

|

SU849309A1 |

| Резервированное запоминающее устройство | 1989 |

|

SU1711237A1 |

| Запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1111205A1 |

| Оперативное запоминающее устройство с коррекцией ошибок по методу мажоритарного декодирования | 1986 |

|

SU1410105A1 |

| Запоминающее устройство с диагностированием ошибок | 1987 |

|

SU1644231A1 |

| Запоминающее устройство с коррекцией информации | 1982 |

|

SU1070610A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1539844A1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С КОРРЕКЦИЕЙ ОДНОКРАТНЫХ ОШИБОК по авт.св. № 1073799, отличающееся тем, что, с целью повышения надежности устройства, в него введены блоки сравнения, элемент И, триггер и элемент индикации, причем одни входы блоков сравнения подключены к выходам сумматоров по модулю два, другие входы - к выходам основного блока памяти, выходы блоков сравнения соединены с входами элемента И, выход которого подключен к одному из входов триггера, другие входы которого подключены к одлим из выходов блока управления, а выход триггера соединен с входом элемента индикации и является одним из выходов устройства. (Л с

15

Запись

л.

13

/2

/7

iuf

г

/

I5T f

10

J

. 2

o fb

i

| I. | |||

| Запоминающее устройство с коррекцией однократных ошибок | 1982 |

|

SU1073799A1 |

| Солесос | 1922 |

|

SU29A1 |

Авторы

Даты

1985-01-30—Публикация

1983-06-29—Подача