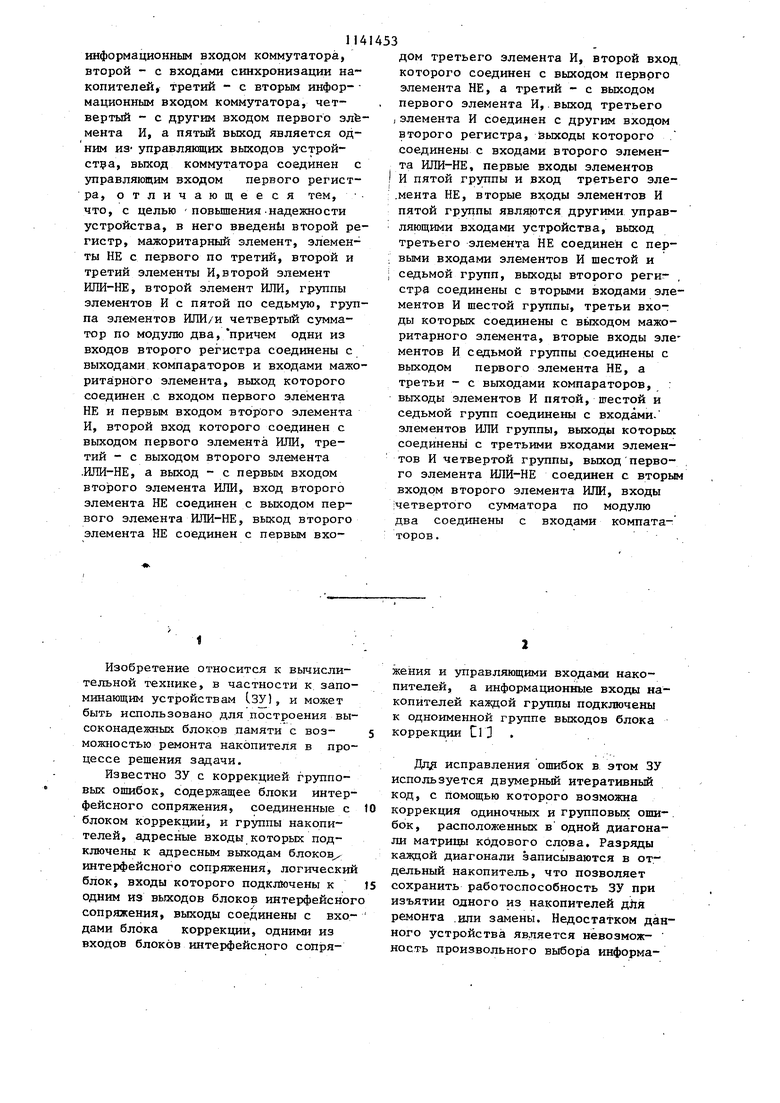

информационным входом коммутатора, второй - с входами синхронизации накопителей, третий - с вторым информационным входом коммутатора, четвертый - с другим входом первого элЬ мента И, а пятый выход является одним из- управляющих выходов устройств а, выход коммутатора соединен с управляющим входом первого регистра, отличающееся тем, что, с целью повышения-надежности устройства, в него введен второй ре гистр, мажоритарный элемент, элементы НЕ с первого по третий, второй и третий элементы И,второй элемент ИЛИ-НЕ, второй элемент ИЛИ, группы элементов И с пятой по седьмую, груп па элементов ИЛИ/и четвертый сумматор по модулю два, причем одни из входов второго регистра соединены с выходами компараторов и входами мажо ритарного элемента, выход которого соединен с входом первого элемента НЕ и первым входом второго элемента И, второй вход которого соединен с выходом первого элемента ИЛИ, третий - с выходом второго элемента .ИЛИ-НЕ, а выход - с первым входом второго элемента ИЛИ, вход второго элемента НЕ соединен с выходом первого элемента ИЛИ-НЕ, вькод второго элемента НЕ соединен с первым вхо11дом третьего элемента И, второй вход которого соединен с выходом первого элемента НЕ, а третий - с выходом первого элемента И,.выход третьего элемента И соединен с другим входом второго регистра, выходы которого соединены с входами второго элемента ИЛИ-НЕ, первые входы элементов И пятой группы и вход третьего элемента НЕ, вторые входы элементов И пятой группы являются другими управляющими входами устройства, выход третьего элемента НЕ соединен с первыми входами элементов И шестой и седьмой групп, выходы второго региг , стра соединены с вторыми входами элементов И шестой группы, третьи входы которых соединены с вьпсодом мажоритарного элемента, вторые входы элементов И седьмой группы соединены с выходом первого элемента НЕ, а третьи - с выходами компараторов, : выходы элементов И пятой, шестой и седьмой групп соединены с входамиэлементов ИЛИ группы, выходы которых соединены с третьими входами элементов И четвертой группы, выход первого элемента ИЛИ-НЕ соединен с вторым входом второго элемента ИЛИ, входы четвертого cyMMatopa по модулю два соединены с входами компататоров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с коррекцией групповых ошибок | 1983 |

|

SU1092570A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1061176A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1991 |

|

SU1837364A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1987 |

|

SU1481863A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1984 |

|

SU1215139A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| Полупроводниковое оперативное запоминающее устройство с коррекцией информации | 1990 |

|

SU1795520A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР | 2009 |

|

RU2417409C2 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С КОРРЕКЦИЕЙ ГРУППОВЫХ ОШИБОК, содержащее накопители, элемент задерж-. ки, коммутатор, первьй элемент И, элементы НЕРАВНОЗНАЧНОСТЬ, neps-jTo группу элементов И и блок коррекции, содержащий первый регистр, первую и вторую группы сумматоров по модулю два, группы элементов И с второй по четвертую, сумматоры по модулю два с первого по третий, компараторы, первый элемент ИЛИ и первый элемент ИПИ-НЕ, причем информационные выходы первого регистра соединены с информационными входами накопителей, информационные выходы первого регистра соединены с одними из входов сумма- торов по модулю два групп, другие входы поключены к выходам тов И второй группы, первые входы которых и входы первого и второго сумматоров по модулю два соединены с контрольными выходами первого регистра, контрольные входы которого подключены к выходам элементов И третьей группы и контрольным выходам накопителей, первые входы одних из элементов И третьей группы соединены с выходами сумматоров по модулю два групп/ первый вход другого элемента И третьей группы соединен с выходом третьего сумматора j по модулю два, входы которого поклю чены к выходам сумматоров по модупю два первой группы, вторые входы элементов И второй группы соединены с .входами признака считывания накопителей, с управляющим входом коммутатора и одним, из входов первого элемента И, вторые входы элементов И-Третьей группы соединены с- входами признака записи накопителей,одни из входов компараторов, первые входы элементов И четвертой группы и одни из входов первого элемента ИЛИ соединены соответственно с выходами ,сумматоров по модулю два первой группы и с выходом первого сз мматора по модулю два, выходы сумматоров по модулю два второй группы и выход второго сумматора по модулю два подключены к вторым входам элементов И четвертой группы, другим входам первого элемента ИЛИ и другим входам компараторов, выходы которы: соединены с входами первого элемента ИЛИНЕ, выходы элементов И четвертой группы соединены с первыми входами элементов НЕРАВНОЗНАЧНОСТЬ, вторые сд входы которых соединены с информаО9 ционными выходами накопителей и являются информационными входами устгГ) ройства, выход первого элемента И соединен с первыми входами элементов И первой группы, вторые входы которых соединены с выходами элементов НЕРАВНОЗНАЧНОСТЬ, а выходы являются инфорг мационными выходами устройства, вход элемента задержкиявляется входом запуска устройства, первый выход элемента задержки соединен с первым

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам СЗУ), и может быть использовано для построения высоконадежных блоков памяти с возможностью ремонта накопителя в процессе решения задачи.

Известно ЗУ с коррекцией групповых ошибок, содержащее блоки интерфейсного сопряжения, соединенные с блоком коррекций, и группы накопителей, адресные входы которых подключены к адресным выходам блоков/ интерфейсного сопряжения, логический блок, входы которого подключены к одним из выходов блоков интерфейсног сопряжения, выходы соединены с входами блока коррекции, одними из входов блоков интерфейсного сопряжения и управляющими входами накопителей, а информационные входы накопителей каждой группы подключены к одноименной группе выходов блока коррекции СгЗ .

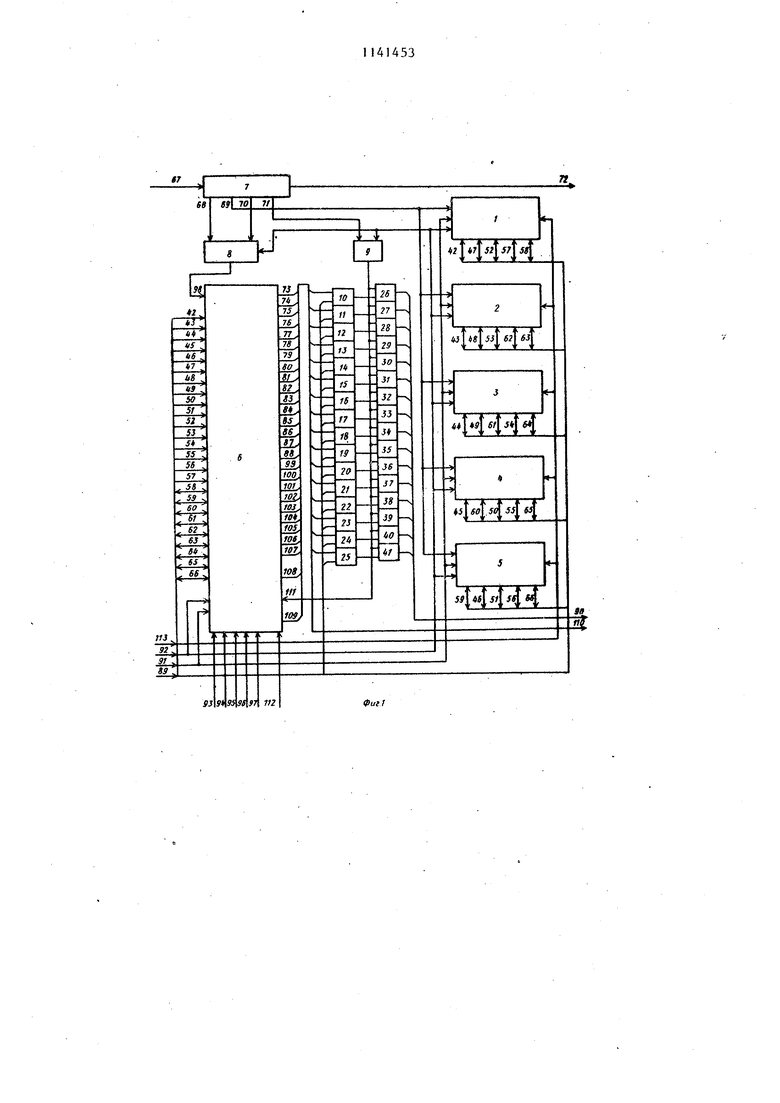

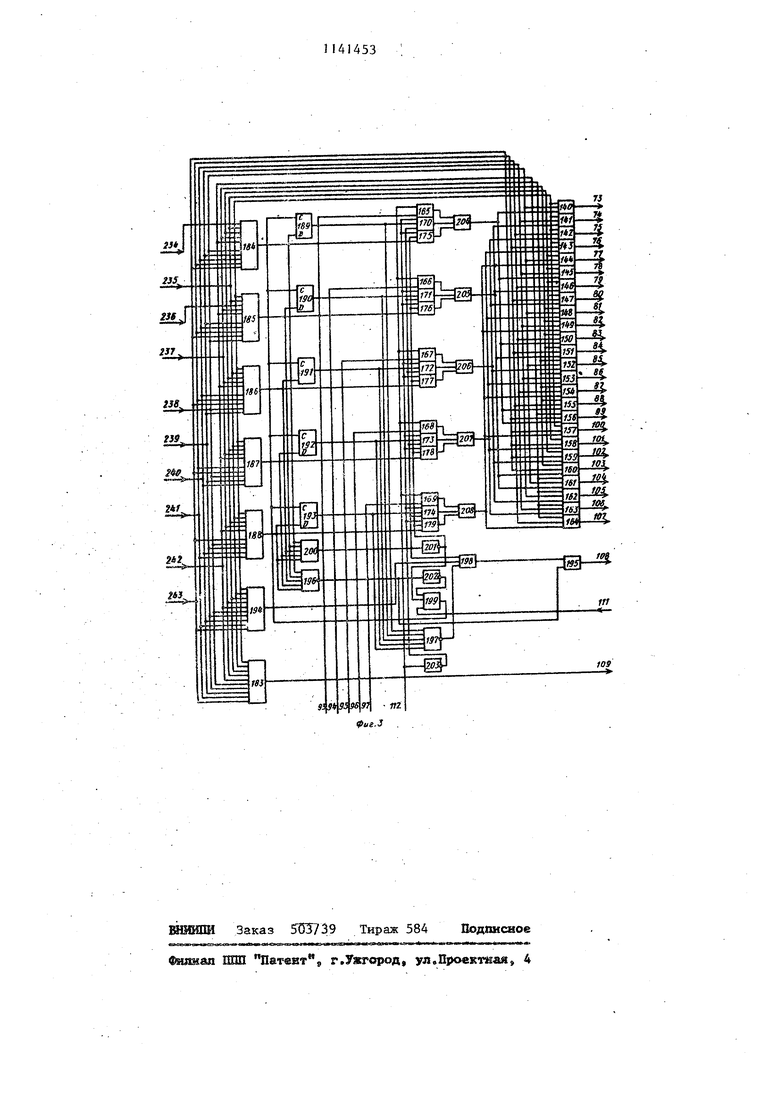

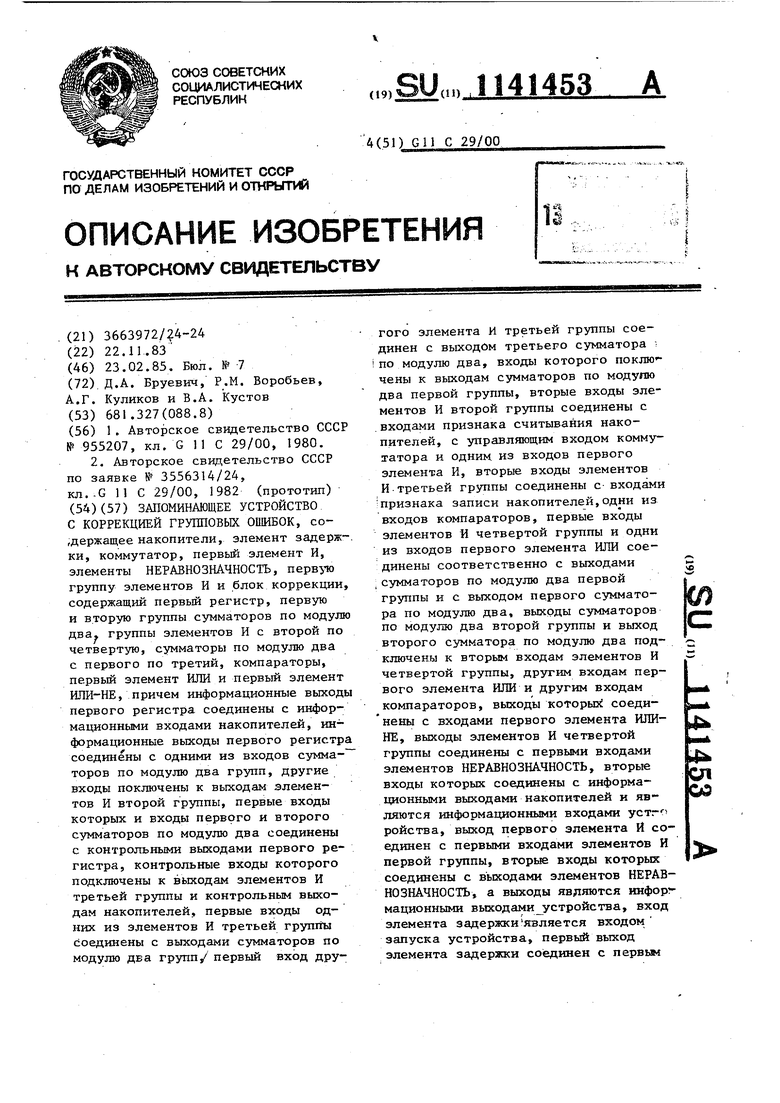

Дгу исправления ошибок в этом ЗУ используется двз мерньй итеративный код, с помощью которого возможна коррекция одиночных и групповых ошибок, расположенных в одной диагонали матрицы кодового слова. Разряды каждой диагонали записываются в отдельный накопитель, что позволяет сохранить работоспособность ЗУ при изъятии одного из накопителей дйя ремонта .или замены. Недостатком данного устройства является невозмож- ность произвольного выбора информа3цнонной емкости ЗУ из-за ее зависимости от длины кодового слова большого числа накопителей. . Наиболее близким техническим решением к изобретению является ЗУ с коррекцией групповьсх ошибок, содер жащее накопители, блок коррекции, элемент задержки, коммутатор, элемент И, элемента НЕРАВНОЗНАЧНОСТЬ, и группу элементов И, причем информ ционные и контрольные выходы накопителей соединены соответственно с информационными и контрольными входами блока коррекции, входы синхро низации накопителей подключены к первому выходу элемента задержки, второй выход и чход которого являются соответственно управляющим выходом и входом запуска устройства, первый и второй входы коммутатора соединены соответственно с третьим и четвертым выходами элемента задержки, пятый выход которого соеди нен с первым входом элемента И, одни из выходов блока коррекции под ключены к первым входа:м соответству ющих элементов НЕРАВНОЗНАЧНОСТЬ, вторые входы которых соединены с информационными выходами накопителе выход первого элемента И подключен к первым входам элементов И груп пы, вторые входы которых соединены с выходами элементов НЕРАВНОЗНАЧНОСТЬ, а выходы являются информационными выходами устройства, управляющий вход блока коррекции подключен к выходу коммутатора, а другие выходы блока коррекции являются контрольными выходами устройства. 2 В режиме Запись слово данных поступает на вход блока коррекции, который формирует контрольные разряды двумерного итеративного кода,, после чего сформированное кодовое слово записывается в накопитель.. В режиме Чтение считанное кодовое слово поступает в блок коррекции, который определяет наличие ошибки в одном из накопителей и выдает позиции ошибок неверно считанных разрядов. Исправление ошибок происходит на элементах НЕРАВНО- ЗНАЧНОСТЬ. Затем через группу элементов И исправленное слово данных поступает на выход устройства. Недостаток устройства заключается в том, что оно не в состоянии обнаружить и скорректировать ошибку, которая возникает при полном 53 выходе из строя одного из накопителей, что приводит к снижению надежности ЗУ. Цель изобретения - повьш1ение надежности устройства., Указанная цель достигается тем, что в ЗУ с коррекцией групповых ошибок, содержащее накопители, элемент задержки,первый элемент И, элементы НЕРАВНОЗНАЧНОСТЬ, первую. группу элементов И и блок коррекции, содержащий первый регистр, первую и вторую группы сумматоров по модулю два, группы элементов И с второй по четвертую, сумматоры по модулю два с первого по третий, компарато-. первый-элемент ИЛИ и первый элеры, мент ИЛИ-НЕ, причем информационные входы первого регистра соединены с информационными входами накопителе, информационные выходы первого регистра соединены с одними из входов сумматоров по модулю два групп, другие входы подключены к выходам элементов И второй группы, первые входы которых и входы первого и второго сумматоров по модулю два соединены с контрольными выходами первого регистра, контрольные входы которогб подключены к выходам элементов И третьей группы и контрольным выходам накопителей, первые входы одних из элементов И третьей группы соединены с выходами сумматоров по модулю два групп, первый вход другого элемента И третьей группы соединен с выходом третьего сумматора по модулю два, входы которого подключены к выходам сумматоров по модулю два первой группы, вторые входы элементов И второй группы соединены с входами признака считывания накопителей, с управляющим входом коммутатора и одним из входов первого элемента И, вторые входы элементов И третьей группы соединены с входами признака записи накопителей, одни из входов компараторов, первые входы элементов И четвертой группы и одни из входов первого элемента ИЛИ соединены соответственно с выходами сумматоров по модулю два первой группы и с выходом первого сумматора по модулю два,- выходы сумматоров по модулю два второй группы и выход второго сумматора по модулю два подключены к вторым входам элементов И четвертой группы, другим входам первого элемента ИЛИ и другим вхо1дам компараторов, выходы которых соединены с входами первого элемент ИЛИ-НЕ, выходы элементов И четвертой группы соединены с первыми входами элементов НЕРАВНОЗНАЧНОСТЬ, вторые входы которык соединены с ин формационными выходами накопителей и являются информационными входами устройства, выход первого элемента соединен с первьши входами элементов И первой группы, вторые входы которых соединены с соответствующи ми выходами элементов НЕРАВНОЗНАЧНОСТЬ, а выходы являются информационными выходами устройства, вход элемента задержки является входом запуска устройства, первый выход элемента задержки соединен с первым информационным входом коммутатора, второй - с входами синхронизации накопителей, третий - с вторым инфо мационным входом коммутатора, четвертый - с другим входом первого элемента И, а пятый вьгход является одним из управляющих выходов, устрой ства, выход коммутатора соединен с управляющим входом первого регистра введены-Второй регистр, мажоритарный элемент, элементы НЕ с первого, по третий, второй и третий элементы И,, второй: элемент ИЛИ-НЕ, второй элемент ИЛИ, группы элементов И с пятой по седьмую, группа элементов ИЛИ и четвертый сумматор по модулю два, причем одни из входов второго регистра соединены с выходами компараторов и входами мажоритарного элемента;, выход которого соединен с входом первого элемента НЕ и первым входом второго элемента И, второй вход которого соединен с выходом первого элемента ИЛИ, третий - с выходом второго элемента ИЛИ-НЕ, а выход с первым входом второго элемента ИЛИ, вход второго элемента НЕ соединен с выходом первого элемента ИЛИ-НЕ, выход второго элемент НЕ соединен с первым входом третьего элемента И, второй вход которог соединен с выходом первого элемента НЕ, а третий - с выходом первого элемента И, выход третьего элемента И соединен с другим входом второго регистра, выходы которого соединены с соответствующими входами второго элемента ИЛИ-НЕ, первые входы элементов И пятой группы и вход третьегб элемента НЕ, вторые входы эле36ментов И пятой группы являются другими управляющими входами устройства, выход третьего элемента НЕ сое|динен с первыми входами элементов И шестой и седьмой групп, выходы второго регистра соединены с вторьми входами элементов И шестой группы, третьи входы которых соединены с выходом мажоритарного элемента, вторые входы элементов И седьмой группы соединены с выходом первого элемента НЕ, а третьи.- с выходами компараторов, выходы элементов И пятой, шестой и седьмой групп соединены с входами элементов ИЛИ группы, выходы которых соединены с третьими входами элементов И четвертой группы, выход первого элемента ИЛИ-НЕ соединен с вторым входом второго элемента ИЛИ, входы четвертого сумматора по модулю два соединены с входами компараторов. На фиг.1 представлена функциональная схема предлагаемого ЗУ с коррекцией групповых ошибок; на фиг.2 и 3функциональная схема блока коррекции. Устройство содержит (фиг. I) накопители 1-5, блок 6 коррекции, элемент 7 задерлски, коммутатор 8, первый элемент И 9, элементы НЕРАВНОЗНАЧНОСТЬ 10-25, первую группу элементов И 26-41, причем информационные 42-57 и контрольные 58-66 выходы накопителей 1-5 соединены соответственно с информационными и контрольными входами блока 6 коррекции, вход элемента 7 задержки является входом 67 запуска устройства, первый выход 68 элемента 7 задержки сог единен с первым входом коммутатора 8, второй 69 - с входами синхронизации накопителей 1-5, третий 70 - с вторым входом коммутатора 8, четвертый 71 - с первым входом первого элемента И 9, а пятый 72 является управ51яющим выходом устройства, выходы 73-88 блока 6 коррекции соединены с первыми входами элементов НЕРАВНОЗНАЧНОСТЬ 10-25, вторые входы которых соединены с информационными выходами 42-57 накопителей 1-5 и являются информационными входами 89 устройства, выход первого элемента и 9 соединен с первыми входами элементов И 26-41 первой группы, вторые входы которых соединены с соответствующими выходами элементов НЕРАВНОЗНАЧНОСТЬ 10-25, а вьпсоды являются информационными выходами 90 устройства, входы признака записи накопителей 1-5 соединены с входом i признака записи блока 6 коррекции и являются входом 91 записи устройства, входы признака считьшания накопителей 1-5 и блока 6 коррекции объединены с управляющим входом коммзтатора 8 и вторым входом первого элемента И 9 и являются входом 92 считьшания устройства, установочными входами 93-97 которого явля ются установочные входы блока 6 коррекции, вьпсод коммутатора 8 соединен с управляющим входом 98 блока 9 коррекции, выходы 73-88 информационных и 99-107 контрольных разрядов, выход 108 признака некорректируемой ошибки и выход 109 признака отказа блока 9 коррекции являются контрольными выходами 11 О устройства, выход первого элемента И 9 соединен с входом 111 синхронизации блока 9 коррекции, вход признак установки которого является входом 112 замены накопителя устройства, адресные входы накопителей являются адресным входом 113 устройства. Блок 6 коррекции содержит (фиг.2 и 3) первый регистр 114, первую группу сумматоров 115-118 по модулю два, вторую группу сумматоров 119122 по модулю два, с второй по седь мую группы элементов И 123-130, 131-139, 140-164, 165-169, 170-174 и 175-179 соответственно, первый 180 второй 181, третий 182 и четвертый 183 сумматоры по модулю два, компараторы 184-188, второй регистр вьшолненный на D-триггерах 189-193 первый 194 и второй 195 элементы ИЛИ, первый 196 и второй 197 элемен ты ИЛИ-НЕ, второй 198 и третий 199 элементы И, мажоритарный элемент 20 первый 201, второй 202 и третий 203 элементы НЕ и группу элементов ИЛИ 204-208, Регистр 114 имеет инфо мационные 209-224 и контрольные 225 233 выходы. Сумматоры 115-122, 180 и 181 по модулю два имеют выходы 234-243. Устройство работает следующим об разом. В устройстве для коррекции одиночных и групповых ошибок используется двумерный итеративный код, мат рица кодового слова которого для числа информационных разрядов, равного в данном примере шестнадцати, имеет вид: - информационные разряды; & - контрольный разряд общей четности; С 4 -1 4 контрольные разряды соответственно групповой и веточной четности. В исходном состоянии регистры 114 и триггеры 189193 обнулены, а на вход 112 подается низкий уровень напряжения. В режиме Запись на вход 113 устройства поступает адрес выбранной ячейки накопителя, на вход 89 - слово данных S , на вход 91 - признак записи, а на вход 67 - сигнал Запуск. Появившись на выходе 68 элемента 7 задержки, сигнал Запуск через коммутатор 8 проходит на вход 98 блока 6, где заносит в регистр 114 информацию, находящуюся на входах 42-57. После этого в блоке 6 начинается формирование контрольных разрядов по формулам 1Ь Контрольные разряды групповой етности С - С формируются с по-. ощью сумматоров 115-118.по модулю ва, а контрольные разряды веточной етности d - с помощью сумматоов 119-122 по модулю два. Контрольый разряд общей четности 6 формиуется с помощью сумматоро-в 115-118 о модулю два и с помощью суммато-. а 182 по модулю два. На входе 92 лока 6 присутствует логический нуль (низкий уровень напряжения), а на ходе 91 - логическая единица (выокий уровень напряжения). В резульате элементы И 123-130 остаются акрытыми и на их выходах находятся огические нули, а элементы И 13139 открываются и сформированные коптрольные разряды поступают с их выходов на входы 58-66 блока 6 и нако пителей 1-5. С появлением сигнала на выходе 69 элемента 7 задержки производится запись кодового слова в накопители 1-5, причем разряды S , ,S(, S , S , с . записьюаются в накопитель 1, разрады S S,., С, d - в накопитель 2, разряды bj, bj, 1.3, копитель 3, разряды о , v.j s S,, , d - в накопитель 4, а разряН / S.., S.,. , . d - в накоды с,,, oj- 10 ts 5. По окончании записи на выход 72 устройства вьщается сигнал Ответ. ., В режиме Чтенце на .вход 113 устройства поступает адрес выбранно ячейки, на вход 92 - признак считывания, а на вход 67 - сигнал Запуск. С появлением сигнала на выходе 69 элемента 7. задержки кодово слово считывается из накопителей 1и поступает на входы блока 6. Так как на управляющем входе коммутатора 8 присутствует логическая единица, поступакнцая с входа 92 устрой ства, то прохождение сигнала через коммутатор с выхода 68 элемента 7 задержки запрещается. Одновременно разрешается прохождение сигнала с выхода 70, поступающего позже сигнала с выхода 69 с задержкой, равной времени выборки информации из накопителей 5. Пройдя коммутатор этот сигнал nocTynaieT на управляющий вход 98 блока 6 и заносит счдтанное кодовое слово в регистр 114.

184 oi об d. 5 185 . о., d d oL d

186 ct, d d, c,. oi

Э т 5

4-Й компаратор 187 d, d, d. d

5-Й компаратор 188 d d.. d

1 z Э 4 1

f.

4

oi. 10 Затем в блоке 6 начинается формирование синдрома ошибки с помощью .сумматоров 115-122, 180 и 181 по модулю два. Так как на входе 92 признака считывания блока 6 присутствует логическая единица, то считанные значения контрольных разрядов ., d4 с выходов 225-233 регист-ра 114 через элементы И 123-130 поступают на входы сумматоров 115-122 по модулю два и логическое состояние их выходов 234-241 определяется формулами соответственно. Состояние выходов 242 и 243 сумматоров 180-181 определяется как/ t d +d, + dj + d, d, + + с„ + с., С. -1 2 соответственно. В дальнейшем разряды синдрома ошибки 6i, Ъ 4 и 5- сравниваются между собой .с помощью компараторов 184-188, причем, компаратор 184 сравнивает одfli oCj (ij и ноименные разряды /J /i /ff остальные компараторы сравнивают разряды cL d d- oCg с. циклически сдвинутыми разрядами /ij Л j 4 COOTветстврш с таблицей.

111141453

При совпаденииинформации на первом-пятом входах с информацией на шестом-десятом входах какого-либо из компараторов состояние его выхода принимает значение логической г %1 . 2; где g. - логическое состояние выхода i-го элемента ИЛИ 204-208. Поэтому при отсутствии опшбки ( все разряды синдрома равны нулю ) на выходах всех компараторов присутствуют высокие уровни напряжения рдйако на выходах 73-107 элементов И 140-164 сохраняются логические ну ли. В этом случае считанные из нако пителя информационные разряды кодового слова проходят через элементы НЕРАВНОЗНАЧНОСТЬ 10-25 без изменения, а затем по сигналу с выхода 7 элемента 7 задержки, проходящему че рез элемент И 9, вьщаются на выходы 90 устройства. Затем на выход 72 поступает сигнал Ответ. Рассмотрим теперь случай неправильного считывания данных. При это предполагается, что неисправность имеет место только в одном из накопителей 1-5.. Пусть, например, в накопители 1- было записано кодовое слово При считывании в результате выхо да из строя разрядов Sj S и d2 в накопителе 3 в регистр поступает следующее кодовое слово: Тогда сумматорами 115-122,180 по модулю два формируется син ром ошибки

12

единицы. Позиции ошибок (неисправные разряды) определяются с помощью элементов И 140-164 при совпадении единичных значений , /5, -/ij. и g g в соответствии с формулами Ч. . «SfS 4/i4 ;«с 4 5 2 «с( ot 1 + 1+0+1+0 1 оСг 1 + 1 + 1+0+0 I (5 0+0+1+0+0 1 Согласно таблице только на выходе компаратора I86 появляется логическая единица, а на выходах остальных компараторов сохраняется логический ноль. На выходе мажоритарного элемента 200 появляется логическая единица только при наличии двух и более единиц на его входах, поэтому в данном случае на его выходе сохраняется низкий уровень напряжения, а на выходе элемента НЕ 201 - высокий. На первых входах элементов И 175-179 также присутствует высокий уровень напряжения, с ввкода элемента НЕ 203, следовательно, вы-, ходы этих элементов повторяют логическое состояние выходов компараторов 184-188. То же логическое соетояние будет к на выходах элементов ИЛИ 204-208, поскольку элементы И 165-174 остаются закрытыми, т.е. на выходе элемента ИЛИ 206 появляется высокий уровень напряжения, а на выходах остальных элементов ИЛИ этой же группы - низкие ( g О, &, О. 8. gi О, g- О). В результате элементы И 140-164 формируют следующие значения позиций ошибок:

SH ОI

0

513 ecJj I

о nМ

Таким образом, на элементах НЕРАВНО ЗНАТНОСТЬ 12 и 17 происходит инверсия третьего и восьмого разряда, а по состоянию контрольных выходов ПО можно определить, что ошибка произошла в разрядах S Sg , Cj и d . Сигнал с выхода s мента И 9 вьщает исправленное слово на выход 90 и одновременно поступает на вход I1 блока 6, где стробирует элемент И 199. На остальных входах данного элемента в эт мент присутствуют лоп-гческие единиць, он открывается, и на вхо, геров 189-193 ньщается сигнал,, записывающий в них информацию, находя-. Е1;уюся на выходах компараторов 184188, Это означает; что в регистре 189-193 происходит запоминание номера отказавшегося накопителя.

Предположим теперь, что в третье накопителе отказал последний разт.е. накопитель 3 полностью

ряд S.

13

вьппел из строя о Если отказ в разрядах S 5 Sg S S,, есть закрепление нуля., а в разрядах Cjjdj - закрепление единицы, то в регистр 114 поступает следующее кодовое слово:

11010

1 1 1 00

S7

S.1

1

5Н ° S15 05 Ч

На элементах НЕРАВНОЗНАЧНОСТЬ 12, 17 .и 22 происходит инверсия третьего, восьмого и тринадцатого разрядов, а состояние выхода указывает на .полный выход из строя накопителя 3. Так как на выходе элемента НЕ 201 присутствует низкий уровень напряжеВ результате на выходах всех компараторов 184-188 и на выходе мажоритарного элемента 200 появляется логическая единица. Элементы И 175179 закрываются и открываются элементы И 170-174, которые пропускают на. .выходы элементов ИЛИ 204-208 информацию, записанную в триггерах 189193. Следовательно, на выходе элемента ИЛИ 206 появляется логическая единица, а на выходах элементов ИЛИ

204 - 208 логические нули (

8, 0, 82 О, 8з

. I §4 О. §5 О ).

Элементы И 140-164 формируют следующие значения позиций ошибок:

0; oj

кия, поступающий на вход элемента И 199, то новая запись данных в триггеры 189-193 по сигналу с выхода элемента И 9 не происходит.

Способность устройства корректировать все разряды, считанные с одного из накопителей, дает возможность защититься от таких его отказов, как выход из строя формирователей синхронизирующих и адресных сигналов, замыкания адресных шин, неисправностей системы питания и т.п. Здесь возможны два случая дальнейшей работы устройства. В первом из них, при первом чтении после возникновения отказа данного вида в одном из накопителей не все пять-разрядов считываются из него неверно например, если в накопитель 3 ранее были записаны разряды S 1, S. О, Сз I, 5„ 1, d. 1, а отказ привел к постоянному считываниш и накопителя нулей, то в разряде 5g ошибка отсутствует . Тогда в триггеры 189-193 записьшается номер отказавшего накопителя, и в дальнейшем устройство работает аналогично описанному выше. Вероятность такого события равны 31 Во втором случае при первом чтении все разряды считываются неверно. Есл предположить, что до этого момента отказов в накопителе не бьто и в триггерах 189-193 записаны нули, то коррекции не происходит. Одновременно на всех трех входах элемента И198 оказьшаются высокие уровни напряжения и логическая единица с его выхода через элемент ИЛИ 195 поступает на выход 108 блока 6 и на выход 110 устройства как признак некорректиру емой ошибки (НКО ). При возникновении такого события, вероятность которого 1 необходимо обратиться в режим чтения к другой ячейке накопителя, а затем провести повторное считывание по нужному адресу. При замене накопителя вероятность вьщачи признака НКО в описанном случае можно свести К нулю,-с этой целью на один из входов 93-97 устройства, номер которого соответствуе номеру заменяемого накопителя, следует подать высокий уровень напряжения (например, на вход 95 при замене накопителя 3), а на остальные низкий. После этого на вход 112 замены накопителя подается логическая единица. Элементы И 170-179 закрываются и открьшаются элементы И 165169, определяя тем самым разряды, которые неправильно считываются вследствие изъятия из состава устрой ства соответствующего накопителя. Тем самым исключается возможность невыполнения коррекции при первом чтении. После замены накопителя подача логической единицы на вход 112 прекращается. Признак НКО вьщается также при обнаружении ошибки в разных накопителях. Пусть, например, ошибка происходит в разрядах 5 и 5 Тогда синдром ошибки примет вид ) оСз 0; odj-O( р, 0; , /, . Так как ни на одном из выходов компараторов 184-188 не оказывается логической единицы, то на выходе элемента РШИ-НЕ 196 появляется высокий уровень напряжения, который через элемент ИЛИ 195 поступает на выход устройства как признак НКО. . Четвертый сумматор 183 по модулю два предназначен для обнаружения ошибок в самом блоке коррекции. Появление логической единицы на его выходе 109 означает, что вьщача признака НКО вызвана не ошибкой в накопителях 1-5, а отказом в цепях формирования синдрома блока 6 коррекции. В целом информация на контрольном выходе 110 устройства, включающая позиции ошибок кодового слова, признак некорректируемой ошибки и признак отказа блока коррекции, может быть использована для индикации отказавших разрядов и ускорения поиска неисправностей в отдельных блоках устройства. Преимущество предлагаемого технического решения по сравнению с известным заключается в более высокой надежности, так как оно способно корректировать ошибки одного из накопителей независимо от их кратности. причем эти ошибки могут быть выэваны отказами как запоминающих микросхем, так и элементов электроники обрамления, Кроме того, устройство способно обнаружить отказы в блоке коррекции.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающее устройство с исправлением ошибок | 1980 |

|

SU955207A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 3556314/24, кл.-С 11 С 29/00, 1982 (прототип) | |||

Авторы

Даты

1985-02-23—Публикация

1983-11-22—Подача