1

(21)4431294/24-21

(22)30.05.88

(46) 23.12.89. Бкш. 47

(72) В.Ш.Арутюнян и А.К.Аракелян (53) 621.3.019.35 (088.8) (56) Абугов Ю.О., Диденко К.И«, Загарий Г.И. и др. Микроэлектронные устройства программного и логического управления. - М.: Машиностроение, 1979, с. 41, рис. 216.

Авторское свидетельство СССР № 1448406, кл. Н 03 К 29/33, 16.11.87 (54) МАЖОРИТАРНЫЙ ЭЛЕМЕНТ 4 ИЛИ БОЛЕЕ ИЗ 7 (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения различных устройств переработки дискретной.информации. Цель изобретения - повьшение надежности за счет использования более простых коммутаторов со структурой 1 из 4. Мажоритарный элемент содержит три коммутатора 1 из 4, семь входов задания переменных, элемент 3 И, мажоритарный элемент 2 или более из 3, два элемента 3 ИЛИ, элемент 2 ШШ, элемент ИСКЛЮЧАЮЩЕЕ ШШ с инверсным выходом, элемент 2 И-НЕ, втны нулевого и единичного логических сигналов. 1 ил.

г

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Мажоритарный элемент | 1987 |

|

SU1448406A1 |

| Мажоритарный элемент | 1987 |

|

SU1499487A1 |

| Мажоритарный элемент | 1988 |

|

SU1538249A1 |

| Реверсивный счетчик | 1983 |

|

SU1145477A1 |

| Устройство для контроля управляющих сигналов интерфейса | 1984 |

|

SU1215111A1 |

| Пороговое логическое устройство | 1987 |

|

SU1422400A1 |

| Устройство для кодирования | 1985 |

|

SU1287294A1 |

| Мажоритарный элемент | 1990 |

|

SU1750052A1 |

| Многофункциональный триггер | 1983 |

|

SU1132341A1 |

| Устройство для отладки тестов | 1982 |

|

SU1084804A2 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения различных устройств переработки дискретной информации. Цель изобретения - повышение надежности за счет использования более простых коммутаторов со структурой "1 из 4". Мажоритарный элемент содержит три коммутатора "1 из 4", семь входов задания переменных, элемент 3 И, мажоритарный элемент "2 или более из 3", два элемента 3 ИЛИ, элемент 2 ИЛИ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ с инверсным выходом, элемент 2И-НЕ, шины нулевого и единичного логических сигналов. 1 ил.

« f

6 7

Ml IfX)

Ш

Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения различных устройств переработки дискретной информации.

Цель изобретения - повышение надежности.

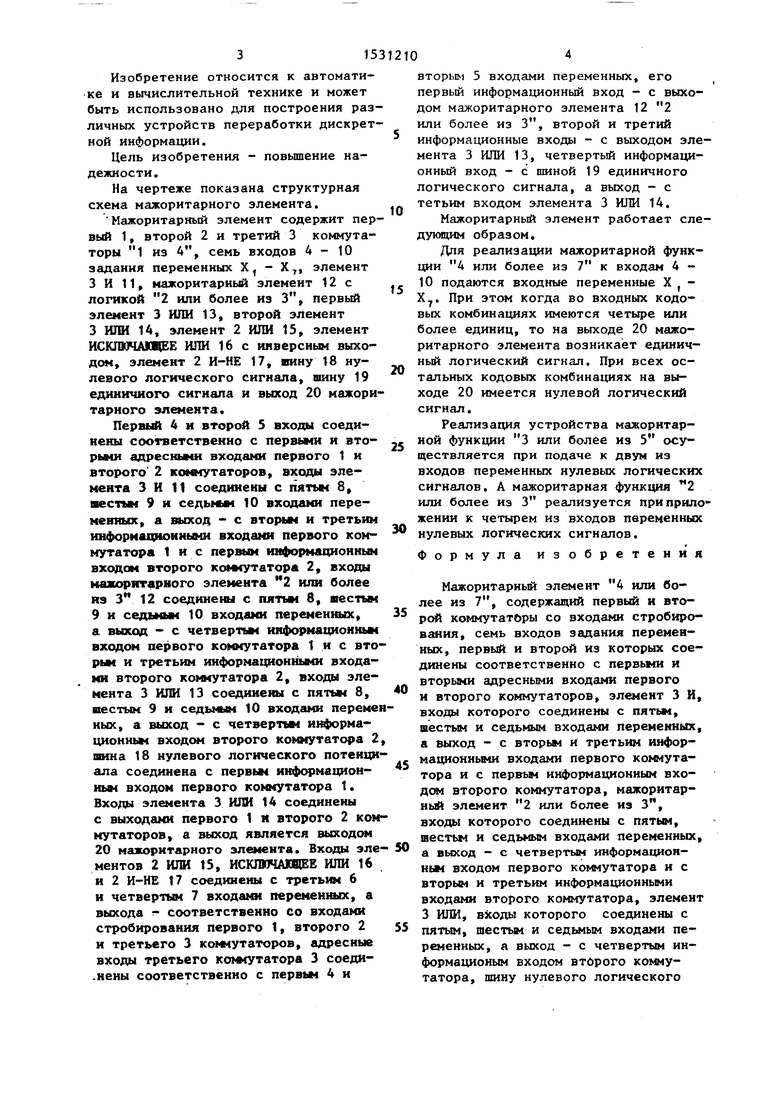

На чертеже показана структурная схема мажоритарного элемента.

Мажоритарный элемент содержит первый 1, второй 2 и третий 3 коммутаторы 1 из 4, семь входов 4-10 задания переменных X, - Х, элемент ЗИП мажоритарный элемент 12с

логикой 2 или более из 3, первый элемент 3 ИЛИ 13, второй элемент 3 И1Ш 14, элемент 2 ШШ 15, элемент ИСКЛНЧАКЩЕЕ ИЛИ 16 с инверсным выходом, элемент 2 И-НЕ 17, шину 18 нулевого логического сигнала, шину 19 единичного сигнала и выход 20 мажоритарного элемента.

Первый 4 и второй 5 входы соединены соответственно с первьми и вторыми адресньми входами первого 1 и второго 2 коммутаторов, входы элемента 3 И 11 соединены с пятьм 8, естъм 9 и седьМ1М 10 входами пере

информационными входами первого коммутатора 1 и с первым информационньш входом второго ко мутатора 2, входы мажоритарного элемента или более иэ 3 12 соединеШ) с пятьм 8, шестьм 9 и седьмьм 10 входами переменшлс, а выход - с четвертьм информационным вход(Я4 первого коммутатора 1 и с вто рьм и третьим информационньАШ входами второго коммутатора 2, входы элемента 3 ИЛИ 13 соединены с пятьм 8, шестым 9 и седьмым 10 входами переменых, а выход - с четвертьм ционньм входом второго коммутатора 2 шина 18 нулевого логического потенциала соединена с первьм информацион- ньм входом первого коммутатора 1. Входы элемента 3 ИЛИ 14 соединены с выходами первого 1 и второго 2 коммутаторов, а выход является выходом 20 мажоритарного эл |ента. Входы эле ментов 2 ИШ 15, ИСКЛЮЧАЮЩЕЕ ИЛИ 16 и 2 И-НЕ 17 соединены с третьим 6 и четвертым 7 входа о1 переменгалх, а выхода г- соответственно со входами стробирования первого 1, второго 2 и третьего 3 кслмутаторов, адресные входы третьего кo lyтaтopa 3 соеди- .нены соответственно с первьм 4 и

0

5

0

5

0

35 50 55

вторым 5 входами переменных, его первый информационный вход - с выходом мажоритарного элемента 12 2 или более из 3, второй и третий информационные входы - с выходом элемента 3 ИЛИ 13, четвертый информационный вход - с шиной 19 единичного логического сигнала, а выход - с тетьим входом элемента 3 ИЛИ 14.

Мажоритарный элемент работает сле- дукщим образом.

Для реализации мажоритарной функции 4 или более из 7 к входам 4 - 10 подаются входные переменные X - Х. При этом когда во входных кодовых комбинациях имеются четыре или более единиц, то на выходе 20 мажоритарного элемента возникает единичный логический сигнал. При всех остальных кодовых комбинациях на выходе 20 имеется нулевой логический сигнал.

Реализация устройства мажоритарной функции 3 или более из 5 осуществляется при подаче к двум из входов переменных нулевых логических сигналов. А мажоритарная функция 2 или более из 3 реализуется при приложении к четырем из входов переменных нулевых логических сигналов.

Формула изобретения

Мажоритарньй элемент 4 или более из 7, содержащий первый и вто- pcrft коммутаторы со входами стробиро- вгшия, семь входов задания переменных, первый и второй из которьлх соединены соответственно с первь т и вторыми адресными входами первого и второго коммутаторов, элемент 3 И, входы которого соединены с пятьм, шестым и седьмым входами переменных, а выход - с вторым и третьим инфор- мационньми входами первого коммутатора и с перныч информационным вхо- ДСЯ4 второго коммутатора, мажоритарный элемент 2 или более из 3, входы которого соединены с пятым, шестьм и седьмым входами переменных,

выход - с четвертым информацнон- ньм входом первого коммутатора и с вторым и третьим информационными входами второго коммутатора, элемент 3 ШШ, которого соединены с пятым, шестым и сед1«1ым входами пе

ременных, а выход - с четвертым ин- формационым входом второго коммутатора, шину нулевого логического

сигнала, которая соединена с первым информационным входом первого коммутатора, шину единичного логичекого сигнала и первьй элемент ИЛИ, первый и второй входы которого соединены с выходами первого и второго коммутаторов, а выход является вы- ходсж мажоритарного элемента, отличающийся тем, что, с целью повышения надежности, первый и второй коммутаторы выполнены со структурой 1 из 4, элемент дополнительно содержит третий коммутатор 1 из 4, второй элемент ИЛИ, элемент ИСКШОЧАИЦЕЕ ИЛИ с инверсным выходом и элемент 2 И-НЕ, а первый элемент ИЛИ содержит третий вход.

12104

входы второго элементов ИЛИ, ИСКЛКЬ ЧАКХЦЕЕ ИЛИ и 2 И-НЕ соединены с третьим и четвертым входами переменных, а выходы - соответственно с входами стробирования первого, второй и третьего коммутаторов, адресные входы третьего коммутатора соединены соответственно с первьм и .Q вторым входами переменных, его первый информационный вход - с выходом мажоритарного элемента 2 или более

иэ 3, второй и третий информационные входы - с выходом первого элемен- та 3 ИЛИ, четвертый информационный вход - с шиной единичного логического сигнала, а выход - с третьим входом первого элемента ИЛИ.

Авторы

Даты

1989-12-23—Публикация

1988-05-30—Подача