Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения различных устройств переработки дискретной информации.

Цель изобретения - расширение функциональных возможностей и области применения устройства путем реализации мажоритарной функции 4 или более из 7,

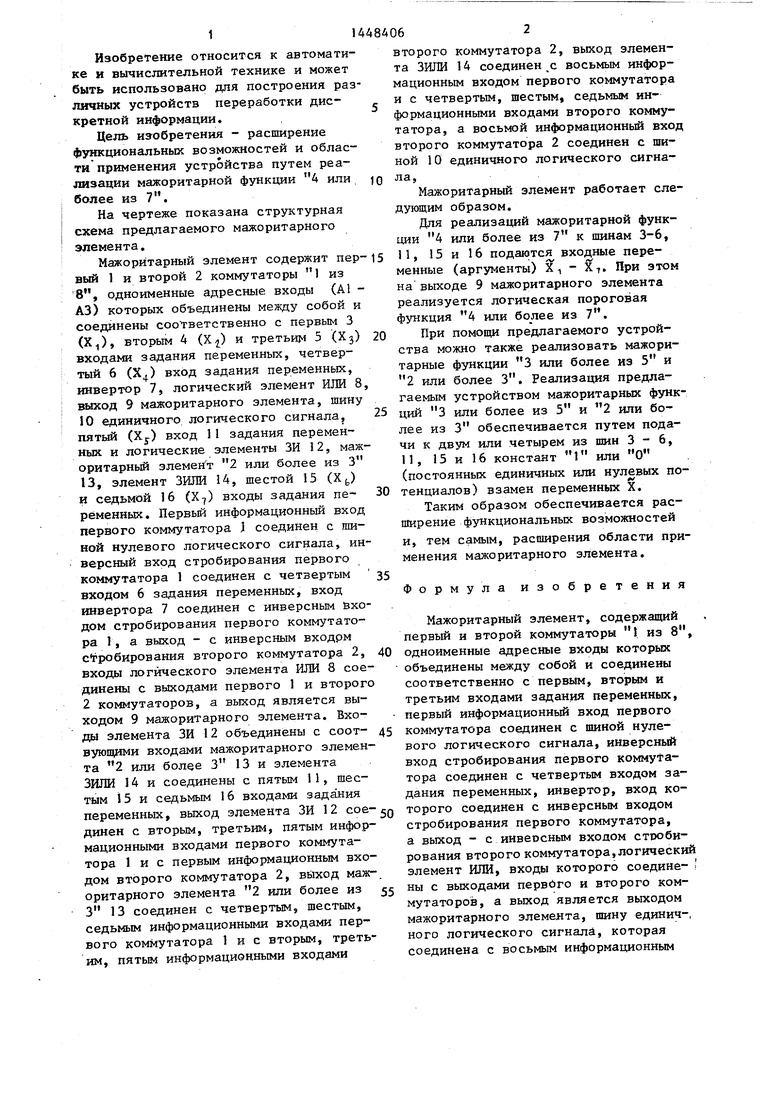

На чертеже показана структурная схема предлагаемого мажоритарного элемента.

Мажоритарный элемент содержит пер- вый 1 и второй 2 коммутаторы 1 из 8, одноименные адресные входы (А1 - A3) которых объединены между собой и соединены соответственно с первым 3 (Х), вторым 4 (Xj) и третьим 5 (Xj) входами задания переменных, четвертый 6 (Х) вход задания переменных, инвертор 7, логический элемент ИЛИ 8 выход 9 мажоритарного элемента, шину 10 единичного логического сигнала, пятый (Х|.) вход 1 1 задания переменных и логические элементы ЗИ 12, мажоритарный элемент 2 или более из 3 13, элемент ЗИЛИ 14, шестой 15 (X (,) и седьмой 16 (Х) входы задания переменных. Первьй информационный вход первого коммутатора j соединен с шиной нулевого логического сигнала, инверсный вход стробирования первого коммутатора 1 соединен с четвертым входом 6 задания переменных, вход инвертора 7 соединен с инверсным бхо- дом стробирования первого коммутатора 1, а выход - с инверсным входрм с гробирования второго коммутатора 2, входы логического элемента ИЛИ 8 соединены с выходами первого 1 и второго 2 коммутаторов, а выход является выходом 9 мажоритарного элемента. Входы элемента ЗИ 12 объединены с соот- вуюпщми входами мажоритарного элемента 2 или более 3 13 и элемента ЗИЛИ 14 и соединены с пятым П, шестым i 5 и седьмым 16 входами задания

переменных, выход элемента ЗИ 12 сое-JQ торого соединен с инверсным входом

динен с вторым, третьим, пятым информационными входами первого коммутатора 1 и с первым информационным входом второго коммутатора 2, выход маж- оритарного элемента 2 или более из 3 13 соединен с четвертым, шестым, седьмым информационными входами первого коммутатора 1 и с вторым, треть им, пятым информационными входами

стробирования первого коммутатора, а выход - с инверсным входом сттхэби рования второго коммутатора, логическ элемент ИЛИ, входы которого соедине 55 ны с выходами первйго и второго ком мутаторов, а выход является вьжодом мажоритарного элемента, шину единич ного логического сигнала, которая соединена с восьмым информационным

0

0

5

5 0 З

второго коммутатора 2, выход элемента ЗИЛИ 14 соединение восьмым информационным входом первого коммутатора и с четвертым, шестым, седьмым информационными входами второго коммутатора, а восьмой информационньй вход второго коммутатора 2 соединен с шиной 10 единичного логического сигнала.

Мажоритарный элемент работает следующим образом.

Для реализаций мажоритарной функции 4 или более из 7 к шинам 3-6, П, 15 и 16 подаются входные переменные (аргументы) X, - ic. При этом на выходе 9 мажоритарного элемента реализуется логическая пороговая функция 4 или более из 7.

При помощи предлагаемого устройства можно также реализовать мажоритарные функции 3 или более из 5 и 2 или более 3. Реализация предлагаемым устройством мажоритарных функций 3 или более из 5 и 2 или более из 3 обеспечивается путем подачи к двум или четырем из шин 3 - 6, 11, 15 и 16 констант 1 или О (постоянных единичных или нулевых по- 0 тенциалов) взамен переменных X.

Таким образом обеспечивается расширение функциональных возможностей

и, тем самым, расширения области применения мажоритарного элемента.

Формула изобретения

Мажоритарный элемент, содержащий первый и второй коммутаторы из 8 одноименные адресные входы которых объединены между собой и соединены соответственно с первым, вторым и третьим входами задания переменных, первый информационный вход первого коммутатора соединен с шиной нулевого логического сигнала, инверсный вход стробирования первого коммутатора соединен с четвертым входом задания переменных, инвертор, вход ко

стробирования первого коммутатора, а выход - с инверсным входом сттхэби- рования второго коммутатора, логический элемент ИЛИ, входы которого соедине- 5 ны с выходами первйго и второго коммутаторов, а выход является вьжодом мажоритарного элемента, шину единич-, ного логического сигнала, которая соединена с восьмым информационным

входом второго коммутатора, пятый вход задания переменных, отличающийся тем, что, с целью расширения функциональных возможностей и области применения за счет реализации логической функции 4 или более из 7, в него дополнительно введены элемент ЗИ, мажоритарный элемент 2 или более из 3, элемент ЗШШ, шестой и седьмой входы задания переменных, входы элемента ЗИ объединены с соответствующими входами мажоритарного элемента 2 или более из 3 и элемента ЗИПИ и соединены с пятым, шее- тым и седьмым входами задания пере

15

448406

менных, выход элемента ЗИ соедннен с вторым, третьим, пятым информационными входами первого коммутатора и с первым информационным входом второго коммутатора, выход мажоритарного элемента 2 или более из 3 соединен с четвертым, шестым, седьмым информационными входами первого коммутатора и с вторым, третьим, пятым информационными входами второго коммутатора; выход элемента ЗИЛИ соединен с -вось- мым информационным входом первого - коммутатора и с четвертым, шестым, седьмым информационными входами второго коммутатора.

10

| название | год | авторы | номер документа |

|---|---|---|---|

| Мажоритарный элемент | 1987 |

|

SU1499487A1 |

| Мажоритарный элемент | 1988 |

|

SU1538249A1 |

| Мажоритарный элемент "4 или более из 7 | 1988 |

|

SU1531210A1 |

| Мажоритарный элемент | 1990 |

|

SU1750052A1 |

| Пороговое логическое устройство | 1987 |

|

SU1422400A1 |

| Многофункциональный логический модуль | 1987 |

|

SU1495990A1 |

| Пороговое логическое устройство | 1987 |

|

SU1499488A1 |

| Многофункциональный логический модуль | 1983 |

|

SU1164693A1 |

| МАЖОРИТАРНЫЙ ЭЛЕМЕНТ | 1991 |

|

SU1819100A1 |

| Устройство для симметрирования токов трехфазных сетей | 1988 |

|

SU1686600A1 |

Изобретение относится к импульсной технике и дискретной автоматике и может быть использовано для построения различных устройств переработки дискретной информации. Цель изобретения - расширение функциональных возможностей и области применения устройства, путем реализации ма- жоритарной функции 4 шш более из 7., Дополнительные функциональные возможности обеспечиваютея элемеитами И 12, 2 или более из 3 13 и ИЛИ 14, входы которых объединены и на которые пос У тупают входйые сигналы, а выходы соединены с входами коммутаторов 1 и 2, выхода которых соединены с входами элемента ИЛИ В, с выхода которого снимается требуемая функция. 1 ил. W с Sl& xsffJ

| Зельдин Е.А.Цифровые интегральные микросхемы в информационно-измерительной аппаратуре | |||

| Л,: Эиерго- атомиздат, 986, с.107, рис | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| и др, IfaKpo электронные устройства программного и логического Зтравления | |||

| М.: Машиностроение, 1979, с,41, йис | |||

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1988-12-30—Публикация

1987-05-06—Подача