1

(61) 1311028

(21)4А00176/24-24

(22)29.03.88

(46) 23.12.89. Бнш. № 47

(71)Институт кибернетики им. В.М.Глушкова

(72)В.П.Стокай, Л.И.Зелинский и В.И.Заболотный

(53)681.325(088.8)

(56)Авторское свидетельство СССР 1311028, кл. Н 03 М 1/64, 1986.

(54)АДАЛТИВНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

(57)Изобретение относится к измерительной и вычислительной технике. По- вынейие точности аналого-цифрового преобразователя достигается за счет линеаризации соответствующего участка выходной характеристики рабочего

фазовращателя. При этом происходит промежуточное преобразование входных сигналов в фазовый сдвиг опорного напряжения с последующим кодированием полученного фазового сдвига. Линеаризация осуществляется за счет того, что в течение второго такта работы преобразователя, частота управляемого генератора 13 импульсов изменяется в соответствии с изменением крутизны того участка выходной характеристики рабочего фазовращателя 6, в пределах которого находится значение нескомпенсированного фазового сдвига, подлежащего кодированию в течение второго такта. Для этого в преобразователь введены блок 20 управляющих напряжений, коммутатор 21, третий опорный фазовращатель 22 и третий опорный компаратор 23. 2 ил,

i

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный аналого-цифровой преобразователь | 1986 |

|

SU1311028A1 |

| Аналого-цифровой преобразователь с автокоррекцией погрешности | 1983 |

|

SU1091337A1 |

| Аналого-цифровой преобразователь с автокоррекцией погрешности (его варианты) | 1983 |

|

SU1144189A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU884121A1 |

| Адаптивное кодирующее устройство | 1983 |

|

SU1166308A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1156258A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1297225A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1095393A1 |

| Быстродействующий аналого-цифровой преобразователь | 1985 |

|

SU1254584A1 |

| Устройство для измерения фазового сдвига | 1984 |

|

SU1190294A1 |

Изобретение относится к измерительной и вычислительной технике. Повышение точности аналого-цифрового преобразователя достигается за счет линеаризации соответствующего участка выходной характеристики рабочего фазовращателя. При этом происходит промежуточное преобразование входных сигналов в фазовый сдвиг опорного напряжения с последующим кодированием полученного фазового сдвига. Линеаризация осуществляется за счет того, что в течение второго такта работы преобразователя частота управляемого генератора 13 импульсов изменяется в соответствии с изменением крутизны того участка выходной характеристики рабочего фазовращателя 6, в пределах которого находится значение нескомпенсированного фазового сдвига, подлежащего кодированию в течение второго такта. Для этого в преобразователь введены блок 20 управляющих напряжений, коммутатор 21, третий опорный фазовращатель 22 и третий опорный компаратор 23. 2 ил.

К

Art/

Изобретение относится к измерительной и вычислительной технике, преимущественно может быть не- пользовано в аналого-цифровых преоб- разо&ателях (АЦП) и является усовершенствованием изобретения по авт. св„ № 1311028.

Целью изобретения является повышение точности.

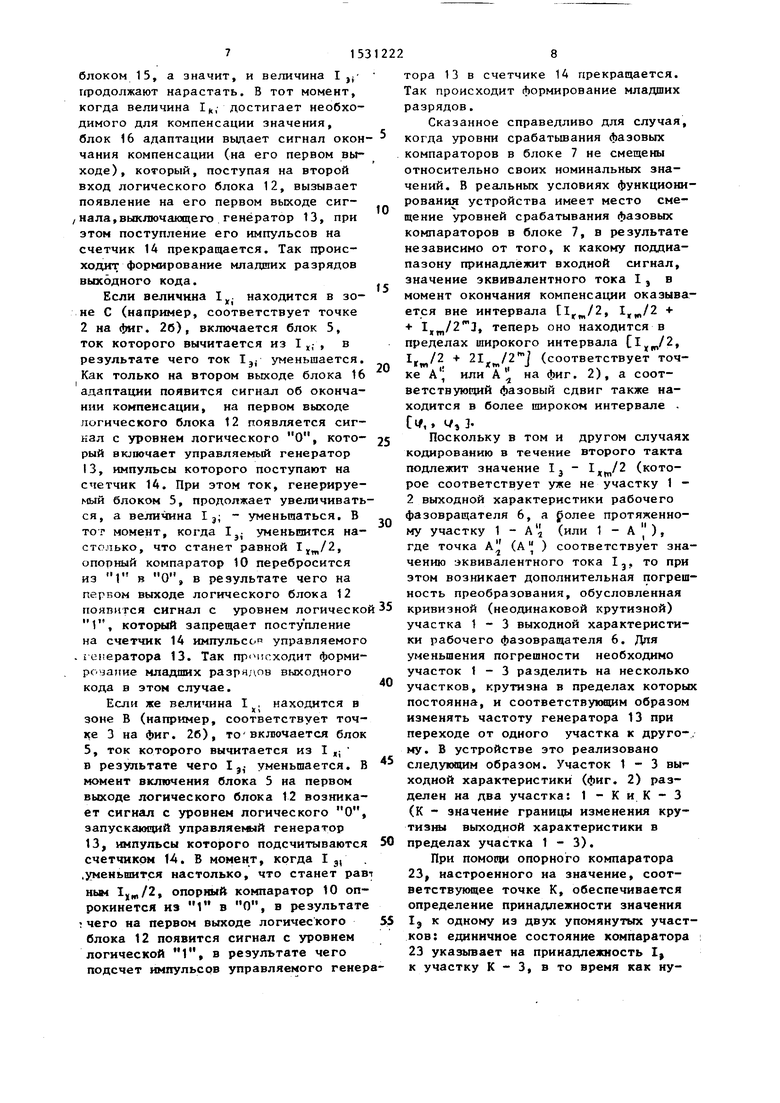

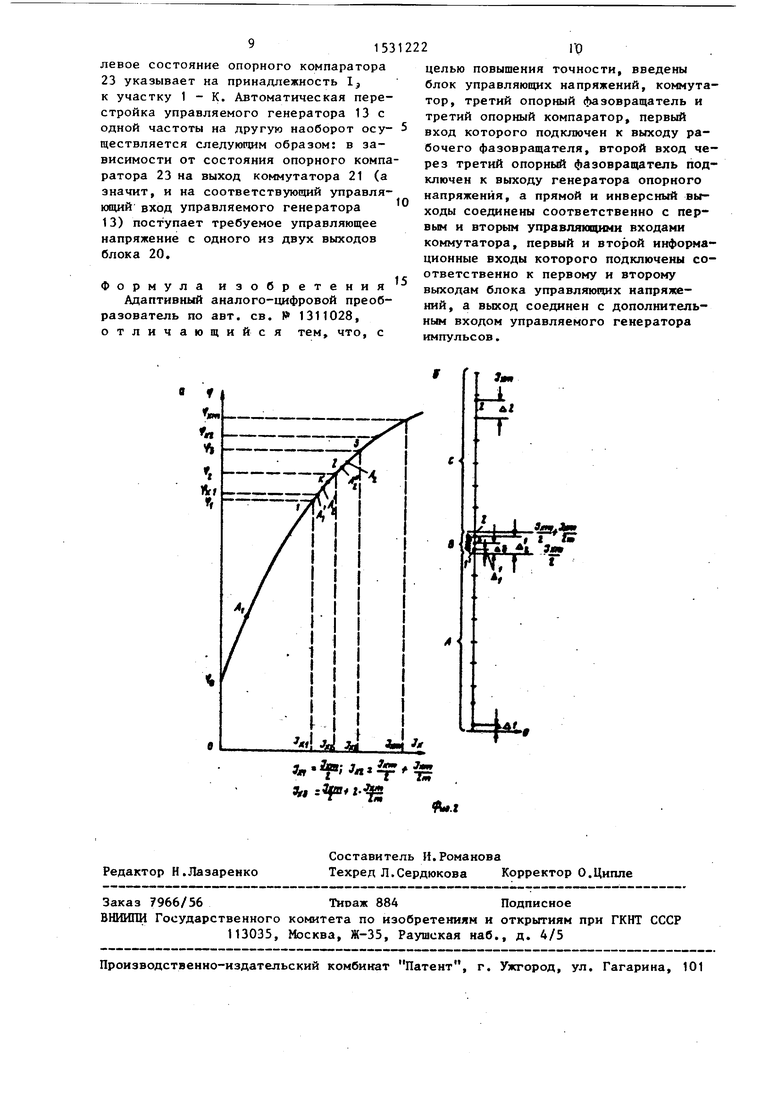

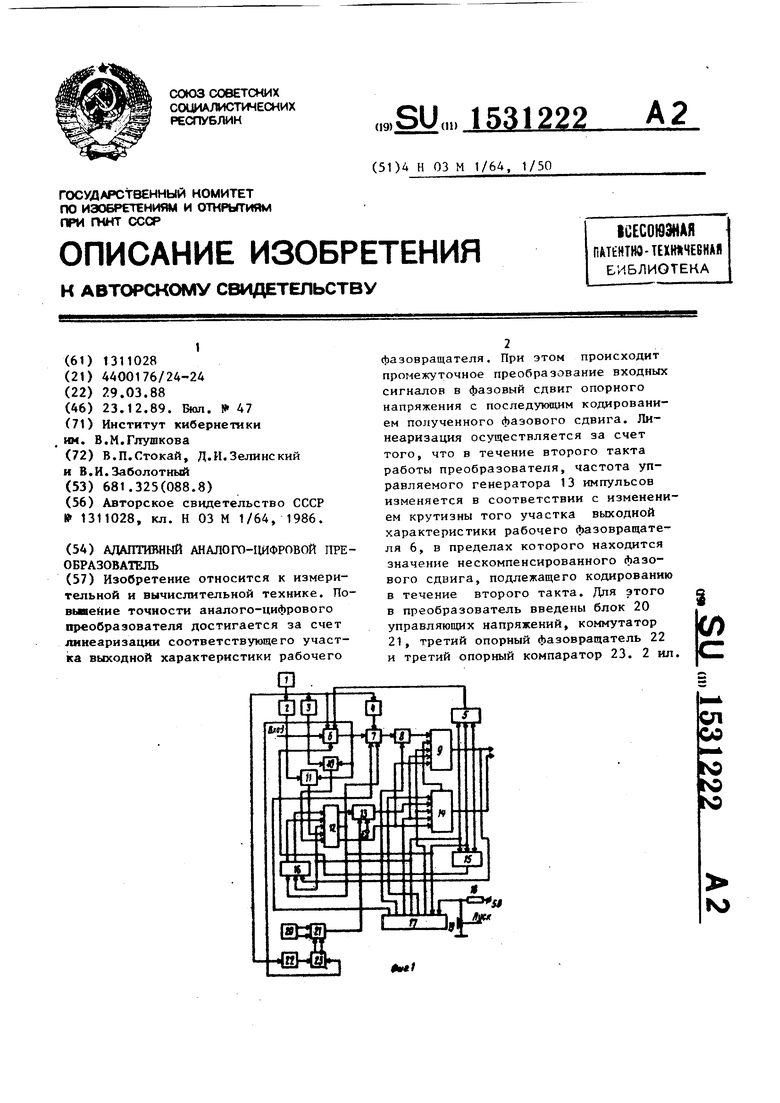

На фиг. 1 представлена функциональная схема устройства; на фиг.2(а, б) - диаграммы, поясняющие фop rapo- нание младших разрядов кода.

Устройство содержит генератор 1 опорного напряжения, опорные фазовраатели 2 и 3, фазовращатель А смещения, блок 5 компенсирующего тока, рабочий фазовращатель 6, блок 7 фазовых компараторов, шифратор 8, счетчик 9, опорные компараторы 10 и 11,j огический блок 12, управляеьвлй геератор 13, счетчик 14, блок 15 коменсирующего тока, блок 16 адаптации, лок 17 управления, резистор 18, норально замкнутые контакты 19, блок 0 управляю1цкх напряжений, коммутатор 21, опорный фазовращатель 22, опорный компаратор 23.

Формироваиие п-разрядного преобразуемого сигнала происходит за два такта: в течение первого такта при помощи генератора 1, фазовращателей 4 и 6, блока 7 фазовых компараторов шифратора 8 происходит формирование m стар1шх разрядов. Затем начинается компенсация, в процессе которой из фазового сдвига, пропорционально- го входному сигналу, вычитается его часть, пропорциональная коду сформированных старших разрядов.

По окончании компенсации выкодное напряжение р.абочего фазовращателя 6 имеет некоторый остаточный (нескомпенсированный) фазовый сдвиг который кодируется в течение второго такта работы.

Лпя пояснения алгоритма формирования п - га младших разрядов кода напомним, что диапазон изменения преобразуемых сигналов разбит на три поддиапазона А, В и С (ф«г. 2), и формирование младших разрядов происходит по-разному в зависимости от того, в каком из поддиапазонов на- ходится входной сигнал.

Если значение входного сигнала I находится в поддиапазоне А (О I „ 4 4I|(), то младшие разряды формируются путем подсчета импульсов генератора 13 счетчиком 14 в течение интервала времени Qt L

t- 01

«

t(cJ. где - момент опрокидывания опорного компаратора 10 из О

Г

5

0

5

0

5

0

t - момент окончания компенсахщи. Если значение входного сигнала 1 находится в поддиапазоне В ( 1 1хш/2 + I.n./), то младшие разряды формируются путем подсчета импульсов генератора 13 в счетчике 14

в течение интервала времени ft, tj, г Де

- момент начала

компенсации; t - момент опрокидывания фазового компенсатора 10 из 1.

Если значение входного сигнала 1 находится в поддиапазоне С (1 /2ч - I j( -IXM младшие разряды формируются путем подсчета импульсов генератора 13 счетчиком 14

в течение интервала времени t в

н

к

где IK- момент окончания то

5

0

5

компенсации i t ; - момент опрокидывания фазового компаратора 10 из 1 в О.

Б реальных условиях на работу устройства воздействуют дестабилизирующие факторы (изменения окружающей .температуры, питающих напряжений и т.д.), вследствие чего возможно смещение уровней срабатывания фазовых компараторов в блоке 7 как в сторону увеличения, так и в сторону уменьшения относительно их номинальных значений. Соответственно код старших разрядов получают с недостатком (т.е. меньше его действительного значения) или с избытком (т.е. больше его действительного значения). Однако благодаря наличию фазовращателя 4 в составе устройства код старвмх разрядов может быть получен либо правильным, либо с недостатком (но никогда с избытком).

Если код старвих разрядов получен с недостатком, то конечное значение компенсирующего тока уменьшится (по сравнению со случаем, когда код старших разрядов правильный), при этом имеет место недокомпёнсация, из-за чего остаточный фазовый сдвиг, подлежащий кодирование в течение второго такта работы, превьвпает дискретность устройства на первом такте его работы.

Поскольку формирование младших разрядов осуществляется путем заполнения эквивалентного временного интервала импульсами стабильной частоты (т.е. время-импульсным способом), возникает погрешность преобразования обусловленная нелинейностью выходной характеристики рабочего фазовращателя 6.

Как уже упоминалось, в случае воздействия дестабилизируюпщх факторов возможен случай, когда значение остаточного фазового сдвига, подлежащего кодированию время-импульсным способом в течение второго такта работы прототипа, превышает дискретность прототипа на первом такте его работы. Поскольку выходная характеристика рабочего фазовращателя 6 имеет ярко выраженный нелинейный характер (фиг, 2), протяженность (а значит, и нелинейность) участка выходной характеристики, соответствующая значению t/ в этом случае (т.е. при получении кода старших разрядов с недостатком), увеличивается, что автоматически привода т к увеличению погрешности устройства в целом. Поясним сказанное с помощью графика, приведенного на фиг. 2.

При отсутствии дестабилизирующих факторов значение эквивалентного

тока I

t)rl

чение преобразуемого сигнала; I ц, значение соответствующего ему тока компенсации), воздействующего на вход устройства, всегда находится в интервале Cl,/2 + Соответственно, значение остаточного фазового сдвига i . , всегда находится в интервале С i/,, (-/jjt соответствует участку выходной характеристики рабочего фазовращателя 6 между точками 1 и 2. При этом погрешность 11 от нелинейности этого участка является одной из доминирующих составляющих общей погрешности для этого случая.

Воздействие дестабилизирую1цих факторов приводит к тому, что код m старших разрядов получается с недостатком, вследствие чего значение эквивалентного тока I эг I xi ici воздействующего на вход прототипа, сказывается за пределами интервала , 1,/2 + I. теперь значение 1,1 находится в интервале 11,/2, 1,„/2 + 21,/2. Соответст- венно, значение остаточного фазового сдвига «.ст находится в более ши- I „, (где I V, - зна

роком интервале /),1/з1 который соответствует участку выходной характеристики рабочего фазовращателя 6 между точками 1 и 3 (фиг, 2). При этом погрешность (, от нелинейности этого участка является одной из доминирующих составляюпщх общей погрешности для этого случая.

Устройство работает следующим образом.

При нажатии кнопки Пуск (фиг.2) происходит запуск блока 17 управления - на его выходах появляются управляющие сигналы, обеспечивающие функционирование блоков предлагаемого устройства по заданному алгоритму. Фазовый сдвиг i/ . выходного напряжения рабочего фазовращателя 6,

0 пропорциональный величине входного (преобразуемого) сигнала , поступает на первый информационный вход блока 7 фазовых компараторов. Блок 7 содержит в своем составе 1 фазо5 вых компараторов (компараторов напряжений), при помощи которых диапазон изменения преобразуемых сигналов 0... I 1 разделяется на 2 зоны одинаковой величины, где п - количество старших двоичных разрядов, определяемых на первом такте работы устройства. В зависимости от величины с/к; в блоке 7 срабатывает соответствующее количество фазовых компараторов, в результате чего на выходе блока 7 получают уни-. арный код, при помощи шифратора 8 он преобразуется в двоичный код, после чего заносится в счетчик 9. Так происходит формирование старших разрядов выходного кода.

Затем по сигналу с выхода блока 17 управления начинается компенсация. Если 1у находится в зоне А, например, соответствует точке 1 на фиг. 2б, то включается блок 15, ток которого складывается с I у;, в результате чего эквивалентный ток 1э1 воздействующий на вход устройства, увеличивается. Как только Iз; достигает значения, равного 1,/2, происходит перебрасывание из О в 1 опорного компаратора 10, в результате чего на первом выходе логического блока 12 появляются сигнал с уровнем логический О, запускающий управляемый генератор 13, импульсы которого начинают подсчитьшаться счетчиком

0

5

0

5

0

5

м

генерируемый

10

15

блоком 15, а значит, и величина I jj/ гфодолжают нарастать. В тот момент, когда величина 1, достигает необхоимого для компенсации значения, блок 16 адаптации выдает сигнал окончания компенсации (на его первом выходе), который, поступая на второй вход логического блока 12, вызывает появление на его первом выходе сигнала,выключающего генератор 13, при этом поступление его импульсов на счетчик 14 прекращается. Так происходит формирование младших разрядов выходного кода.

Если величина 1. находится в зоне С (например, соответствует точке 2 на фиг. 2б), включается блок 5, ток которого вычитается из I ; , в результате чего ток Ijj уменьшается. Как только на втором выходе блока 16 адаптации появится сигнал об окончании компенсации, на первом выходе логического блока 12 появляется сигнал с уровнем логического О, который включает управляемый генератор 13, импульсы которого поступают на счетчик 14. При этом ток, генерируемый блоком 5, продолжает увеличиваться, а величина Ij; - уменьшаться. В тот момент, когда 1 уменьшится настолько, что станет равной 1,/2, опорный компаратор 10 перебросится из 1 в О, в результате чего на первом выходе логического блока 12 появится сигнал с уровнем логической 35 1, который запрещает поступление на счетчик 14 импульсор управляемого

ге ератора 13. Так пр мк ходит формирование младших разркдов выходного кода в этом случае.

Если же велтичина 1, находится в зоне В (например, соответствует точке 3 на фиг. 26), ТО включается блок

20

25

30

40

5, ток которого вычитается из I

i

В

в результате чего Ij,- уменьшается, момент включения блока 5 на первом выходе логического блока 12 возникает сигнал с уровнем логического О, запускаю1 Ц1й управляемый генератор 13, импульсы которого подсчитываются счетчиком 14. В момент, когда I д, .уменьшится настолько, что станет равт ным , опорный компаратор 10 опрокинется из 1 в О, в результате -. чего на первом выходе логического блока 12 появится сигнал с уровнем логической 1, в результате чего подсчет импульсов управляемого генер0

5

5

0

5

0

тора 13 в счетчике 14 прекращается. Так происходит формирование младших разрядов.

Сказанное справедливо для случая, когда уровни срабатьшания фазовых компараторов в блоке 7 не смещены относительно своих номинальных значений. В реальных условиях функционирования устройства имеет место смещение уровней срабатывания фазовых компараторов в блоке 7, в результате независимо от того, к какому поддиапазону принадлежит входной сигнал, значение эквивалентного тока I, в момент окончания компенсации оказывается вне интервала , 1,/2 + + , теперь оно находится в пределах широкого интервала С1к,„/2, (соответствует точ- на фиг. 2), а соот- ветствуюсщй фазовый сдвиг также находится в более широком интервале .

Cif,. I/, 3Поскольку в том и другом случаях кодированию в течение второго такта подлежит значение I, - 1,/2 (котоУ Д П«

рое соответствует уже не участку 1 - 2 выходной характеристики рабочего фазовращателя 6, а ролее протяженному участку 1 - А (или 1 - А ),

1г./2 ке А :

- .. или А

где точка (А ) соответствует чению эквивалентного тока I,. то

з

зна- при

35

40

45

50

этом возникает дополнительная погрешность преобразования, обусловленная кривизной (неодинаковой крутизной) участка 1 - 3 выходной характеристики рабочего фазовращателя 6. Для уменьшения погрешности необходимо участок 1 - 3 разделить на несколько участков, крутизна в пределах которых постоянна, и соответствующим образом изменять частоту генератора 13 при переходе от одного участка к друго-, му. В устройстве это реализовано следующим образом. Участок 1-3 выходной характеристики (фиг. 2) разделен на два участка: 1 - К и К - 3 (К - значение границы изменения кру- выходной характеристики в пределах участка 1-3).

При noMOiw опорного компаратора 23, настроенного на значение, соответствующее точке К, обеспечивается определение принадлежности значения 55 Ij к одному из двух упомянутых участков: единичное состояние компаратора : 23 указывает на принадлежность I, к участку К - 3, в то время как ну9153

левое состояние опорного компаратора 23 указывает на принадлежность 1 к участку 1 - К. Автоматическая перестройка управляемого генератора 13 с одной частоты на другую наоборот осу- ществляется следуюрщм образом: в зависимости от состояния опорного компаратора 23 на выход коммутатора 21 (а значит, и на соответствующий управляющий вход управляемого генератора 13) поступает требуемое управляющее напряжение с одного из двух выходов блока 20.

Формула изобретения

Адаптивный аналого-цифровой преобразователь по авт. св. 1311028, отличающийся тем, что, с

ГО

5 0

5

целью повышения точности, введены блок управляющих напряжений, коммутатор, третий опорный фазовращатель и третий опорный компаратор, первый вход которого подключен к выходу рабочего фазовращателя, второй вход через третий опорный фазовращатель подключен к выходу генератора опорного напряжения, а прямой и инверсный выходы соединены соответственно с первым и вторым управляющими входами коммутатора, первый и второй информационные входы которого подключены соответственно к первому и второму выходам блока управляющих напряжений, а выход соединен с дополнительным входом управляемого генератора импульсов.

а.

е

Дя«.

Ц

Авторы

Даты

1989-12-23—Публикация

1988-03-29—Подача