Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах, например коммуникационных мультипроцессорных комплексах, в которых требуется введение очередей зада- 1ШЙ и заявок на обслуживание, а так- яе осуществление синхронизации процессов и процессоров через механизм очередей.

Эффективность функционирования таких вычислительных систем во многом зависит от реализации механизма очередей.

Целью изобретения является повышение быстродействия и сокращение аппаратурных затрат.

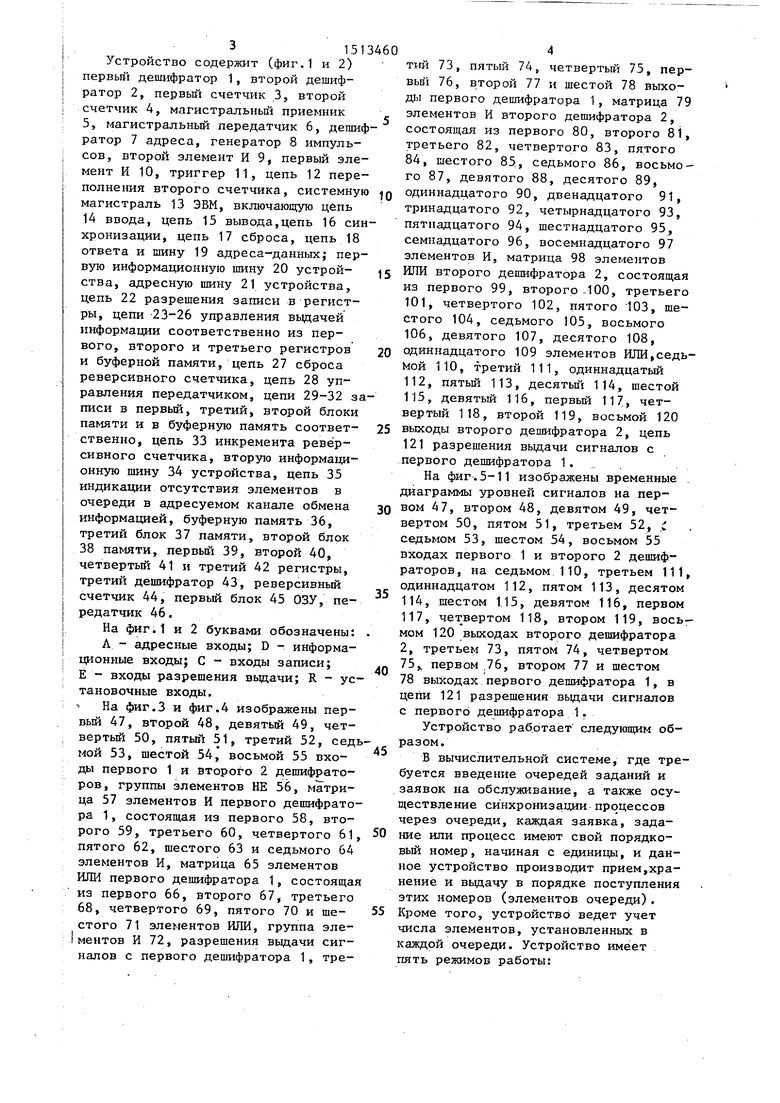

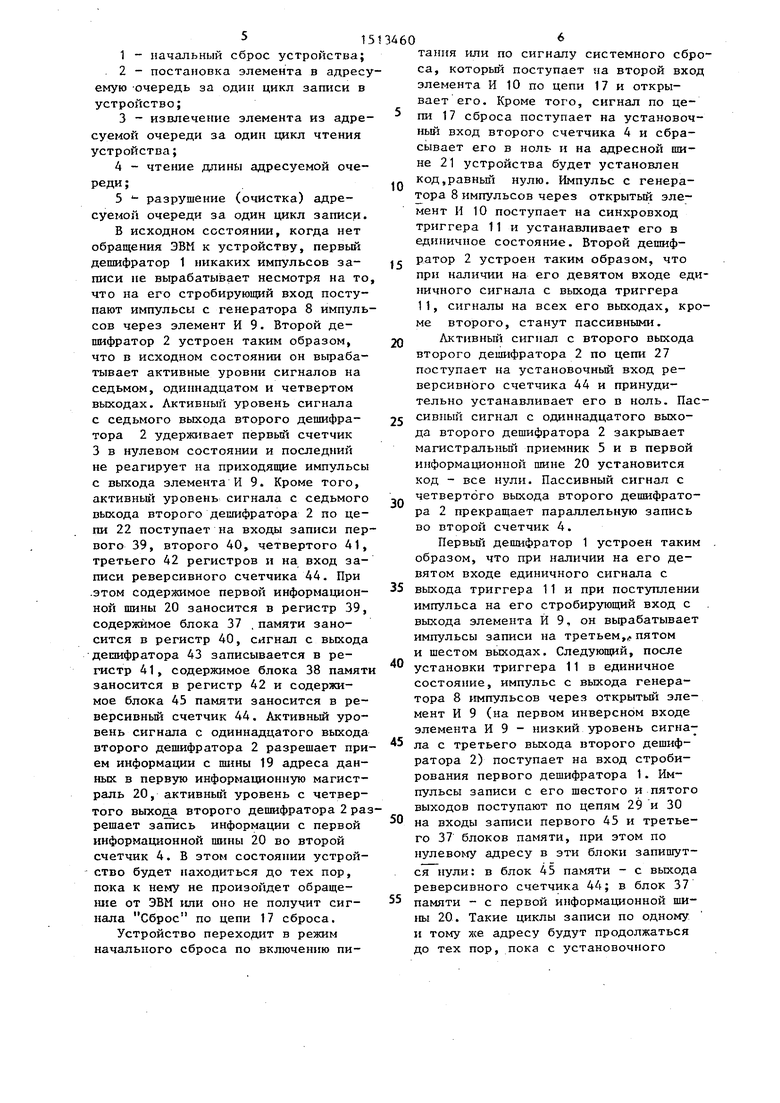

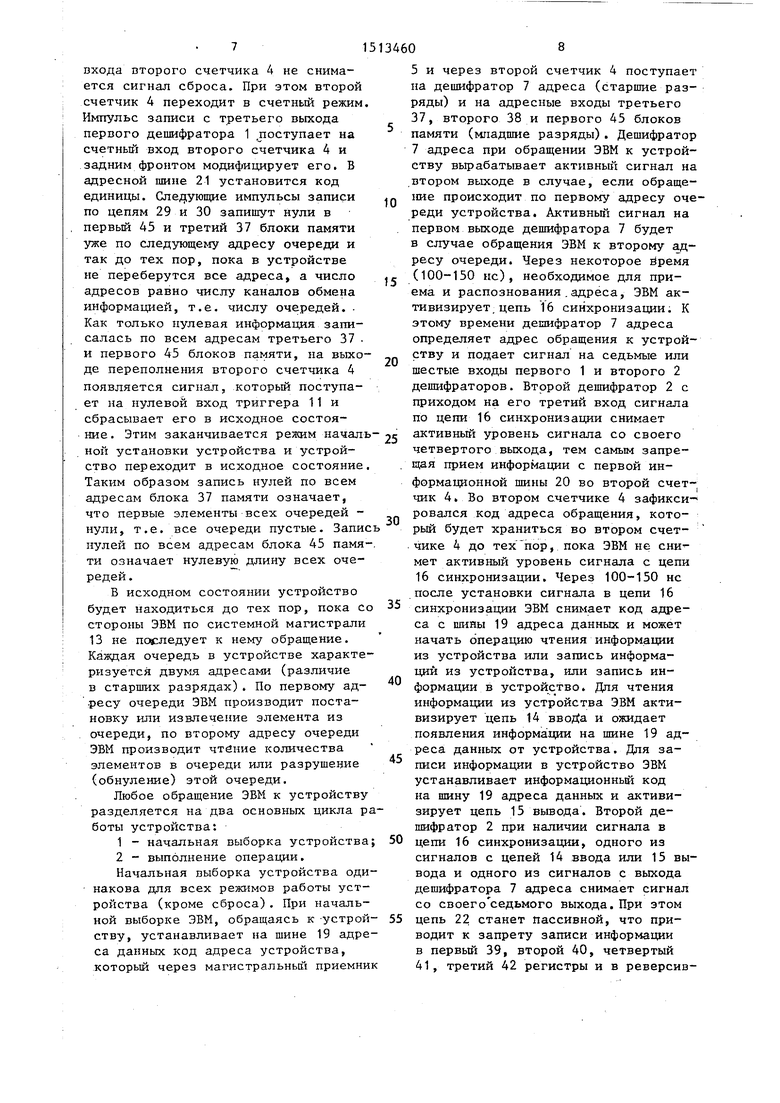

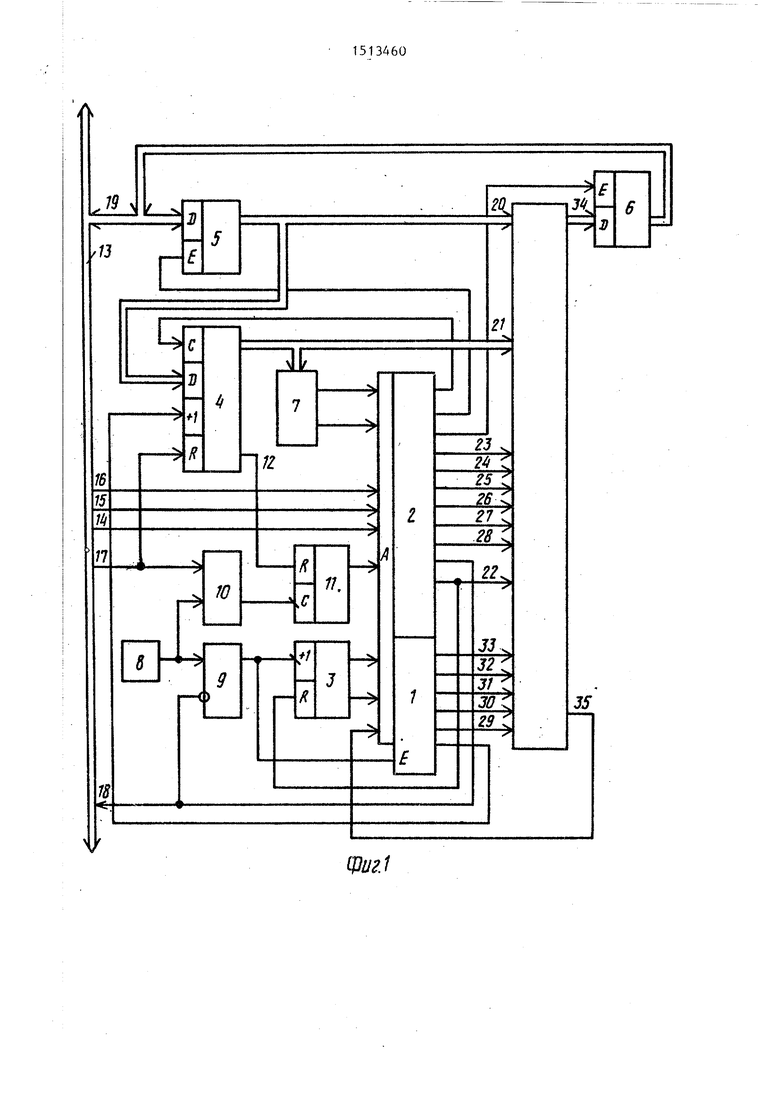

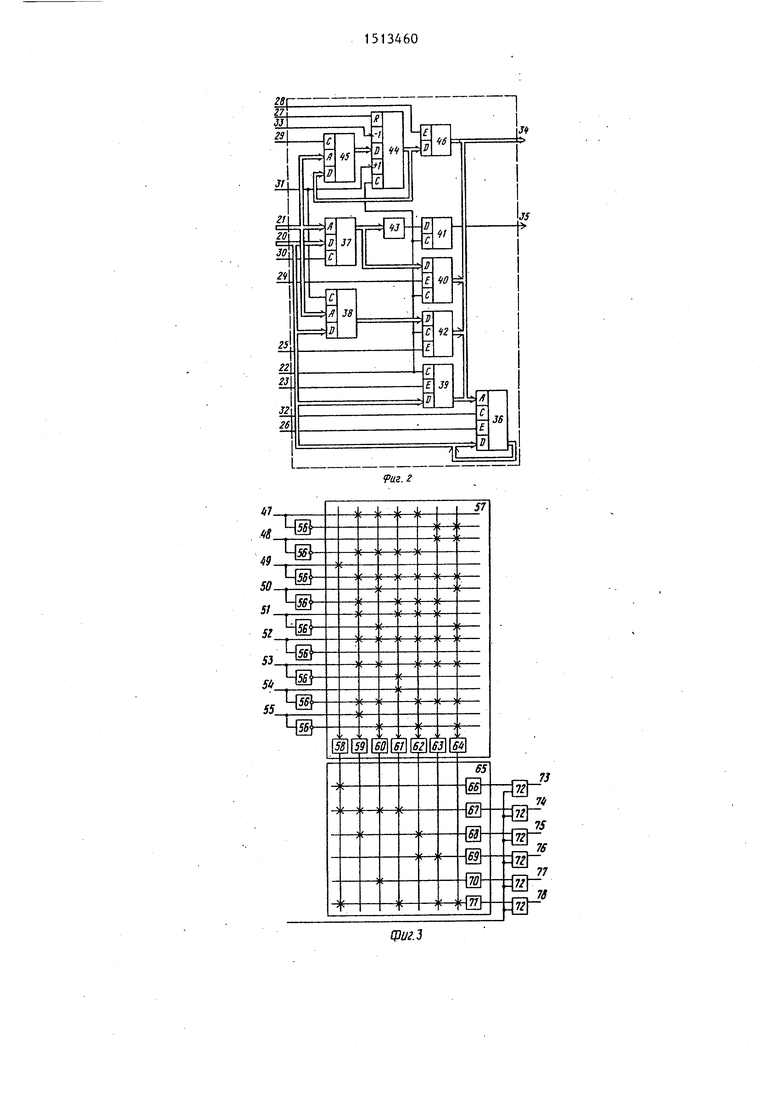

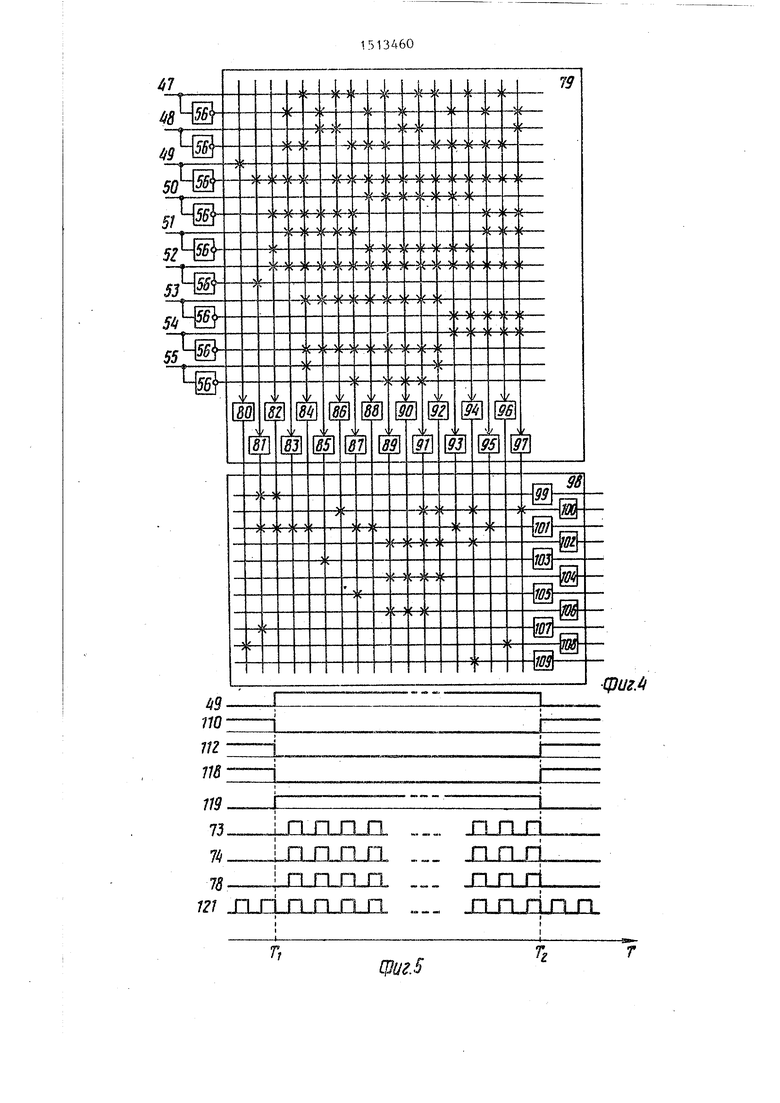

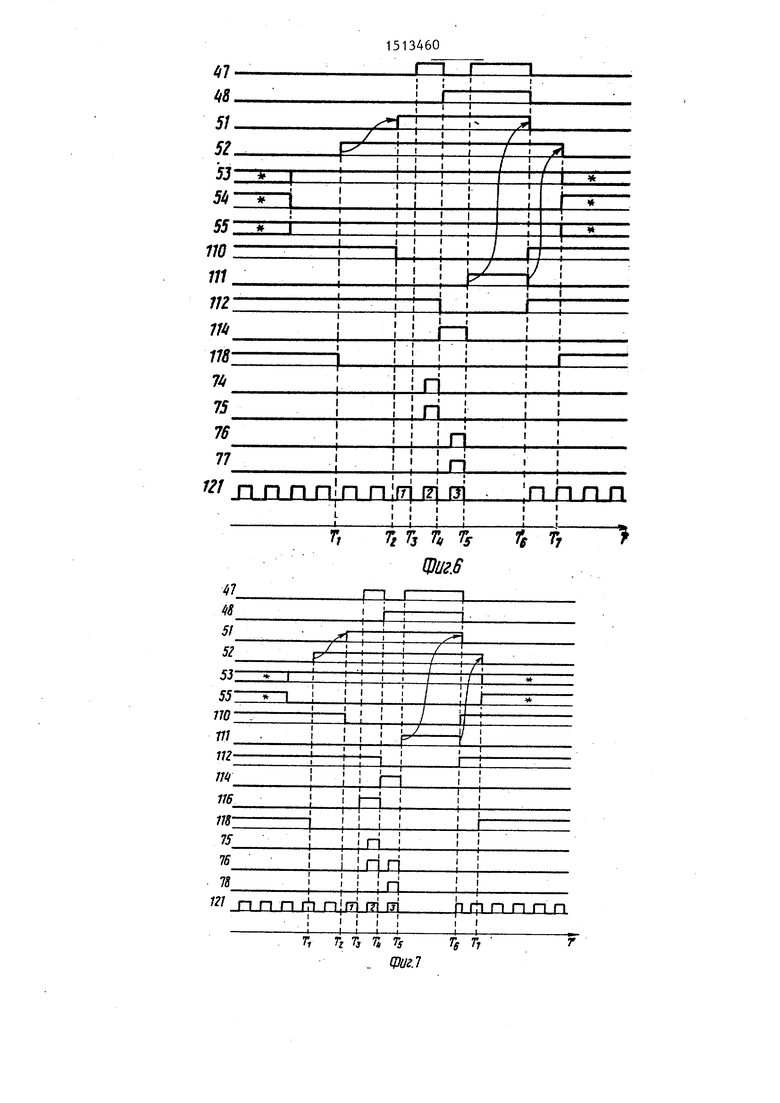

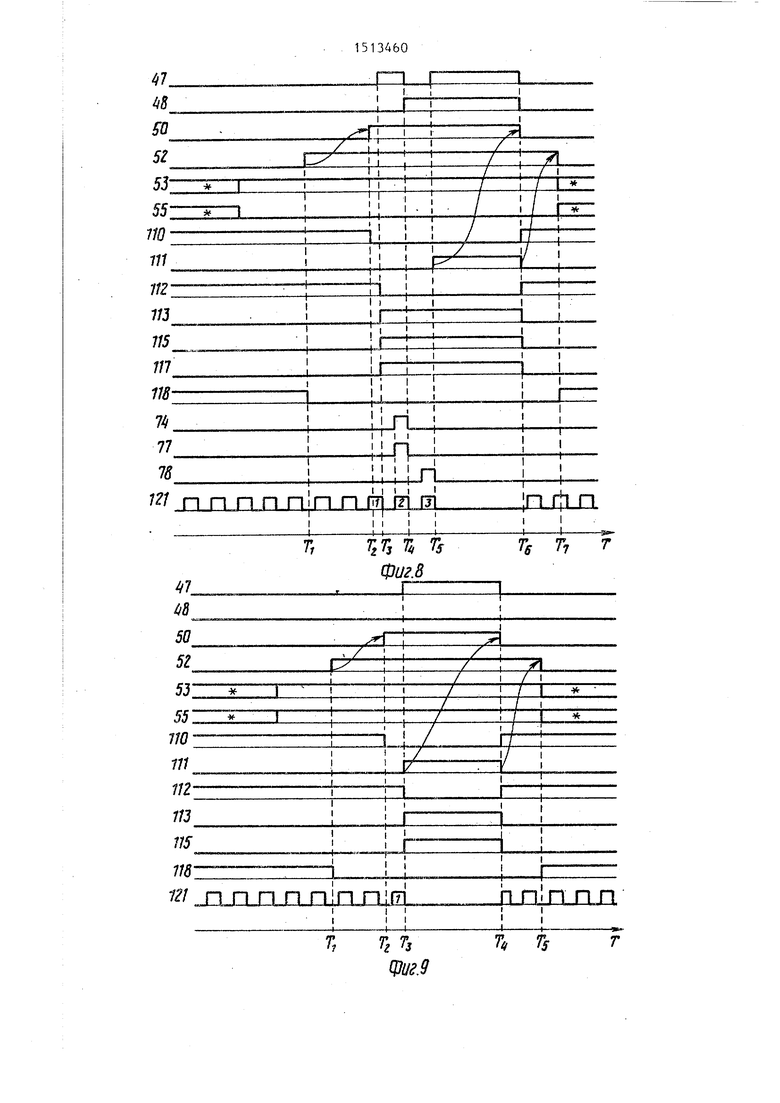

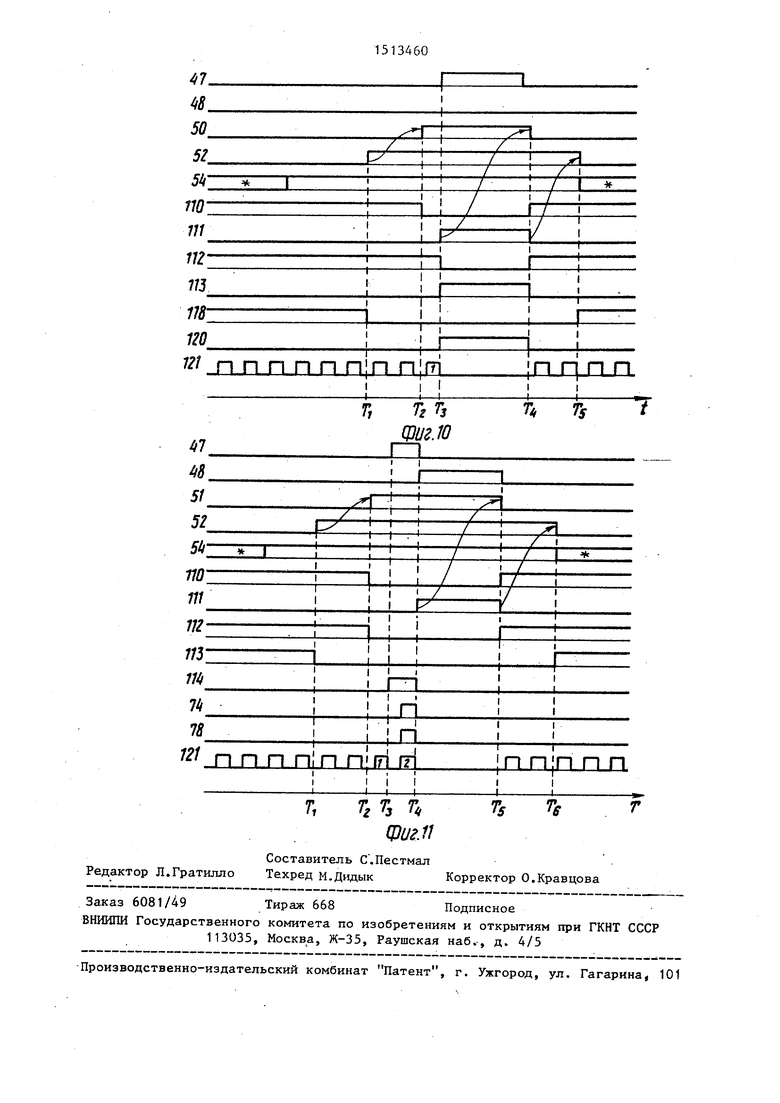

На фиг.1 и 2 представлена структурная схема устройства; на фиг.З - структурная схема первого дешифратора; на фиг.4 - структурная схема второго дешифратора; на фиг.5 - временная диаграмма работы первого и второго дешифраторов в режиме начального сброса; на фиг.6 - то же, в режиме постановки злемента очереди в пустую очередь; на фиг.7 - то же, в режиме постановки элемента очереди в непустую очередь;на фиг.8 - то же, в режиме извлечения элемента очереди из непустой очереди; на фиг,9 - временная диаграмма работы второго дешифратора в режиме извлечения элемента очереди из пустой очереди; на фиг.10 - то же, в режиме получения текущей длины очереди; на фиг.11 - временная диаграмма работы перво1:о и второго дешифраторов в режиме разрушения очереди.

сл

со

4

Од

31513

Устройство содержит (фиг.1 и 2) первьш дешифратор 1, второй дешифратор 2, nepBbrit счетчик 3, второй счетх1ик 4, магистральньй приемник 5, магистральный передатчик 6, дешифратор 7 адреса, генератор 8 импульсов, второй элемент И 9, первый элемент И 10, триггер 11, цепь 12 переполнения второго счетчика, системную магистраль 13 ЭВМ, включающую цепь 14 ввода, цепь 15 вывода,цепь 16 синхронизации, цепь 17 сброса, цепь 18 ответа и шину 19 адреса-данных; первую информационную шину 20 устрой- ства, адресную шину 21 устройства, цепь 22 разрешения записи в регистры, цепи 23-26 управления выдачей информации соответственно из первого, второго и третьего регистров и буферной памяти, цепь 27 сброса реверсивного счетчика, цепь 28 управления передатчиком, цепи 29-32 записи в первый, третий, второй блоки памяти и в буфернзпо память соответ- ственно, цепь 33 инкремента реверсивного счетчика, вторую информационную шину 34 устройства, цепь 35 индикации отсутствия элементов в очереди в адресуемом канапе обмена информацией, буферную память 36, третий блок 37 памяти, второй блок 38 памяти, первьв 39, второй 40, четвертый 41 и третий 42 регистры, третий дешифратор 43, реверсивный счетчик 44, первьй блок 45 ОЗУ, передатчик 46.

На фиг.1 и 2 буквами обозначены: Л - адресные входы; D - информационные входы} С - входы записи; Ё - входы разрешения выдачи; R - установочные входы.

На фиг.З и фиг.4 изображены первый 47, второй 48, девятый 49, четвертый 50, пятый 51, третий 52, седьмой 53, шестой 54, восьмой 55 входы первого 1 и второго 2 дешифраторов , группы элементов НЕ 56, матрица 57 элементов И первого дешифратора 1, состоящая из первого 58, второго 59, третьего 60, четвертого 61, пятого 62, шестого 63 и седьмого 64 элементов И, матрица 65 элементов ИЖ первого дешифратора 1, состоящая из первого 66, второго 67, третьего 68, четвертого 69, пятого 70 и ше- стого 71 элементов ИЛИ, группа эле- I ментов И 72, разрешения выдачи сигналов с первого дешифратора 1, тре

5 о

0 5

5

5

тий 73, пятый 74s четвертый 75, первьш 76, второй 77 и шестой 78 выходы первого дешифратора 1, матрица 79 элементов И второго дешифратора 2, состоящая из первого 80, второго 81, третьего 82, четвертого 83, пятого 84, шестого 85, седьмого 86, восьмого 87, девятого 88, десятого 89, одиннадцатого 90, двенадцатого 91, тринадцатого 92, четырнадцатого 93, пятнадцатого 94, шестнадцатого 95, семнадцатого 96, восемнадцатого 97 элементов И, матрица 98 элементов ИЛИ второго дешифратора 2, состоящая из первого 99, второго-100, третьего 101, четвертого 102, пятого 103, шестого 104, седьмого 105, восьмого 106, девятого 107, десятого 108, одиннадцатого 109 элементов ИЛИ,седьмой 110, третий 111, одиннадцатый 112, пятый 113, десятьп 114, шестой 115, девятый 116, первьй 117 четвертый 118, второй 119, восьмой 120 выходы второго дешифратора 2, цепь 121 разрешения выдачи сигналов с первого дешифратора 1. .

На фиг.5-11 изобралсены временные , диаграммы уровней сигналов на первом 47, втором 48, девятом 49, четвертом 50, пятом 51, третьем 52, i седьмом 53, шестом 54, восьмом 55 входах первого 1 и второго 2 дешифраторов, на седьмом 110, третьем 111, одиннадцатом 112, пятом 113, десятом 114, иестом 115, девятом 116, первом 117, четвертом 118, втором 119, восьмом 120 выходах второго дешифратора 2, третьем 73, пятом 74, четвертом 75,, первом .76, втором 77 и шестом 78 выходах первого дешифратора 1, в цепи 121 разрешения вьщачи сигналов с первого дешифратора 1.

Устройство работает следующим образом.

В вычислительной системе, где требуется введение очередей заданий и заявок на обслуживание, а также осуществление синхронизации процессов через очереди, каждая заявка, задание или процесс имеют свой порядковый номер, начиная с единицы, и данное устройство производит прием,хра- нениё и выдачу в порядке поступления этих номеров (элементов очереди). Кроме того, устройство ведет учет числа элементов, установленных в каждой очереди. Устройство имеет пять режимов работы:

51

1- начальный сброс устройства;

2- постановка элемента в адресуемую -очередь за один цикл записи в устройство;

3- извлечение элемента из адресуемой очереди за один цикл чтения устройства;

4- чтение длины адресуемой очереди ;

5- разрушение (очистка) адресуемой очереди за один цикл записи.

В исходном состоянии, когда нет обращения ЭВМ к устройству, первый дешифратор 1 никаких импульсов записи не вьфабаты вает несмотря на то что на его стробирующий вход поступают импульсы с генератора 8 импульсов через элемент И 9. Второй дешифратор 2 устроен таким образом, что в исходном состоянии он вырабатывает активные уровни сигналов на седьмом, одиннадцатом и четвертом выходах. Активный уровень сигнала с седьмого выхода второго дешифратора 2 удерживает пёрвьй счетчик 3 в нулевом состоянии и последний не реагирует на приходящие импульсы с выхода элемента И 9. Кроме того, активный уровень сигнала с седьмого выхода второго дешифратора 2 по цепи 22 поступает на входы записи первого 39, второго 40, четвертого 41, третьего 42 регистров и на вход записи реверсивного счетчика 44. При .этом содержимое первой информационной шины 20 заносится в регистр 39, содержимое блока 37 .памяти заносится в регистр 40, сигнал с выхода дешифратора 43 записывается в регистр 41, содержимое блока 38 памят заносится в регистр 42 и содержимое блока 45 памяти заносится в реверсивный счетчик 44. Активный уровень сигнала с одиннадцатого выхода второго дешифратора 2 разрешает прием информации с шины 19 адреса данных в первую информационную магистраль 20, активньв уровень с четвертого выхода второго дешифратора 2 разрешает запись информации с первой информационной шины 20 во второй счетчик 4. В этом состоянии устройство будет находиться до тех пор, пока к нему не произойдет обращение от ЭВМ или оно не получит сигнала Сброс по цепи 17 сброса.

Устройство переход11Т в режим начального сброса по включению пи460

талия или по сигналу системного сброса, который поступает па второй вход элемента И 10 по цепи 17 и открывает его. Кроме того, сигнал по це- пи 17 сброса поступает на установочный вход второго счетчика 4 и сбрасывает его в ноль и на адресной шине 21 устройства будет установлен

.- код,равньп 1 нулю. Импульс с генератора 8 импульсов через открытый элемент И 10 поступает на синхровход триггера 11 и устанавливает его в единичное состояние. Второй дешифr ратор 2 устроен таким образом, что при наличии на его девятом входе единичного сигнала с выхода триггера 11, сигналы на всех его выходах, кроме второго, станут пассивными.

Q Активньш сигнал с второго выхода второго дешифратора 2 по цепи 27 поступает на установочный вход реверсивного счетчика 44 и принудительно устанавливает его в ноль. Пас5 сивный сигнал с одиннадцатого выхода второго дешифратора 2 закрывает магистральньш приемник 5 и в первой информационной шине 20 установится код - все нули. Пассивный сигнал с четвертого выхода второго дешифратора 2 прекращает параллельную запись во второй счетчик 4.

ПервьЙ дешифратор 1 устроен таким образом, что при наличии на его девятом входе единичного сигнала с

5 выхода триггера 11 и при поступлении импульса на его стробируюш 1й вход с выхода элемента И 9, он вырабатывает импульсы записи на третьем,# пятом и шестом выходах. Следующий, после

установки триггера 11 в единичное состояние, импульс с выхода генератора 8 импульсов через открытый элемент И 9 (на первом инверсном входе элемента И 9 - низкий уровень сигна5 ла с третьего выхода второго дешифратора 2) поступает на вход строби- рования первого дешифратора 1. Импульсы записи с его шестого и пятого выходов поступают по цепям 29 и 30

0 на входы записи первого 45 и третьего 37 блоков памяти, при этом по нулевому адресу в эти блоки запишутся нули: в блок 45 памяти - с выхода реверсивного счетчика 44; в блок 37

5 памяти - с первой информационной шины 20. Такие циклы записи по одному и тому же адресу будут продолжаться до тех пор, пока с установочного

0

входа второго счетчика 4 не снимается сигнал сброса. При этом второй счетчик 4 переходит в счетный режим Импульс записи с третьего выхода первого дешифратора 1 .поступает на счетный вход второго счетчика 4 и задним фронтом модифицирует его. В адресной шине 21 установится код единицы. Сле 1ующие импульсы записи по цепям 29 и 30 запишут нули в первый 45 и третий 37 блоки памяти уже по следующему адресу очереди и так до тех пор, пока в устройстве не переберутся все адреса, а число адресов равно числу каналов обмена информацией, т.е. числу очередей. - Как только пулевая информация записалась по всем адресам третьего 37 и первого 45 блоков памяти, на выходе переполнения второго счетчика 4 появляется сигнал, который поступает на нулевой вход триггера 11 и сбрасывает его в исходное состояние . Этим заканчивается режим начал ной установки устройства и устройство переходит в исходное состояние Таким образом запись нулей по всем адресам блока 37 памяти означает, что первые элементы всех очередей

нули, т.е. все очереди пустые. Запис нулей по всем адресам блока 45 памяти означает нулевую длину всех очередей .

В исходном состоянии устройство будет находиться до тех пор, пока со стороны ЭВМ по системной магистрали 13 не последует к нему обращение. Каждая очередь в устройстве характеризуется двумя адресами (различие в старших разрядах). По первому ад- .ресу очереди ЭВМ производит постановку или извлечение элемента из очереди, по второму адресу очереди ЭВМ производит чтение количества элементов в очереди или разрушение (обнуление) этой очереди.

Любое обращение ЭВМ к устройству разделяется на два основных цикла работы устройства:

1- начальная выборка устройства;

2- выполнение операции.

Начальная выборка устройства одинакова для всех режимов работы устройства (кроме сброса) . При начальной выборке ЭВМ, обращаясь к -устрой ству, устанавливает на шине 19 адреса данных код адреса устройства, который через магистральный приемник

-

10

15

- 25

20

ь ,

а;

к

5134608

5 и через второй счетчик 4 поступает на дешифратор 7 адреса (старшие разряды) и на адресные входы третьего 37, второго 38 и первого 45 блоков памяти (младшие разряды). Дешифратор 7 адреса при обращении ЭВМ к устройству вырабатывает активньв сигнал на втором выходе в случае, если обращение происходит по первому адресу очереди устройства. Активньй сигнал на первом выходе дешифратора 7 будет в случае обращения ЭВМ к второму адресу очереди. Через некоторое йремя (100-150 не), необходимое для приема и распознования.адреса, ЭВМ активизирует, цепь 16 синхронизации. К этому времени дешифратор 7 адреса определяет адрес обращения к устройству и подает сигнал на седьмые или шестые входы первого 1 и второго 2 дешифраторов. Второй дешифратор 2 с приходом на его третий вход сигнала по цепи 16 синхронизации снимает активный уровень сигнала со своего четвертого выхода, тем самым запрещая прием информации с первой информационной шины 20 во второй счетчик 4. Во втором счетчике 4 зафикси- ровался код адреса обращения, который будет храниться во втором счетчике 4 до тех пор, пока ЭВМ не снимет активный уровень сигнала с цепи 16 синхронизации. Через 100-150 не после установки сигнала в цепи 16 синхронизации ЭВМ снимает код адреса с шины 19 адреса данных и может начать операцию чтения информации из устройства или запись информации из устройства, или запись информации в устройс тво. Дпя чтения информации из устройства ЭВМ активизирует цепь 14 ввойа и ожидает появления информа1щи на шине 19 адреса данных от устройства. Для записи информации в устройство ЭВМ устанавливает информационный код на шину 19 адреса данных и активизирует цепь 15 вывода. Второй дешифратор 2 при наличии сигнала в цепи 16 синхронизации, одного из сигналов с цепей 14 ввода или 15 вывода и одного из сигналов с выхода дешифратора 7 адреса снимает сигнал со своего седьмого выхода. При этом цепь 22 станет пассивной, что приводит к запрету записи информации в первьп 39, второй 40, четвертый 41, третий 42 регистры и в реверсив30

35

40

45

50

- 55

9 , 15

ный счетчик 44. В регистре 39 зафиксируется код с первой информационной шины 20. В регистре 40 зафиксируется код адресуемой ячейки блока 37 памяти. В регистре 41 зафиксируется результат анализа этого кода дешифратором 43. В регистре 42 зафиксируется код адресуемой ячейки блока 38 памяти. В реверсивном счетчике 44 зафиксируется код адресуемой ячейки блока 45 памяти. Кроме того, снятие сигнала с седьмого выхода второго де шифратора1 2 подготавливает первый счетчик 3 к счету и следующий после этого импульс с выхода элемента И 9 своим задним фронтом переведет счетчик 3 из нулевого состояния в первое . На этом цикл начальной выборки устройства закончен. Первый дешифратор 1 в цикле начальной выборки никаких импульсов записи не вырабатывает .

Далее начинается цикл выполнения операции, который происходит по тактам от генератора 8 импульсов.

Рассмотрим режим (операцию) постановки элементов в очередь (т.е. работу одного канала обмена информации) на примере записи по первому адресу очереди устройства элементов с номерами десять, сто и тысяча. Для записи в устройство в нужную очередь элемента с номером десять ЭВМ адресуется к устройству, установив необходимый адрес очереди. После передачи в устройство адреса ЭВМ устанавливает на шину 19 адреса данных код числа десять и активизирует цепь 15 вывода. После цикла на- . чальной выборки счетчик 4 зафиксировал код адреса обращения. Старшие разряды этого кода поступают на дешифратор 7 адреса, который определяет обращение к устройству. Если обращение происходит по первому адресу очереди, то дешифратор 7 адреса устанавливает активньй сигнал на своем втором выходе, который является седььйлм входом первого 1 и второго 2 дешифраторов. Младшие разряды определяют номер очереди и поступают по адресной шине 21 на адресные входы третьего 37, второго 38 и первого 45 блоков памяти и выбирают соответствующие ячейки этих блоков памяти. Причем каждому адресу очереди соответствует одна ячейка памяти, информация из которой зафиксирована

46010

в соответствующем регистре в цикле начальной выборки. Содержимое третьего 37, второго 38 и первого 45 блоков памяти по выбранному адресу зафиксировано соответственно во втором 40, третьем 42 регистрах и в реверсивном счетчике 44. Кроме того, код с выхода блока 37 памяти постуQ пает на дешифратор 43, сигнал с выхода которого зафиксирован в регистре 41 и с выхода последнего поступает на восьмые входы первого 1 и второго 2 дешифраторов. Третий дег шифратор 43 вырабатывает активный сигнал, когда его входной код равен нулю, а это происходит в том случае, если адресуемая очередь пуста. Таким образом, при первом, обращении к

0 адресуемой очереди в цикле начальной выборки в регистре 41 зафиксировался признак пустой очереди, в регистре 40 - код пустой очереди (все нули), в регистре 4 - произвольный

с код,в регистре 39 - код числа 10 с первой информационной пшны 20, а в реверсивном счетчике 44 - код длины очереди, равный нулю. Далее устройство начинает работать по тактам. Первый, после подготовки первого счетчика 3 к счету импульс переводит этот счетчик из нулевого состояния в первое, изменяя код на входах первого 1 и второго 2 дешифраторов. Второй дешифратор 2 состояние своих вы5 ходных сигналов не изменяет, а первый дешифратор 1 при наличии признака пустой очереди (единичный сигнал на его восьмом входе) подготавливается к выдаче сигналов с пятого и четвертого выходов. С приходом второго импульса па стробирующий вход первого дешифратора 1 происходит запись кода числа десять с первой информационной шины 20 в третий 37 и

второй 38 блоки памяти. Конец второго импульса с выхода элемента И 9 переводит счетчик 3 из первого состояния во второе,кроме того задний фронт импульса записи по цепи 31 про изводит прибавление единицы к содер- . жимому реверсивного счетчика 44 и его значение станет равным единице.

Во втором состоянии счетчика 3 дешифратор 2 устанавливает активный

5 сигнал только на своем десятом выходе . Остальные сигналы на выходе дешифратора 2 пассивны. Магистральный приемник 5 при этом закрывается

0

II. 1

Ц в первой информационной тине устаИавливается код нуля, а регистр 39 с ткрывается (активна цепь 23), за- г|исанный в нем коД числа десять г|ерез вторую информационную шину 34 rtocTynasT на .адресные входы буферной памяти 36 и выбирает в нем ячей- ly с адресом десять. С приходом третьего тактового импульса на строби- рующий вход дешифратора 1 (при втором состоянии счетчика 3) последний вырабатывает импульсы записи, ко орые по цепям 29 и 32 поступают, соответственно на вход записи блока -5 памяти и вход записи буферной па- 1ШТИ 36. При этом произойдет запись нуля с первой информационной шины :Ю по адресу, равному десяти, в бу(}ернута память 36 и запись единицы с выхода реверсивного счетчика 44 :з блок 45 памяти по адресу очереди. Задний фронт третьего импульса пере- ;зедет первый счетчик 3 в третье со- :тояние, при которой дешифратор 2 вы :}абатывает сигнал в цепь 18 ответа, указывая этим сигналом ЭВМ о завер- иен1ш операции. Кроме того, сигнал : цепи 18 поступает на инверсный вход элемента И 9 и закрывает его Зледуюпще импульсы с генератора 8 н :;четчик 3 и дешифратор 1 поступать не будут. Устройство будет находить в таком состоянии до тех пор, пока ВМ, получив сигнал по цепи 18 отве |та, не снимет сигналы с цепи 15 вы- рода и цепи 16 синхронизации начала операции. После этого устройство пе рейдет в исходное состояние. Таким юбразом,после первого цикла записи |числа десять в устройство, блок 37 ;памлти будет хранить код числа деся п6 адресу очереди, как код первого элемента очереди, блок 38 памяти бу , дет хранить по адре.су очереди код гшсла десять как код последнего эле ;мента очереди, блок 45 памяти будет кранить по адресу очереди единицу как признак того, что в адресуемой очереди находится один элемент, а буферная память 36 будет хранить (по адресу десять) ноль как ссылку на то, что за элементом с номером десять следующего элемента нет.

Для установки, следующего элемент (с номером сто) в эту же очередь ЭВМ, как и в первом случае, адресуется к этой очереди с опера- цией Запись. При этом дешиф

0

20

460

25

12

ратор 2, как и в первом случае., снимает сигналы со своих седьмого и четвертого выходов и подготавливает счетчик 3 к счету.После начальной выборки регистр 40 зарегистрирует код первого элемента очереди, т.е. десять, регистр 41 зарегистрирует отсутствие пустой очереди, так как на входе дешифратора 43 код не равен нулю, регистр 42 зафиксирует код последнего элемента очереди, т.е. тоже десять, регистр 39 зафиксирует код элемента с пер- вой информационной шины 20, т.е. код числа сто, а в реверсивном счетчике 44 зафиксируется код числа один. Задний фронт первого тактового импульса с выхода генератора 8 через открытый элемент И 9 переведет счетчик 3 из нулевого состояния в первое. Так как в данном случае сигнал в цепи 35 отсутствует (очереди не пуста), дешифратор 2 устанавливает активные сигналы на своих одиннадцатом и девятом выходах, при этом регистр 42 открывается (цепь 25 активна) и код последнего элемента

очереди, т.е. код числа десять, поступает через вторую информационную шину 34 на адресньй вход буферной памяти 36 и выбирает ячейку с адресом десять, которая хранит число ноль. Первый дешифратор 1 устроен так, что в случае записи в непустую очередь и при единичном состоянии счетчика 3 с приходом тактового импульса с выхода элемента И 9 он вырабатывает импульсы записи в цепях 31 32. При этом в блок 38 памяти по адресу очереди и в буферную память 36 по адресу десять с первой информационной шины 20 запишется код числа сто. Одновременно с записью в блок 38 памяти произойдет прибавление единицы к содержимому реверсивного счетчика 44, т.е. код, хранимый этим счетчиком, станет равным двум. Задний фронт второго тактового импульса переведет счетчик 3 из первого состояния во второе,В этом случае и дешифратор 2 закроет регистр 42 и.

5

как в предыдущем примере, закроет магистральный приемник 5 и откроет регистр 39, а с приходом третьего 55 тактового импульса первый дешифратор 1 по цепям 32 и 29 произведет запись нуля с первой информационной шины 20 в буферную память 36 по ад131

ресу, равному ста,, из регистра 39, запись двойки в блок 45 памяти из реверсивного счетчика 44. По концу третьего импульса счетчик 3 перейде в третье состояние, при котором дешифратор 2 установит сигнал в цепь

18ответа и закроет элемент И 9. Ка только ЭВМ снимет сигналы с цепи 16 синхронизации и с цепи 15 вывода, устройство перейдет в исходное состояние. Теперь блок 37 памяти хранит код первого элемента - десять, блок 38 памяти хранит код последне - го элемента - сто, блок 45 памяти хранит код числа два как признак того, что в адресуемой очереди хранятся два элемента. Буферная память 36 по адресу первого элемента хранит код сто как ссылку на то, что следующий после элемента с номером десять установлен элемент с номером сто, а по адресу сто хранит код . нуля, как признак того, что за этим элементом в очереди других элементо нет.

Для установки в эту же очередь третьего элемента с номером тысяча ЭВМ адресуется к этой очереди с операцией Запись, установив на шине

19адреса данных код третьего-элемента очереди - тысяча. Работа устройства в этом случае будет аналогина работе при установке второго элемента в очередь. Отличие будет только в том, что после цикла начальной выборки в регистре 42 зафиксируется код числа сто, в регистре 39 - код числа тысяча, а в реверсивном счетчике 44 - код числа элементов в очереди - два. Во время второго тактового импульса произойдет запись по адресу, равному ста, из регистра

42 кода числа тысяча с первой информационной шины 20 в буферную память 36 и по .адресу очере щ в блок 38 памяти. Одновременно увеличится на единицу содержимое реверсивного счетчика 44, По третьему тактовому импульсу в блок 45 памяти по адресу очереди будет записан код три - содержимое реверсивного счетчика 44,а в буферную память 36.no адресу тысяча - ноль. Таким образом, для адресуемой очереди после трех циклов записи в устройство блок 37 памяти хранит код числа тысяча, блок 45 памяти код числа три, а буферная память 36 хранит по адресу десять код

346014

числа сто, по адресу сто - код тыся-. чн, по адресу тысяча- - код нуля.

Аналогичным образом работает любой другой канал обмена информацией,

Для извлечения элемента очереди из канала обмена информацией ЭВМ адресуется к нужной очереди с операцией чтения, в результате чего ройство вьщает в ЭВМ код первого элемента очереди. Вьщача нуля в ЭВМ означает, что данная очеред пуста,

Режим извлечения элемента из очереди рассмотрим на примере работы то1 го же канала обмена информацией, что и в режиме постановки в очередь,

В режиме извлечения элемента из очереди ЭВМ адресуется к нужной очереди с операцией чтения, при этом,

20 как и при записи, дешифратор 2 по сигналу с цепи 16 синхронизации начала операции фиксирует адрес обращения в счетчике 4, а по сигналу в цепи 14 ввода производит фиксацию

25 состояния регистров, при этом регистр 40 хранит код первого элемента очереди - десять, регистр 41 - признак непустой очереди (код десять не равен нулю), реверсивный счетчик 44 - код длины очереди - три. Регистры 39 и 42, а также магистраль- ньвг приемник 5 и передатчик 46 в выполнении операции Чтение из устройства участия не принимают и соответствующими сигналами с выходов

35 дешифратора 2 на время вьшолнения этой операции закрыты. После фиксации информации в регистрах сигналом с седьмого выхода второго дешифратора 2 разблокируется счетчик 3 и вый после этого импульс с генератора 8 через элемент И 9 переведет этот счетчик из нулевого состояния в первое. При этом состоянии счетчика 3 и при наличии активных сигналов в

45 цепи 16 синхронизации начала операции в цепи 14 ввода информации, а также признака непустой очереди в цепи 33 с выхода регистра 41,. дешифратор 2 устанавливает активные уров-

50 ни сигналов на своих шестом, первом и пятом выходах, которые поступают соответственно на разрешающие входы регистра 40, буферной памяти 36 и второй вход магистрального передат-

55 чика 6, Сигнал по цепи 24 с шестого выхода второго дешифратора 2 открывает выход регистра 40, информация из которого (код десять) посту30

15151

|тает по второй информа1даонной шине 34 па вход магистрального передат- Цика 6 и на адресньв вход буферной Ьамяти 36. Сигнал с первого выхода фторого дешифратора 2 по цепи 26 1|)азрешает вьщачу информации из буферной памяти 36 в первую информационную шину 20, при этом на информационный вход блока 37 памяти с вы- хода буферной памяти 36 поступает код числа сто, которьш хранится по с1дресу десять, установленному на лторой информационной шине 34 с ре- з-истра 40. Сигнал с пятого выхода нторого дешифратора 2 открывает ма- з-истральпый передатчик 6 и информа- з(ия (код числа десять) с выхода ре- wcTpa 40 поступает на шину 19 адреса данных.

Первый дешифратор 1, при той же комбинации сигналов на своих адресных входах, с приходом второго тактового импульса вырабатывает сигналы ;|аписи в цепях 30 и 33. Сигнал с пя- ого выхода дешифратора 1 по цепи ;0 произведет запись информации в (шок памяти, в данном случае код числа сто. Сигнал с второго выхода де- нифратора 1 по цепи 33 произведет иычитание единицы из содержимого ре- ерсивного счетчика 44. Таким обра- :(ом, в реверсивном счетчике 44 будет :срамиться код числа два. Задний оропт второго импульса с выхода элемента И 9 переведет счетчик 3 во вто )ое- состояние. В этом состоянии де- 1 1ифратор 2 не меняет комбинации свои выходных сигналов, а дешифратор 1 {; приходом третьего импульса выраба- jrbiBaeT сигнал записи на своем шестом зыходе. Этот сигнал по цепи 29 за- йосится в блок 45 памяти код числа Два с выхода реверсивного счетчика 44. По концу третье.го импульса с выхда элемента И 9 счетчик 3 переходит р третье состояние. В этом состоявши дешифратор 2, в дополнение к уже установленным сигналам, устанавливает сигнал на своем третьем выходе. Этот сигнал поступает на вход элемента И 9 и закрывает его, кроме того, этот сигнал по цепи 18 ответа Извещает ЭВМ о завершении операции Чтение устройства ЭВМ, получив сиг Нал по цепи 18 ответа, считывает код с шины данных и убирает сигналы обращения . Устройство переходит в исходное состояние. После операции Чтени

j

5

0

16

устройства блок 37 памяти хранит код числа сто, как код первого элемента очереди (элемент с номером десять уже взят из очереди), а блок 45 памяти хранит код числа два, т.е. в адресуемой очереди находится два элемента.

При втором чтении той же очереди устройство срабатывает аналогичным образом с той лишь разницей, что в момент обращения регистр 40 зафиксирует код числа сто, а реверсивный счетчик 44 - код числа два. Второй тактовый импульс запишет в блок 37 памяти содержимое буферной памяти 36, т.е. код числа- тысяча, которьш буферная память 36 хранит по адресу сто, и уменьшит состояние реверсивного счетчика 44. Третий тактовый импульс запишет в блок 45 памяти код единицы с выхода реверсивного счетчика 44. Аналогично произойдет и третий цикл чтения этой же очереди, при котором устройство выдаст в ЭВМ код числа тысяча. Во время третьегр цикла чтения второй тактовый импульс запишет в блок 37 памяти код числа ноль с выхода буферной памяти 36, так как по адресу тысяча в последнем цикле записи в устройство в буферную память 36 был записан ноль. Третий тактовьш импульс запишет в блок 45 памяти нулевую дпину с выхода реверсивного счетчика 44. В случае четвертого цикла чтения этой же очереди (а очередь пуста) .при обращении ЭВМ к устройству регистр 40 зафиксирует код, равный нулю, с вьгхода блока 37 памяти, а регистр 41 зафиксирует признак пустой очереди с выхода дешифратора 43. В этом случае после первого тактового импульса, когда счетчик 3 перейдет в первое состояние, дешифратор 2 установит сигналы на пятом, шестом и третьем своих выходах, закрыв тем самым элемент И 9 и послав сигнал в цепь 18 ответа, при этом через открытый магистральный передатчик 6 в шину 19 адреса данных поступит код нуля с выхода регистра 40. ЭВМ, получив сигнал ответа, считывает данные с шинь 19 адреса данных. Программное обеспечение ЭВМ построено таким образом, что прочитанный ноль из адресуемой очереди воспринимается как признак того, что данная очередь пуста.

Таким образом, с помощью данного устройства ЭВМ или группа ЭВМ могут вести очереди заданий и заявок па обслуживание, обмениваясь при этом номерами этих заявок или заданий. Такое устройство наиболее эффективно при конвеериой обработке заявок или заданий в мультипроцессорных системах с большим числом очередей на обработку между различными процессами.

Устройство позволяет ЭВМ работат с очередями за один цикл обращения (записи или чтения); поэтому конфликтных ситуаций в этом случае в мультипроцессорных системах не произойдет, так как одновременный доступ к одному и тому же ресурсу системы от двух и более ЭВМ предотвращает системньш арбитр.

На практике в ряду мультипроцессорных систем возникает необходимос знать число элементов той или иной очереди. Для этой цели в устройстве предусмотрен режим чтения длины очереди.

Для получения текущей длины очереди ЭВМ адресуется к данной очеред но по второму адресу этой очереди с операцией чтения. Как и в предыдущих случаях в цикле начальной выборки в устройстве фиксируются адре в счетчике 4 и содержимое третьего 37, второго 38 и первого 45 .блоков памяти. Дешифратор 7 адреса, определив, что обращение осуществляется по второму адресу очереди , а не по первому, устанавливает сигнал на своем первом выходе, который является шестым входом первого 1 и второго 2 дешифраторов. После цикла начальной выборки устройства, когда первый импульс переведет счетчик 3 из нулевого состояния в первое, дешифратор 2 устанавливает активные сигналы на пятом, третьем и восьмом выходах. Сигнал с восьмого выхода дешифратора 2 по цепи 28 открьшает передатчик 46. Информация о длине адресуемой очереди, зафиксированная в реверсивном счетчике 44, через передатчик 46 поступает на вторую информационную шину 34 и по ней на вход магистрального передатчика 6. Сигнал с пятого выхода второго дешифратора 2 поступает на разрешаю- вход магистрального передатчика 6 и открывает его. Информация

0

5

0

5

о длине адресуемой очереди с второй информационной шины 34 через открытый магистральный передатчик 6 поступает в шину 19 адреса данных. Сигнал с третьего выхода депифрато- ра 2 блокирует прохождение следующих импульсов с генератора 8 на счетный вход счетчика 3. Кроме того, этот сигнал по цепи 16 ответа указывает ЭВМ, что устройство требуемую операцию выполнило. ЭВМ счи- тьшает код длины и снимает сигналы обращения. Устройство переходит в исходное состояние. Дешифратор 1 в этом режиме никаких сигналов не вырабатывает и информация, хранимая в трех блоках памяти и буферной,памяти, не изменяется. Иногда в процессе работы вычислительной системы возникает необходимость разрушить какую- либо очередь, ЭВМ принявшая решение об разрушении какой-либо очереди, может очистить ее путем мно- , гократного чте1шя данной очереди до тех пор, пока не прочтет из устройства ноль как признак пустой очереди. Но к этой очереди в интервалах между чтениями может обратиться другая ЭВМ. Для предотвращения такой ситуации в устройстве предусмотрен режим разрушения очереди за один цикл обращения. Для этого ЭВМ адресуется по второму адресу очереди к нужному номеру очереди с опера- 5 цией Запись. Как и при любом обращении к устройству дешифратор 2 вырабатывает сигнал для фиксации ин- формации в регистрах и разрешает работу счетчика 3. Конец первого тактового импульса переводит счетчик 3 из нулевого состояния в первое. Дешифратор 2 при первом состоянии счетчика 3, при наличии сигнала на цепи 15 вывода и цепи 16 синхро- 5 низации и наличии сигнала на первом выходе дешифратора 7 адреса, как и в режиме начальной установки, -снимает сигналы со всех своих выходов, кроме второго. Сигнал с второго вы- 0 хода дешифратора 2 поступает по цепи 27 на установочный вход реьерсив- ного счетчика 44 и устанавливает его в ноль. Второй тактовый импульс с выхода элемента И 9 поступает на 5 стробирующий вход дешифратора 1, который формирует импульсы записи на цепях 29 Н 30. Импульс в цепи 30 производит запись нуля с первой ин0

0

19

формациоинон шины 20 в блок 37 памя |ги, а импульс в цепи 29 - с выхода реверсивного счетчика 44 в блок 45 Ьамяти. По концу второго импульса с :зыхода элемента И 9 счетчик 3 пере- :содит во второе состояние, в кото- )ом дешифратор 2 устанавливает сигнал в цепь 18 ответа и этим сигна- jroM закрывает элемент И 9. ЭВМ, по- лгучив сигнал по цепи 18 ответа, снимает свои сигналы обращения. Уст-. 1ЮЙСТВО переходит в исходное состояние. Таким образом, ЭВМ за один цикл записи обнулит адресуемую очередь. И теперь при чтении этой очереди по первому адресу ЭВМ получит 1;оль как признак пустой очереди, а i:o второму адресу ЭВМ прочтет нуле- гую длину очереди. Очевидно, что количество адресуемых очередей (ка- i. 1алов обмена информацией) в устрой- с тве зависит от объема блоков ОЗУ, с быстродействие - от типа элементной базы и частоты тактового генератора. Так, третий 37 и первый 45 блоки памяти должны содержать столь- KJO слов, сколько необходимо каналов с|бмена информацией, а буферная па- ять 36 должна содержать столько слов, сколько элементов может быть выстроено в одну очередь. Частота генератора 8 импульсов выбирается из у1словия, что длительность импульса должна быть достаточной дпя надежной записи информации в блоки памяти, а длительность паузы должна учитывать время срабатывания дешифраторов и время выборки адреса блоков памяти. : Описанное устройство для обмена и 1формацией используется в макетах многопроцессорной вычислительной си- с1гемы,предназначенной для построения н|а ее основе коммуникационных ком- п|1ексов вычислительной сети и сети передачи данных с коммутацией па- . Многопроцессорная вычислительная система представляет собой параллельно работающих ЭВМ Электроника 60, имеющих свое ОЗУ и имеющих окно на выход в шину общего доступа, к которой подклю- странично организованная память П()оцессов, странично организованная данных и адаптеры внешних свя- , и устройство для обмена инфор- , называемое контроллером списков, которое является аппаратной шЬддержкой специально разработанto

15

20

25

1513460.20

ной операционной системы. Все страницы общей памяти имеют сквозную нумерацию. Операционная система построена таким образом, что каждый процессор системы, закончив выполнение оче-, редного задания, ставит это задание (т.е. номер этого задания) в очередь и берет из очереди следующее. Таким образом, любой процессор системы может выполнять любое задание. Параллельно выполняется столько заданий, сколько работает процессоров. Каждый процессор, работая со страницами памяти данных, отработав свою часть информации, ставит эту страницу (номер этой страницы) в очередь на обработку в тот или иной процесс, и из своей входной очереди берет следующую информацию на обработку. Таким образом, достигается конвеерная обработка информации и синхронизации процессов в мультипроцессорной среде.

Устройство для обмена информацией в макетах вычислительной системы позволяет поддерживать 512 оче-J редей с 1023 элементами очереди. Поэтому объем третьего 37, второго 38 и первого 45 блоков памяти составляет 512 X 10 бит каждый, а объем буферной памяти 36 составляет 1024 X 10 бит.

В мультипроцессорной системе устройство для обмена информацией

35 имеет следующие адреса: 154000g - 155776g - для операций с постановкой и извлечением из очереди (первые адреса очереди); 156000j - 15777 - для операций чтения длины

40 очереди и разрушения очереди (вторые адреса очереди).

Длительность цикла постановки в очередь или извлечения из очереди составляет 4-5 мкс (для ЭВМ

45 Электроника-60), а длительность чтения длины очереди или ее разрушения составляет 3-3,5 мкс, т.е. такая же, как и длительность чтения (записи) обычной ячейки памяти.

50 Дешифраторы 1 и 2 устроены и работают следующим образом.

Первый - девятьй входы первого дешифратора параллельно соединены с соответствующими входами второго

55 дешифратора и соединены со следующими элементами устройства:

входы .47 и 48 соединены с первым и вторым выходами счетчика 3;

30

21 ,

вход 49 дешифраторов соединен с выходом триггера 11 и является входом, инициирзпощим перевод дешифраторов в режим сброса;

вход 50 дешифраторов соединен с цепью Ввод устройства и является входом, инициирующим чтение из устройства;

вход 51 дешифраторов соединен с цегйзю Вывод устройства и является входом, инициирующим запись в устройство;

вход 52 дешифраторов .соединен с цепью синхронизации и является входом, сигнализирующим об обращении ЭВМ к устройству;

вход 53 дешифраторов соелинен с вторым выходом дешифратора 7 адреса и является входом обращения к устройству по первому адресу очереди;

вход 54 дешифраторов соединен с первым выходом дешифратора 7 адреса и является входом обращения к устройству по второму адресу очереди;

вход 55 дешифраторов соединен с выходом регистра 41, в котором при обращении к устройству фиксируется признак пустой очереди-(55 ф - адресуемая очередь.не пустая 55 1 - адресуемая очередь пустая)

Сигналы, поступаюп е на первьй - девятый входы первого и второго дешифраторов, инвертируются в соответствующих группах элементов НЕ 56 и поступают вместе с прямьми сиг- иалами в.матрицу 5 7 элементов И дешифратора t и матрицу 79 элементов И дешифратора 2,

Матрица 79 элементов И дешифратора 2 предназначена для анализа состояния сигналов на входах 47-55} - соответствующих определенному режиму, циклу работы или состоянию, устройства.

Сигнал на выходе первого элемента И 80 появляется при комбинации сигналов на входах 47-55, соответствующей режиму Сброс устройства, т.е. тогда, когда появится активный сигнал на входе 49 дешифратора независимо от уровня сигналов на остальных его входах.

Сигнал с выхода первого элемента И 80 поступает на вход десятого 108 элемента ИЛИ матрицы 98.

Сигналы с выходов остальных элементов И матрицы 79 могут появить10

20

25

3460 . 22

ся только при отсутствии сигнала на

входе 49 дешифратора.

Сигнал на выходе второго элемента И 81 появляется при комбинации 5 сигналов на входах 47-55, соответствующей исходному состоянию устройства, т.е. при отсутствии обра- щеш1Я к устройству со стороны ЭВМ (нет сигнала на входе 52).

Сигнал с выхода второго элемента И 81 поступает на входы первого 99, третьего 101 и девятого 107 элементов ИЛИ матрицы 98.

Сигнал на выходе третьего элемента И 82 появляется при комбинации сигналов на входах 47-55,соответствующей началу цикла обращения ЭВМ к устройству, т.е. сигнал об обращении к устройству от ЭВМ поступил (52 1), но нет еще признака типа инициируемой операдаи - чтения (50 0) или записи (51 0).

Сигнал с выхода третьего элемента И 82 поступает на входа 1 первого 99 и третьего 101 элементов ИЛИ матрицы 98.

Сигнал на выходе четвертого элемента И 83 появляется при комбинации сигналой на входах 47-55, соот- 3 ветствующей циклу начальной выборки устройства (47 0, 48 ) при обращении к устройству (52 1) с операцией записи (50 0, 51 1) по первому адресу очереди (53 0, 35 54 - 0), что соответствует режиму постановки элемента в очередь.

Сигнал с выхода четвертого элемента И 83 поступает на вход третьего 101 элемента ИЛИ матрицы 98. 40 Сигнал на выходе пятого элемента И 84 появляется при комбинации сигналов на входах 47-55, соответствующей первому состоянию (47 1, 48 0) операции записи в устройство 45 (50 0, 51 1, 52 1) по первому адресу очереди (53 1, 54 0), и при наличии признака пустой очереди (55 1), что соответствует режиму постановки элемента в пустую оче- 50, редь.

Сигнал с выхода пятого элемента И 84 поступает на вход третьего 101 элемента ИЛИ матрицы 98.

Сигнал на выходе шестого элемен- 55 та И 85 появляется при комбинации сигналов на входах 47-55, соответ- .ствующей .второму состоянию (47 0, 48 1) операции записи в устрой- ство (50 0 , 51 1. 52 1) по

23

5Д

nopBONry адресу очереди (53 1, 0), Что соответствует режиму постановки элемента в очередь.

Сигнал с выхода шестого элемента И 85 поступает на вход пятого 103 элемента ИЛИ 98 матрицы.

Сигнал на выходе седьмого элемента И 86 появляется при комбина- гщн сигналов на входах 47-55, соответствующей третьему состоянию (47 1, 48 1) операции записи в устройство (50 0, 51 1, 52 1) по первому адресу очереди (53 1, 34 ), что соответствует режиму постановки элемента в очередь.

Сигнал с выхода седьмого элемента И 86.поступает на вход второго

100элемента ИЛИ матрицы 98,

. Сигнал на выходе восьмого элемента И 87 появляется при комбинации сигналов на входах 47-55, соответствующей первому состоянию (47 1, 48 0) операции записи в устройство (50 0 51 1, 52 1) по первому адресу очереди (53 1, 54 - 0), что соответствует режиму постановки элемента в непустую очередь.

Сигнал с выхода восьмого элемента И 87 поступает на вход третьего

101и восьмого 105 элемента ИЛИ матрицы 98.

Сигнал на выходе девятого элемента И 88 появляется при комбинации сигналов на входах 47-55, соответствующей циклу начальной выборки устройства (47 - 0, 48 0) при об- |ращении к устройству (52 1) с операцией чтения из устройства (50 1, 51 (2, 52 1) по первому адресу очереди (53 1, 54 0), что соответствует режиму извлечения элемента из очереди.

Сигнал с выхода девятого элемента И 88 поступает вход третьего 101 элемента ИЛИ матрицы 98.

Сигнал на выходе десятого элемента И 89 появляется при комбинации сигналов на входах 47-55,соответствующей первому состоянию (47 1, 48 ) операции чтения из устройства (50 1, 51 0, 52 1) по первому адресу очереди (53 1, 54 ) и при отсутствии признака пустой очереди (55 0), что Соответствует режиму извлечения элемента из. непустой очереди.

Сигнал с выхода десятого элемента И 89 поступает на входы четвертого

151346024

102, шестого 104 и восьмого 106 йле10

15

20

25

30

ментов ИЛИ матрицы 98.

Сигнал на выходе одиннадцатого элемента И 90 появляется при комбинации сигналов на входах 47-55, соответствующей второму состоянию (47 i , 48 1) операции чтения из устройства (50 1, 51 -0, 52 1) по первому адресу очереди (53 1, 54 ) и при отсутствии признака пустой очереди (55 (2), что соответствует режиму извлечения эле- ента из непустой очереди.

Сигнал с выхода одиннадцатого элемента И 90 поступает на входы четвертого 102, шестого 104 и восьмого 106 элементов ИЛ.И матрицы 98.

Сигнал на выходе двенадцатого элемента И 91 появляется при комбинации сигналов на входах 47-55, соответствующей третьему состоянию (47 1, 48 1) операции чтения из устройства (50 1, 51 , 52 1) по первому адресу очереди (53 1, 54 0) и при отсутствии признака пустой очереди (55 0), что соответствует режиму извлечения элемента из не:пустой очереди.

Сигнал с выхода двенадцатого элемента И 91 поступает на входы второго 100, четвертого 102, шестого 104 и восьмого 106 элементов ИЛИ матрицы 98.

Сигнал на выходе тринадцатого эле- мента И 92 появляется при комбинации сигналов.на входах 47-55, соответствующей первому состоянию (47 1, 48 0) операции чтения из устройства (50 1, 51 , 52 1) по первому адресу очереди (53 1, 54 Z) и при наличии признака пустой очереди (55 1), что соответствует режиму извлечения -элемента из пустой очереди.

Сигнал с выхода тринадцатого элемента И 92 поступает на входы второ- гр 100, четвертого 102 и шестого 104 элементов ИЛИ матрицы 98.

Сигнал на выходе четырнадцатого элемента И 93 появляется при комбинации сигналов на входах 47-55,соответствующей циклу начальной выборки . устройства (47 0, 48 0) при обращении к устройству (52 1) с опе- 55 рацией чтения (50 1, 51 0) по второму адресу очереди (53 0, 54 1), что соответствует режиму чтения длины очереди.

40

45

50

5

0

5

0

ментов ИЛИ матрицы 98.

Сигнал на выходе одиннадцатого элемента И 90 появляется при комбинации сигналов на входах 47-55, соответствующей второму состоянию (47 i , 48 1) операции чтения из устройства (50 1, 51 -0, 52 1) по первому адресу очереди (53 1, 54 ) и при отсутствии признака пустой очереди (55 (2), что соответствует режиму извлечения эле- ента из непустой очереди.

Сигнал с выхода одиннадцатого элемента И 90 поступает на входы четвертого 102, шестого 104 и восьмого 106 элементов ИЛ.И матрицы 98.

Сигнал на выходе двенадцатого элемента И 91 появляется при комбинации сигналов на входах 47-55, соответствующей третьему состоянию (47 1, 48 1) операции чтения из устройства (50 1, 51 , 52 1) по первому адресу очереди (53 1, 54 0) и при отсутствии признака пустой очереди (55 0), что соответствует режиму извлечения элемента из не:пустой очереди.

Сигнал с выхода двенадцатого элемента И 91 поступает на входы вто рого 100, четвертого 102, шестого 104 и восьмого 106 элементов ИЛИ матрицы 98.

Сигнал на выходе тринадцатого эле- мента И 92 появляется при комбинации сигналов.на входах 47-55, соответствующей первому состоянию (47 1, 48 0) операции чтения из устройства (50 1, 51 , 52 1) по первому адресу очереди (53 1, 54 Z) и при наличии признака пустой очереди (55 1), что соответствует режиму извлечения -элемента из пустой очереди.

Сигнал с выхода тринадцатого элемента И 92 поступает на входы второ- гр 100, четвертого 102 и шестого 104 элементов ИЛИ матрицы 98.

Сигнал на выходе четырнадцатого элемента И 93 появляется при комбинации сигналов на входах 47-55,соответствующей циклу начальной выборки . устройства (47 0, 48 0) при обращении к устройству (52 1) с опе- 55 рацией чтения (50 1, 51 0) по второму адресу очереди (53 0, 54 1), что соответствует режиму чтения длины очереди.

0

45

50

251

Сигнал с выхода четырнадцатого элемента И 93 поступает на вход третьего 101 элемента ИЛИ матриць 98.

Сигнал на выходе пятнадцатого элемента И 94 появляется при комбинации сигналов на входах 47-55, соответствующей первому состоянию (47 1, 48 ) операции чтения из устройства (50 1, 51. 0, 52 1) по второму адресу очереди (53 0, 54 1), что соответствует режиму чтения дпины очереди.

Сигнал с выхода пятнадцатого элемента И 94 поступает на входы второг 100, четвертого 102 и одиннадцатого 109 элементов ИЛИ матрицы 98.

Сигнал на выходе шестнадцатого элемента И 95 появляется при комбинации сигналов на входах 47-55, соответствующей циклу начальной выборки устройства (47 0, 48 0) при обращении к устройству (52 1) с операцией записи (50 0, 51 1) по второму адресу очереди (53 0, 54 1), что соответствует режиму разрушения очереди.

Сигнал с выхода шестнадцатого элемента И 95 поступает на вход третьего 101 элемента ИЛИ матрицы 98.

Сигнал на выходе семнадцатого элемента И 96 появляется при комбинации сигналов на входах 47-55, соответствующей первому состоянию (47 1, 48 0) операции записи в устройство (50 , 51 1, 52 1) по второму адресу очереди (53 0 , ,54 1), что соответствует режиму разрушения очереди.

Сигнал с выхода семнадцатого элемента И 96 поступает на вход десятого 108 элемента ИЛИ. матрицы.98.

Сигнал на выходе восемнадцатого элемента И 97 появляется при комбинации сигналов на входах 47-55, соответствующей второму состоянию (47 0, 48 1) операции записи в устройство. (50 0, 51 1., 52 1) по второму адресу очереди (53 0, 54 1), что соответствует режиму разрушения очереди.

Сигнал с выхода восемнадцатого элемента И 97 поступает на вход второго 100 элемента ИЛИ матрицы 98.

Матрица 98 второго дешифратора предназначена для получения сигналов Vщ aвлeния на выходах 110-120 при наличии определенных условий на ее входе.

346026

Сигнал с выхода 110 второго дешифратора предназначен для разрешения записи информации с первой информационной шины 20 устройства в регистр 39; с выхода блока 37 памяти - в регистр 40; признак пустой очереди с выхода дешифратора 43 - в регистр 41; с выхода блока 38 памяQ ти - в регистр 42 и с выхода блока 45 памяти - в реверсивный счетчик 44. Кроме того, сигнал с выхода 110 дешифратора 2 сбрасывает счетчик 3 в нулевое состояние.

Сигнал на выход 110 дешифратора 2 поступает с выхода первого 99 элемента ИЛИ матрицы 98 при условии наличия сигналов с выхода второго ИЛИ 81 и третьего 82 элементов И ма0 трицы 79.

Сигнал с выхода 111 дешифратора 2 предназначен для выдачи ответа в ЭВМ о завершении текущей операции. Кроме того, этот сигнал закрьшает

5 элемент И 9 и сигналы с выхода генератора не поступают на входы счетчика 3 и дешифратора 1.

Сигнал на выход 111 дешифратора 2 поступает с выхода второго 100 эле0 мента ИЛИ матрицы 98 при условии наличия сигналов с выхода седьмого ИЛИ 86, двенадцатого 91 или тринадцатого 92, или пятнадцатого 94, или восемнадцатого 97 элементов И матрицы 79.

Сигнал с выхода 112 дешифратора 2 предназначен для разрешения приема адреса данных из системной магистрали в первую информационную шину 20 устройства через магистральный приемник 5.

Сигнал на выход 112 дешифратора 2 поступает с выхода третьего 101 элемента ИЛИ матрицы 98 при условии наличия сигналов с выхода второго 81 или третьего 82, или четвертого 83, или пятого 84, или восьмого 87, или девятого 88, или четырнадцатого 93, или шестнадцатого 95 элементов И матрицы 79.

Сигнал с выхода 113 дешифратора 2 предназначен для разрешения выдачи данных с второй информационной шины 34 устройства в системную магистраль через магистральньш пере датчик 6.

Сигнал на выход 113 дешифратора 2 поступает с выхода четвертого 102 элемента ИЖ матрицы 98 при условии

5

0

5

0

наличия сигналоэ с выхода десятого 89 или одиннадцатого 90, или двенадцатого 91, или тринадцатого 92, или пятнадцатого 9А элементов И матрицы 79.

Сигнал с выхода 114 дешифратора 2 предназначен для разрешения вьщачи данных, хранящихся в регистре 39 устройства, во вторую информагщон- ную шину 34.

Сигнал на выход 114 дешифратора 2 поступает с выхода пятого 103 элемента ИЛИ матрицы 98 при условии наличия сигнала с выхода шестого 85 элемента И матрицы 79.

Сигнал с выхода 115 дешифратора 2 предназначен для разрешения вы-. дачи данных, хранящихся в регистре 40 устройства, во вторую информационную шину 34.

Сигнал на выход 115 дешифратора 2 поступает с выхода шестого 104 элмента ИЛИ матрицы 98 при условии наличия сигналов с выхода десятога 89 или одиннадцатого 90, или двенадцатого 91, или тринадцатого 92 элемента И матрицы 79. I Сигнал с выхода 116 дешифратора 2 предназначен для разрешения выдач данных, хранящихся в регистре 42 ус I ройства, во вторую информационную I шину 34. Сигнал на выход 116 депшфратора I2 поступает с выхода седьмого 105 I элемента ИЛИ матрицы 98 при условии наличия сигнала с выхода восьмого I87 элемента И матрицы 79. i Сигнал с выхода 117 депшфратора I2 предназначен для разрешения выда- чи данных, хранящихся в буферной памяти 36 устройства, в первую информационную шину 20.

Сигнал на выход 117 дешифратора 2 поступает с выхода восьмого 106 элемента ИЛИ матрицы 98 при условии наличия сигналов с выхода десятого 89 или одиннадцатого 90, или двенадцатого 91 элемента И матрицы 79. Сигнал с выхода 118 дешифратора 2 предназначен для разрешения записи информации с первой информационной шины 20 устройства в счетчик 4. Сигнал на выход 118 дешифратора 2 поступает с.выхода девятого 107 элемента ИЛИ матрицы 98 при условии наличия сигнала с выхода второго 81 элемента И матрицы 79.

0

5

0

5

0

5

0

55

Сигнал с выхода 119 дешифратора 2 предназначен для сброса реверсивного счетчика 44 устройства в нулевое состояние.

Сигнал на выход 119 дешифратора 2 поступает с выхода десятого 108 элемента ИЛИ матрицы 98 при условии наличия сигналов с выхода первого 80 или семнадцатого 96 элементов И матрицы 79.

Сигнал с выхода 120 дешифратора 2 предназначен для разрешения вьодачи данных с выхода реверсивного счет- чйка 44 устройства во вторую информационную шину 34 через передатчик 46. .

Сигнал на выход 120 дешифратора 2 поступает с выхода одиннадцатого 109 элемента ИЛИ матрицы 98 при условии наличия сигнала с выхода пятнадцатого 94 элемента И матрицы 79.

Матрица 57 элемента И дешифратора 1 имеет такое же назначение, как и матрица 79 элементов И дешифратора 2.

Сигнал на выходе первого элемента И 58. матрицы 57 элементов И дешифратора 1 вырабатывается по такому же условию, как и на выходе пер вого элемента И 80 матрицы 79 дешифратора 2.

Сигнал с выхода первого элемента И 58 поступает на входы первого 66, второго 67 и шестого 71 элементов ИЛИ матрицы 65 дешифратора 1. .

Сигнал на выходе второго элемента И 59 матрицы 57 .элементов И дешифратора 1 вырабатьшается по такому же условию, как и на выходе пятого элемента И 84 матрицы 79 дешифратора 2.

Сигнал с выхода второго элемента И 59 поступает на входы второго 67 и третьего 68 элементов ИЛИ матрицы 65 дешифратора 1.

Сигнал на выходе третьего элемента И 60 матрицы 57 дешифратора 1 вы- рабатьгоается по такому же условию, как и на выходе десятого элемента И 89 матрицы 79 дешифратора 2.

Сигнал с выхода третьего элемента И 60 поступает на входы второго 67 и пятого 70 элементов матрицы 65 дешифратора 1.

Сигнал на выходе четвертого элемента И 61 матрицы 57 дешифратора 1 вырабатывается по такому же условию.

как и на выходе семнадцатого элемента И 96 матрицы 79 дешифратора 2

Сигнал с выхода четвертого элемета И 61 поступает на входы второго 67 и шестого 71 элементов ИЛИ матрицы 65 дешифратора 1.

Сигнал на выходе пятого элемента И 62 матрицы 57 дешифратора 1 вырабатывается по такому же условию, как и на выходе восьмого элемента И 87 матрицы 79 дешифратора 2. .

Сигнал с выхода пятого элемента И 62 поступает на входы третьего 68 и четвертого 69 элементов ИЛИ матрицы 65 дешифратора 1.

Сигнал на выходе шестого элемента И 63 матрицы 57 дешифратора 1 вырабатывается по такому же условию, как и,на вь1коде шестого элемента И 85 матрицы 79 дешифратора 2,

Сигнал с выхода шестого элемента И 63 поступает на входы четвертого 69 и шестого 71 элементов ИЛИ матрицы 65 дешифратора 1.

Сигнал на выходе седьмого элемента И 64 матрицы 65 дешифратора 1 вырабатывается по такому же условию, как и на выходе одиннадцатого элемента И 90 матрицы 79 дешифратора 2.

Сигнал с выхода седьмого элемента И 64 поступает на вход шестого 71 элемента ИЛИ матрицы 65 дешифратора 1.

Матрица 65 элементов ИЛИ дешифратора 1 предназначен для обеспечения условий выработки сигналов записи на выходах 73-78 дешифратора 1.

Сигнал с выхода 73 дешифратора 1

производит модификацию счетчика 4, Сигнал на выходе 73 дешифратора 1 вырабатывается при условии появления сигнала на выходе первого 66 элемента ШШ матрицы 65 и при наличии разрешающего сигнала и цепи 121. Сигнал на выходе первого элемента ИЛИ 66 появится при условии наличия сигнала с выхода первого 58 элемента И матрицы 57.

t

Сигнал с выхода 74 дешифратора 1 производит запись данных с первой информационной шины 20 в блок 35 памяти устройства.

Сигнал на выходе 74 дешифратора 1 вырабатьшается при условии появления сигнала на выходе второго 67 элемента ШШ матрицы 65 и при наличии разрешающего сигнала в цепи 121..

0

5

0

5

Сигнал на выходе второго элемен- та ИЛИ 67 появится,при условии наличия сигнала с выхода первого 58 или второго 59, или третьего 60,или четвертого 61 элементов И матрицы 57.

Сигнал с выхода 75 дешифратора 1 производит запись данных с первой информационной шины 20 в блок 38 памяти. Кроме того, он задним своим фронтом производит прибавление единицы к содержимому реверсивного счетчика 44.

Сигнал на выходе 75 дешифратора 1 вырабатывается при условии появления сигнала на выходе третьего 68 элемента ШШ матрицы 65 и при наличии разрешающего сигнала в цепи 121.

Сигнал на выходе третьего элемента РШИ 68 появится при условии наличия сигнала с выхода второго 59 или пятого 62 элементов И матрицы 57.

Сигнал с выхода 76 дешифратора 1 производит запись данных с первой информационной шины 20 в буферную память 36 устройства.

Сигнал на выходе 76 дешифратора 1 вырабатывается при условии появления сигнала на выходе четвертого 69 элемента ИЛИ матрицы 65 и при наличии разрешающего сигнала в цепи 121.

Сигнал на выходе четвертого элемента 1-ШИ 69 появится при условии наличия сигнала с выхода пятого 62 или шестого 63 элементов И матрицы 37.

Сигнал с выхода 77 дешифратора 1 производит вычитание единицы из содержимого реверсивного счетчика 44 устройства.

Сигнал на выходе 77 дешифратора 1 вьфабатьтается при условии появления сигнала на выходе пятого 70 элемента ИЛИ матрицы 65 и при наличии разрешающего сигнала в цепи 121.

Сигнал на выходе пятого элемента 5 ИЛИ 70 появится при условии наличия сигнала с выхода третьего 60 элемента И матрицы 57.

Работа первого и второго дешиф- , раторов в различных режимах работы устройства, описанных в тексте заявки, проиллюстрирована временными диаграммами (фиг.5-11). Каждое состояние работы устройства селектирует один из семнадцати элементов И ма- 5 трицы 79 дешифратора 2. Сигналы с выходов элементов И матрицы 79 через элементы ИЛИ матрицы 98 . формируют управляющие сигналы на выходах 110-120.

0

5

0

0

10

20

25

, 1513460

Каходое состояние работы устройста, npi котором необходимо произвети запись, селектирует один ия cet-oi лементов И матри1.ы 57, дешифратора 1, игналы с выходов элементов И мат- ицы 57 через элементы ИЛИ матрицы 5 и элементы И 72 формируют сиг иалы записи на выходах 73-78.

Каждому режиму работы устройства редшествует исходное состояние. В {СХОДНОМ состоянии, когда нет обра ения к устройству (52 0) и нет / казания о сбросе (49 0), незавиимо от состояния остальных сигиа.лов рабатывает второй элемент, И 81 де- ;ифратора 2 и сигнал с его выхода оступает через элементы ИЛИ 99, ИЛИ 101 и ИЛИ 107 на выходы 110, 112 и 115 дешифратора 2. В дешифраторе 1 и один из элементов И матрицы 57 е срабатывает и сигналы на выходах деширатора 1 отсутствуют. В исходном состоянии устройство будет находиться до тех пор, пока не по-., явится обращение к нему от ЭВМ (52 1) или не появится сигнал (49 1) сброса (момент Т1 на фиг.5-11),

Временная диаграмма работы первого и второго дешифраторов в режиме Сброс устройства представлена на фиг.5.

о При поступлении сигнала на вход 49 первого и второго дешифраторов (момент Т1) в депшфраторе 2 включается первый элемент И 80 и выключается второй элемент И 81. Сигнал с выхода первого элемента И 80 через десятый элемент ИЖ 108 поступает на выход 119 дешифратора 2. Выключение второго элемента И 81 приводит к снятию |сигналов на выходах 110э112и 118. рнятие сигнала с выхода 110 выводит реверсивный счетчик 44 из режима параллельной записи. Снятие сигнала с быхода 112 закрывает магистраль- :ный приемник 5 и в первой информационной шине 20 устанавливается код нуля (отсутствие каких-либо данных). Снятие сигнала с выхода 118 переведет счетчик 4 из режима параллельной записи в счетный. Сигнал с выхода 119 установит реверсивный счетчик 44 в «улевое состояние.

В дешифраторе 1 при поступлении сигнала на вход 49 включается, первьш :элемент И 58 и приход следующего (после появления сигнала на входе 49) импульса по цепи 121 разрешения

г

вы н вы п чи ю и

35 с . о

55 м

30

40

50

0

5

460

32

выдачи вызовет появление импульсов на выходах 73, 74 и 78, Сигналом с выхода 74 будет записан код нуля с первой информационной шины 20 в блок 37 памяти по нулевому адресу со счетчика 4 о Сигналом с выхода 78 произойдет запись нулевого значения с выхода реверсивного счетчика 44 в блок 45 памяти по тому же адресу. Задний фронт сигнала с выхода 73 переведет счетчик 4 в первое состояние.Следующий импульс на цепи 121 разрешения вьщачи вызовет запись нулей в блоки 37 и 45 памяти по второму адресу и так до тех пор, пока блоки 37 и 45 памяти не обнулятся nor всем адресам, после чего сигналом переполнения со счетчика 4 снимется сигнал на входе 49 дешифраторов и устройство перейдет в исходное состояние (момент Т2).

Работа первого и второго дешифраторов при обращении ЭВМ к устройству с операциями ввода/вывода проиллюстрирована .временными диаграммами (фиг.6-11).

операция обращения ЭВМ к устройству состоит из цикла начальной выборки, цикла, вьшолнения операции и цикла завершения операции.

Цикл начальной выборки любого ре- жима работы устройства (кроме режима Сброс) начинается в момент времени Т1, через 100-150 не после установки в системной магистрали адре- 35 са очереди обращения, ЭВМ устанавливает сигнгш в линию синхронизации, который поступает на вход (52 1) дешифраторов, К этому моменту дешифратор 7 адреса определяет обращение к устройству по первому (53 1, 54 0) адресу очереди (операции постановки в очередь и извлечения из очереди) или по второму .(53 0, 54 1). адресу очереди (операции чтения длины очереди или разрушения очереди). В момент Т1 включается третий элемент И 82 девмфратора 2 и активизирует сигналы на выходах 110 и 112 дешифратора 2, Снятие сигнала с выхода 118 дешифратора 2 (второй элемент И 81 вьпшючен)-зафиксирует в счетчике 4 код адреса очереди . обращения до конца текущей операции.

Через некоторый промежуток вре- 55 мени после установки сигнала на входе 52 дешифраторов (момент Т2) ЭВМ снимает код адреса с системной магистрали и начинает операцию ввода

0

40

50

3315

(50 1, 51 0) или вывода (50 , 51 1). К этому моменту дешифратор 43 анализирует признак пустой очереди и сигнал с его выхода через ре- гистр 41 поступает (если очередь пуста) на вход 55 дешифраторов. В этом состоянии в дешифраторе 2 включается только четвертый элемент И 83 (постановка в очередь) или девятый элемент И 88 (извлечение из очереди), или четырнадцатьш элемент И 93 (чтение длины), или шестнадцатый элемент И 95 (разрушение очереди) и сигнал с одного из выходов этих элементов активизирует сигнал на выходе 112. Снятие сигнала с выхода 110 (третий элемент И 82 выключен) прекращает запись в первой, второй, третий и четвертый регистры, реверсивный счет чик и подготавливает счетчик 3 устройства к счету.

Задний фронт первого (после установки сигнала на входе 50 или 51) импульса на цепи 121 переведет счет- .чик 1 из нулевого состояния в первое и на входах 47 и 48 дешифраторов установится код , 48 ( (момент ТЗ). До мемента ТЗ в дешифраторе 1 не включается ни один элемент И матрицы 57 и дешифратор 1 импульсов записи не вырабатывает.

С момента ТЗ начинается цикл выполнения операции, который для каждого режима протекает по разному. Завершается цикл выполнения операции обязательной вьщачей в ЭВМ сигнала ответа с выхода 111 дешифратора 2, ЭВМ, получив сигнал с выхода 111 дешифратора 2, завершает операцию ввода или вывода, сняв сигнал с четвертого (50 0) или пятого (51 0) входов дешифраторов. Б этом случае устройство переходит в состояние, предшествующее моменту времени Т2, т.е. включается третий элемент И 82 дешифратора 2, появляются сигналы на выходах 110, 112, обнуляется счетчик 3 (47 0, 48 0) и снимается сигнал ответа с выхода 111. ЭВМ в ответ на снятие сигнала с выхода 111 завершает текущую операцию и снимает сигнал синхронизации с входов 52 дешифраторов. Устройство переходит в исходное состояние. Во время цикла завершения работы дешифратор 1 никаких импульсов записи не вьфабатьша ет, Т|,е, в нем не включается ни один из элементов И матрихдр 57.

034

Далее будет описываться только цикл вьшолнения операции, так как циклы начальной выборки и заверше- ния одинаковы для всех режимов ра- боты устройства.

Для постановки элемента очереди в необходимую очередь ЭВМ адресуется к этой очереди по ее первому ад0

s

0

5

0

0

5

5

ресу. с операцией записи, устанавливая на системной магистрали код номера элемента очереди.

Временная диаграмма работы первого и второго дешифраторов в режиме постановки элемента очереди в пустую очередь представлена на фиг.6, На фиг.6-11 знаком обозначен произвольный,не имеющий значения уровень сигнала.

В цикле начальной выборки режима постановки элемента в пустзто очередь в- третьем регистре зафикс1фовался единичный сигнал с выхода дешифратора 43 как признак пустой очереди, а в регистре 39 - код номера устанавливаемого в очередь элемента (например, десять). В реверсивном счетчике 44 записан код нуля (очередь бьша пуста) с выхода блока 45 памяти. В момент ТЗ, когда счетчик 3 перейдёт из нулевого (47 0, 48 0) соетояния в первое (47 1, 48 0), при наличии признака пустой очереди (55 1) в дешифраторе 2 включается пятый элемент И 84, сигнал

5 с выхода которого поступает (как и в цикле начальной выборки) на выход 112 дешифратора 2 и последний комбинацию выходных сигнало не меняет. В дешифраторе 1 в этом случае срабатывает второй элемент И 59 и сигнал с его выхода появится на выходах второго 67 к третьего 68 элементов ИЛИ матрицы 65. Второй (после момента Т2) импульс в цепи 121 разрешит выдачу сигналов записи на выходах 74 и 75 дешифратора 1. Импульс с выхода 74 дешифратора 1 запишет в блок 38 памяти код числа десять (первого элемента очереди)

0 с первой информационной шины 20.

Сигнал с выхода 75 запишет код числа десять в блок 37 памяти, как код последнего элемента очереди. Задний фронт сигнала с выхода 75 прибавит единицу к содержимому реверсивного счетчика. Задний фронт второго импульса переведет счетчик 3 из первого состояния во второе (момент Т4).

3515

В этом состоянии (47 0 , 48 1) в дешифраторе 2 включится шестой элемент И 85 и активным станет сигнал на выходе 114 дешифратора 2. В этом случае во второй информационной шине 34 установится код числа десять из регистра 39. В дешифраторе 1 в этом состоянии включается, шестой элемент И бЗ, и сигнал с его выхода появится на выходах четвёртого 69 и шестого 71 элементов ИЖ. Третий импульс в цепи 121 разрешения выдачи вызовет появление сигналов на выходах 72 и 78 дешифратора 1. Импульс с выхода 72 зацишет ноль с первой информационной шины 20 в буфер1гую память 36 по.адресу десять. Сигнал с выхода 78 дешифратора 1 запишет код единицы с выхода реверсивного счетчика 44 в блбк 45 памяти. Задний фронт третьего импульса переведет счетчик 3 из второго состояния в третье (момент Т5). Начинается цикл завершения операции,

В третьем состоянии (47 1, 48 1) включается седьмой элемент И 86 второго дешифратора и сигнал с его вькода через второй элемент ИЛИ 100 (выход 111) закроет элемент И 9 устройства и импульсы перестанут поступать в цепь 121 разрешения выдачи. того, сигнал с выхода 111 сообщит ЭВМ о завершении операции постановки элемента с номером десять в адресуемую очередь. ЭВМ, получив I сигнал с выхода. 111 дешифратора 2, : снимет сигнал вывода (48 0). Де- I шифратор 2 снимет сигнал с выхода 1 I(момент Т6), ЭВМ снимает сигнал I синхронизации (52 ). Устройство I переходит в исходное состояние (мо- :кент Т7).

Для постановки следующего элемента в,эту же очередь ЭВМ, как и в предыдущем случае, адресуется к этой очереди с операцией вывода (записи) , установив на системной магист- рали код второго элемента очереди (например,, ста).

Временная диаграмма работы первого и второго дешифраторов в режим постановки элементов в непустую очередь представлена на фиг.7,

В цикле начальной выборки регист 39 зафиксировал код числа сто как номер устанавливаемого элемента очереди, регистр 40 - код числа десять как номер первого элемента очереди.

5

60

36

регистр 41 - признак непустой очереди (55 0) , регистр 42 - код числа десять, как номер последнего элемента очереди.

После завершения цикла начальной выборки (момент ТЗ) при единичном состоянии счетчик-а 3 (47 1, 48 0) и при отсутствии признака пустой очереди (55 0) в дешифраторе 2 включится восьмой элемент И 87 и ак- тивизирз ет сигнал на выходах 112 и 116, Сигнал с выхода 116 открывает регистр 42 и по втррой информационной шине 34 распространится код числа десять. В дешифраторе 1 в этом состоянии включится элемен- И 62 и подготовит выдачу сигналов записи на выходах 75 и 76. Второй (после момента Т2) импульс с цепи 121 разрешения вьщачи инициирует выдачу импульсов записи на выходах 75 и 76 дешифратора 1. Сигнал с выхода 75 дешифратора 1 ггроизведет запись кода числа сто с первой информационной шины 20 в блок 37 памяти и своим задним фронтом прибавит единицу е содержимому реверсивного счетчика 44, Сигнал с выхода 76 дешифратора 1 запишет код числа сто в буферную память 36 по адресу десять. Задний фронт второго импульса переведет счетчик 3 во второе состояние (момент Т4).

В этом состоянии (47 0, 45 1) в дешифраторе 2 включится шестой элемент И 85 и активным станет сигнал на выходе 114 дешифратора 2, В этом случае во второй информационной шине 34 становится код числа сто из регистра 39, В дешифраторе 1 в этом состоянии включается шестой элемент И 63,и сигнал с его выхода появится на выходах четвертого 69 и шестого 71 элементов УШИ,- Третий импульс в цепи 121 разрешения вадачи вызовет появление сигналов на выходах 76 и 78 дешифратора 1, Импульс с выхода 76 запишет ноль с первой информационной шины 2,в буферную память 36 по ад- ресу сто. Сигнал с выхода 78 первого дешифратора запишет код двойки с выхода реверсивного счетчика 44 в блок 45 памяти.

Задний фронт третьего импульса переведет счетчик 3 из второго состо-, 55 яния в третье (момент ТЗ). Начинается цикл завершения операции,

В третьем состоянии (47 1, 48 1) включается седьмой элемент И 86

0

5

0

45

50

37.15

дешифратора 2 и сигнал с его выхода через второй элемент ИЛИ 100 (выход 111) закроет первый элемент И устройства и импульсы перестанут поступать в цепь 121 разрешения выдачи. Кроме того, сигнал с выхода 111 сообщит ЭВМ о завершении операции постановки элемент с номером сто в адресуемую очередь. ЭВМ, получив сигнал с выхода 111 дешифратора 2 снимет сигнал вывода (51 0f). Дешифратор 2 снимет сигнал с выхода 111 (момент Т6). ЭВМ снимает сигнал синхрониза ции (52 0). Устройство переходит в исходное состояние (момент Т7).

Для извлечения элемента из очереди ЭВМ адресуется к нужной очереди по первому ее адресу с операцией ввода (чтения). Устройство вьщает в ЭВМ номер первого элемента очереди Если очередь пустая, устройство выдает в ЭВМ нулевой код.

Временная диаграмма работы первого и второго дешифраторов в режи-i мё извлечения элемента из непустой очереди представлена на фиг.8.

В цикле начальной выборки при поступлении сигнала ввода на вход 50 дешифраторов (момент Т2) сработает девятый элемент И 88 матрицы I 79 и активизирует сигнал, как и в предыдущих случаях, только на выходе 112 дешифратора 2.

После завершения цикла начальной выборки (момент ТЗ) при единичном состоянии первого счетчика (47 1, 48 i) и при отсутствии признака пустой очереди (55 0) в дешифраторе 2 включится десятый элемент И 89 и активизирует сигналы на вькодах 113, 115 и 117 дешифратора 2. Сигналами с выходов 115 и 113 открываются регистр 40 и магистральный передатчик 6. Код номера первого элемента очереди поступает в системную магистраль. Сигнал с выхода 117 открывает буферную память 36 и код номера, следующего за первым элемента поступает в первую информационную ши-ну 20..

В дешифраторе 1 в этом состоянии включится третий элемент И 60 и второй (после момента Т5) импульс в це пи 121 разрешит выдачу сигналов записи с выходов 74 и 77 дешифратора Сигнал с выхода 74 запишет в блок - 37 памяти код номера следующего элемента очереди или код нуля, если вы3460

38

5

дается последний элемент очереди. Сигнал с выхода 77 уменьшит на единицу содержимое реверсивного счетчика 44. Задний фронт второго импульса (момент Т4) переведет счетчик 3 из первого состояния во второе (47 52, 48 1), при котором в дешифраторе 2 включится одиннадцатый элемент И 90, который активизирует комбинацию выходных сигналов такую же, как и элемент И 89 в предыдущем состоянии устройства (47 1, 48 0).

В дешифраторе 1 в этом состоянии включится седьмой элемент И 64 и тре- тий импульс на цепи 121 разрешит вьщачу импульса записи на выходе 64 дешифратора 1, которьй запишет скорректированный код длины очереди в блок 45 памяти.

Задний фронт третьего импульса (момент Т5) переведет счетчик 3 в третье состояние (47 1, 48 t), при котором в дешифраторе 2 включится двенадцатьш элемент И 91 и к уже имеющимся сигналам на выходе дешифратора 2 добавится сигнал на выходе 111, который сообщит ЭВМ о завершении операции, т.е. о том, что номер первого элемента очереди установлен на системной магистрали, после чего ЭВМ завершает операцию чтения (момент Т6, Т7).

Временная диаграмма работы дешиф- 5 ратора 2 в режиме извлечения элемента из пустой очереди, т.е. когда 1 ЭВМ пытается прочесть номер элемен- та очереди, а адресуемая очередь пу0

5

0

стая, представлена на фиг.9,

В цикле начальной выборки, когда произошло обращение- к устройству (52 1) с операцией чтения (50 1, 51 0) по первому адресу очереди (53 1, 54 ч 0) и дешифратор 43 устойства определил признак пустой очереди, на вход 55.дешифраторов будет подан высокий уровень (55 1) с выхода регистра 41. После завершения цикла начальной выборки (момент

ТЗ) при единичном состоянии счетчика 3 (47 1, 48 ) в дешифраторе 2 включится тринадцатый элемент И 92 и сигнал с его выхода через второй 100, четвертый 102 и шестой 104 элемент ИЛИ поступит на выходы 111,

113 и 115. Сигнал с выхода 115 вы- даст код нуля (с регистра 40 через открытьй сигналом 113 магистральный

передатчик 6) в системную магистраль, а сигнал с выхода 111 дешифратора 2 сообщит ЭВМ о завершении оператщи, ЭВМ обычным образом завер- операцию .(моменты Т4, Т5) ,

Дешифратор 1 в режиме чтения пустой очереди не работает.

В режиме чтения длины адресуемой очереди ЭВМ обращается к устройству (52 1) с операцией чтения (50 1, 51 0) по второму адресу очереди (53 0, 54 1) .

Временная диаграмма работы дешифратора 2 .(дешифратор 1 в этом режиме не работает) представлена на фиг.10.

После завершения цикла начапьнрй 1выборки (момент ТЗ) в дешифраторе 2 включается пятнадцатый элемент И 94 и сигнал с его выхода через второй 100, четвертьй 102 и одиннадцатый 109 элементы ИЛИ поступит на выходы

1

113 и 120 дешифратора 2. Сигнал

с выхода 120 разрешит вьщачу кода длины адресуемой очереди из реверсивного счетчика 44 через передатчик 46 во вторую информационную шину устройства 34. Сигнал с выхода 113 разрешит выдачу кода длины адресуемой очереди из второй информационной шины 34 устройства через (открытьй магистральный передатчик 6 в системную магистраль. Сигнал с выхода 111 дешифратора 2 сообщит ЭВМ о завершении.операции. ЭВМ пбсле получения сигнала с выхода 111 дешифратора 2 завершает операцию (моменты Т4, Т55,.

Для разрушения какой-либо очереди ЭВМ адресуется к этой очереди (52 1) по второму ее адресу (53 0, 54 1) с операдаей записи (50 0, 51 -1).

Временная диаграмма работы первого и второго дешифраторов в режиме разрушения очереди представлена на фиг.11.

В этом режиме после завершения цикла начальной выборки (момент ТЗ) при первом состоянии первого счетчика (47 1, 48 0) в дешифраторе 2 включается семнадцатьШ элемент И 96 и сигнал с его вйхода через десятый элемент ИЛИ 108 поступает на выход 119 дешифратора 2 и устанавливает в нулевое состояние реверсивный счетчик 44.

В депшфраторе 1 в этом состоянии включается четвертый элемент И 61 и

второй (после момента Т2) импульс в цепи 121 разрешит выдачу импульсов записи на выходы 74 и 78. При этом сигналом с выхода 74 деш1фратора 1

в блок 37 памяти запишется код нуля (с первой информационной шины 20), а в.блок 45 памяти запишется код нуля с выхода реверсивного счетчика

, -44. Задний фронт второго импульса переведет счетчик 3 во второе состояние (47 2, 48 1), при котором в дешифраторе 2 включится восем- надцатьй элемент И 97 и сигнал с

, его выхода, через второй элемент

ИЛИ 100 поступит на выход 111 дешифратора 2 и сообщит ЭВМ о завершении операции (момент Т4). ЭВМ после получения сигнала с выхода 111 деп шифратора 2 завершает операцию (моменты Т5 и Тб).

Формула изобретения

j . Устройство для управления обменом информацией, содержащее буферную память, два дешифратора, два счетчика, реверсивный счетчик, причем первый и второй выходы первого счетчика соединены с первым и вторым информационными входами первого и второго дешифраторов, первые выходы которых соединены соответственно с разрешающим входом и входом записи буферной памяти, вторые выходы первого и вто5 рого дешифраторов соединены соответственно с входом уменьшения счета и с установочным входом реверсивного счетчика, отличающееся тем, что, с целью повьш1ения быстро 0 действия и сокращения аппаратурных затрат, в устройство введены четыре регистра, три блока пакйдти, третий дешифратор, передатчик, дешифратор адреса, магистральный передатчик,

45 магистральньй приемник, триггер, генератор импульсов, два элемента И, причем группа информационных выходов магистрального передатчика и группа информационных входов магистрального

50 приемника образуют группу входов-вы-, ходов устройства для подключения к адресной и информационной магистрали ЭВМ, установочньй вход второго счетчика соединен с первым входом

55 neipBoro элемента И и является входом . устройства для подгслючения к установочной шине магистрали ЭВМ, третий, четвертьй и пятый информационные входы первого дешифратора соединены со0

ответственно с третьим, четвертым и пятым информационными входами второго дешифратора и являются входами устройства для подключения соответственно к шине синхронизации, шине ввода, шине вывода магистрали ЭВМ, третий выход второго дешифрато соединен с первым входом второго элмента И и является выходом устройства для подключения к шине ответа магистрали ЭВМ, при этом синхровыхо