1 Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных машинах и устройствах цифровой обработки сигналов для перемножения матриц.

Цель изобретения - упрощение контроля работоспособности устройства.

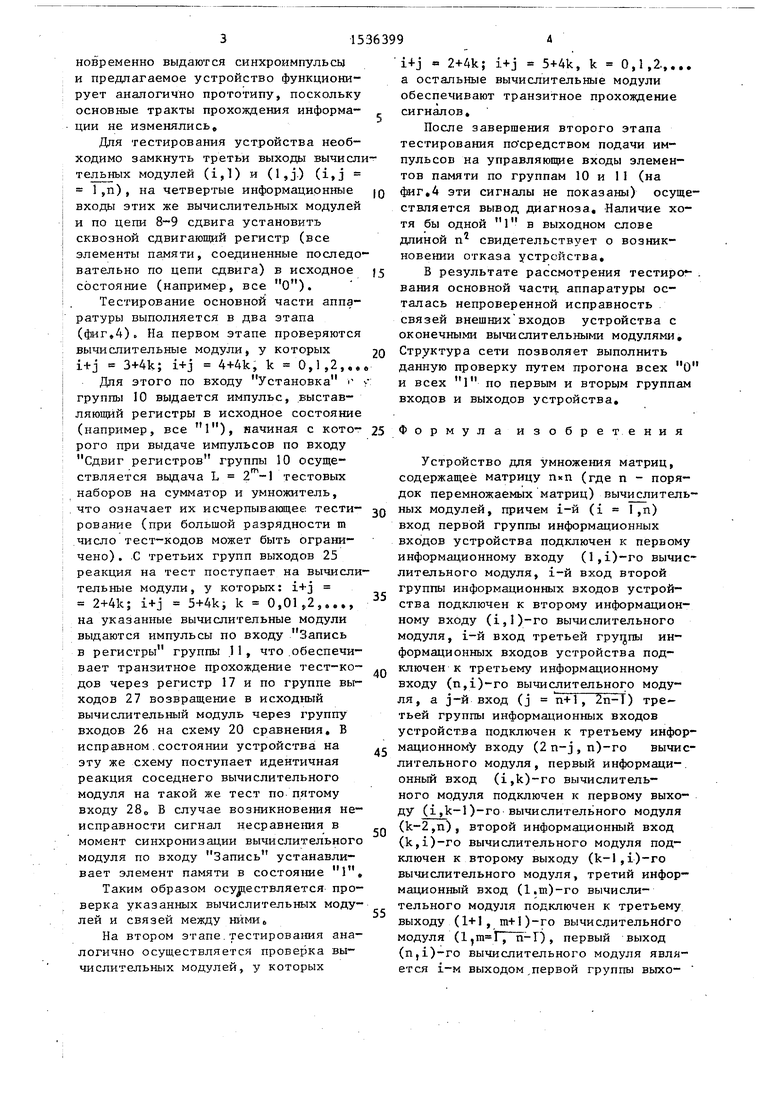

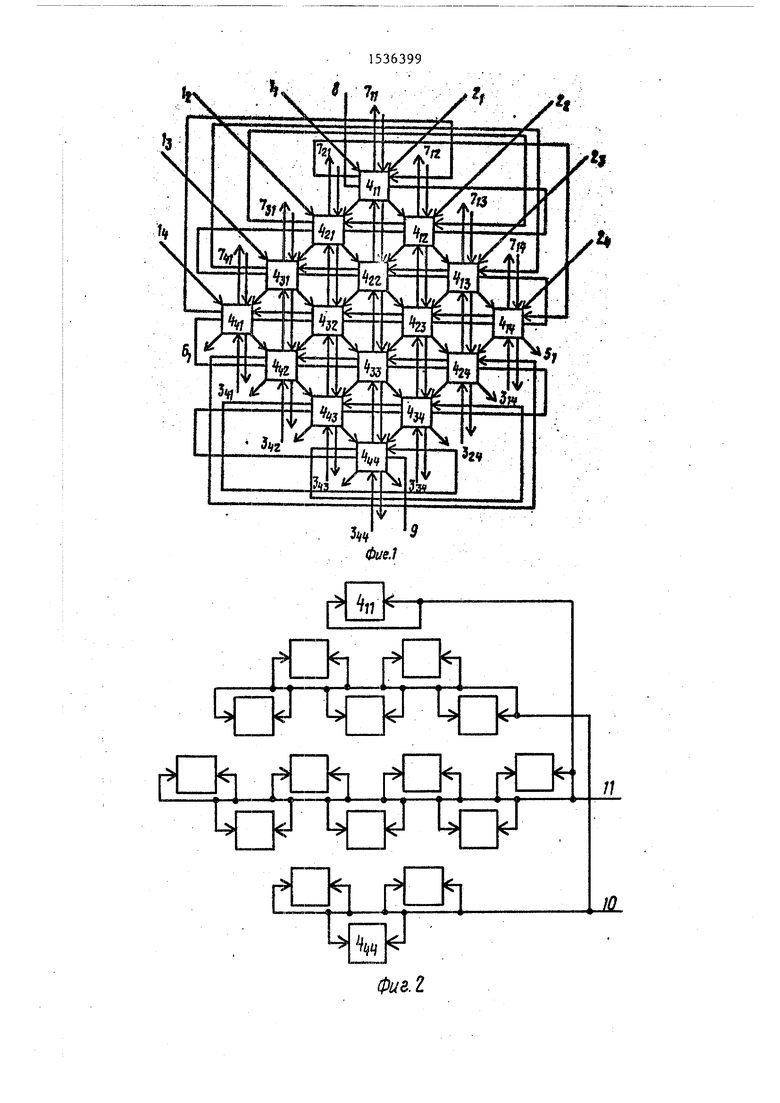

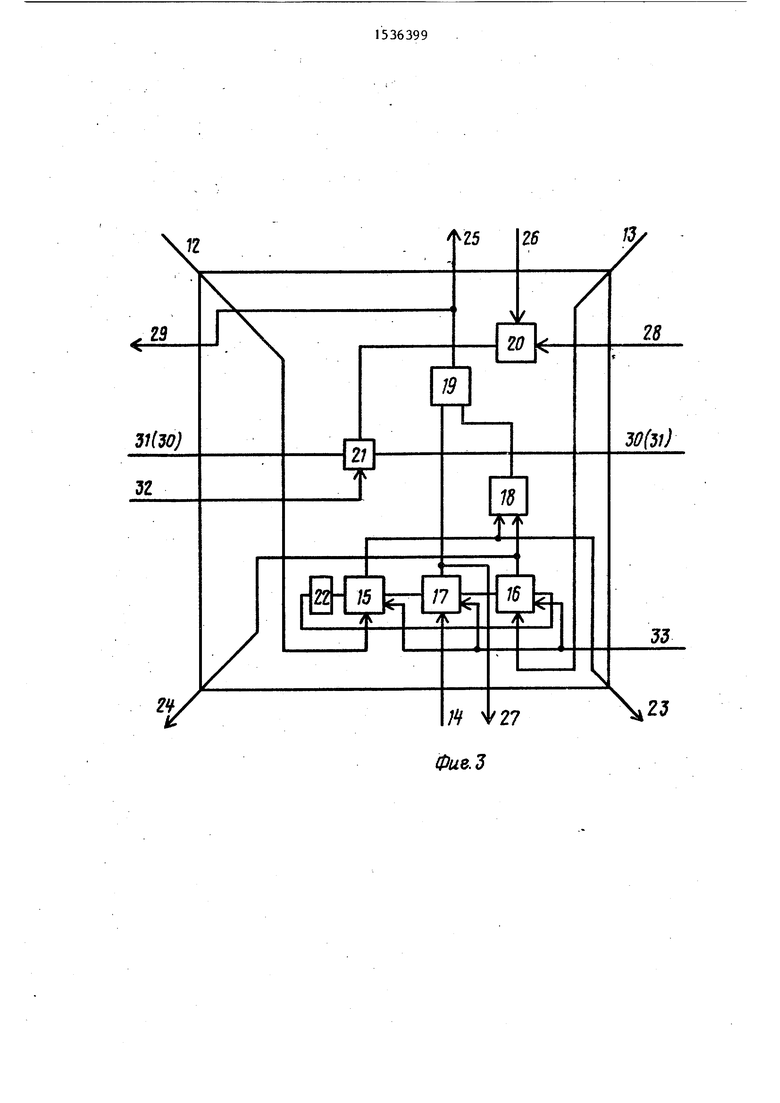

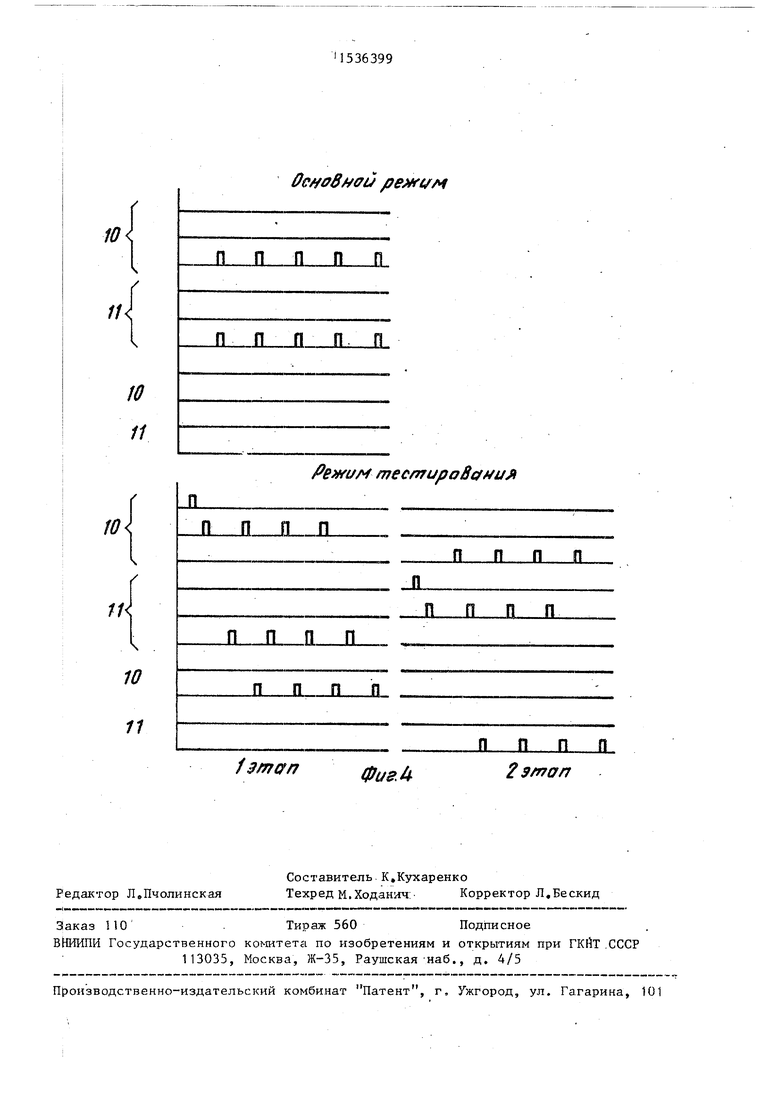

На фиг.1 представлена схема устройства для умножения матриц порядка 4; на фиг.2 - схема соединений для обеспечения синхронизации; на фиг.З - схема вычислительного модуля; на фиг.4 - временные диаграммы работы устройства.

Устройство содержит первую 1{ (1 1,4), вторую 2. и третью 3j (j 1,7) информационных входов, вычислительные модули 4 (k 1,4), первую 5.J , вторую 6- и третью 7 группы выходов, информационные вход 8 и

выход 9 устройства (образующие цепь . сдвига), первую 10 и вторую 11 группы управляющих входов.

Каждый вычислительный модуль содержит первый 12, второй 13 и третий 14 информационные входы, первый 15, второй 16 и третий 17 регистры, умножитель 18, сумматор 19, схему 24 сравнения, элемент 21 памяти, сумматор 22 по модулю два, первый 23, второй 24 и третий 25 выходы, четвертые информационный вход 26 и выход 27, пятые информационный вход 28 и выход 29, вход 30 и выход 31 элемента памяти, вторую 32 и первую 33 группы управ- ляющих входов.

В устройстве предусмотрено два режима функционирования: основной и тестирования,

В основном режиме на управляющие входы 10 и 11,Запись в регистры одел

со о

со со

Ј

новременно выдаются синхроимпульсы и предлагаемое устройство функционирует аналогично прототипу, поскольку основные тракты прохождения информации не изменялись.

Для тестирования устройства необходимо замкнуть третьи выходы вычисли тельных модулей (1,1) и (l,j) (i,j 1,n) , на четвертые информационные входы этих же вычислительных модулей и по цепи 8-9 сдвига установить сквозной сдвигающий регистр (все элементы памяти, соединенные последовательно по цепи сдвига) в исходное состояние (например, все О).

Тестирование основной части аппаратуры выполняется в два этапа (). На первом этапе проверяются вычислительные модули, у которых i-tj 3+4k; i+j 4+4k, k 0,1,2,,.

Для этого по входу Установка группы 10 выдается импульс, выставляющий регистры в исходное состояние (например, все 1), начиная с которого при выдаче импульсов по входу Сдвиг регистров группы 10 осуществляется выдача L 2т-1 тестовых наборов на сумматор и умножитель, что означает их исчерпывающее тестирование (при большой разрядности m число тест-кодов может быть ограничено). С третьих групп выходов 25 реакция на тест поступает на вычислительные модули, у которых: i+j 2+4k; i+j 5+4k; k 0,01,2,..., на указанные вычислительные модули выдаются импульсы по входу Запись в регистры группы 11, что обеспечивает транзитное прохождение тест-кодов через регистр 17 и по группе выходов 27 возвращение в исходный вычислительный модуль через группу входов 26 на схему 20 сравнения. В исправном состоянии устройства на эту же схему поступает идентичная реакция соседнего вычислительного модуля на такой же тест по пятому входу 28в В случае возникновения неисправности сигнал несравнения в момент синхронизации вычислительного модуля по входу Запись устанавливает элемент памяти в состояние 1.

Таким образом осуществляется проверка указанных вычислительных модулей и связей между нимий

На втором этапе тестирования аналогично осуществляется проверка вычислительных модулей, у которых

5

i+j « 2+4k; i+j - 5+4k, k 0,1,2.,... а остальные вычислительные модули обеспечивают транзитное прохождение сигналов.

После завершения второго этапа тестирования посредством подачи импульсов на управляющие входы элементов памяти по группам 10 и 11 (на фиг.4 эти сигналы не показаны) осуществляется вывод диагноза. Наличие хотя бы одной 1 в выходном слове длиной пг свидетельствует о возникновении отказа устройства,

В результате рассмотрения тестиро - вания основной часта аппаратуры осталась непроверенной исправность связей внешних входов устройства с оконечными вычислительными модулями. Структура сети позволяет выполнить данную проверку путем прогона всех О и всех 1 по первым и вторым группам входов и выходов устройства.

25 Формула изобретения

0

5

0

5

0

5

Устройство для умножения матриц, содержащее матрицу пхп (где п - порядок перемножаемых матриц) вычислительных модулей, причем i-й (i 1,п) вход первой группы информационных входов устройства подключен к первому информационному входу (l,i)-ro вычислительного модуля, i-й вход второй группы информационных входов устройства подключен к второму информационному входу (i,l)-ro вычислительного модуля, i-й вход третьей группы информационных входов устройства подключен к третьему информационному входу (n,i)-ro вычислительного модуля, а j-й вход (j п+1, 2п-1) третьей группы информационных входов устройства подключен к третьему информационному входу (2 n-j , n)-ro вычислительного модуля, первый информационный вход (i,k)-ro вычислительного модуля подключен к первому выходу (i,k-l)-ro вычислительного модуля (k-2,n), второй информационный вход (k,i)-ro вычислительного модуля подключен к второму выходу (k-l,i)-ro вычислительного модуля, третий информационный вход (l.m)-ro вычислительного модуля подключен к третьему выходу (1+1, т+1)-го вычислительного модуля (L ,, п-Г), первый выход (n,i)-ro вычислительного модуля является i-м выходом первой группы выхо-

дов устройства, второй выход (i,n)-ro вычислительного модуля является i-м выходом второй группы выходов устройства, третий выход (i,l)-ro вычислительного модуля является (n-i+1)-м выходом третьей группы выходов устройства, а третий выход (1,1)-го вычислительного модуля является (п+1)-м выходом третьей группы выходов устройства, каждый вычислительный модуль содержит три регистра, умножитель и сумматор, причем первый, второй и третий информационные входы вычислительного модуля соединены со входами соответственно первого, второго и третьего регистров, выходы первого и второго регистров соединены

15 ()го вычислительного модуля,пятый выход которого соединен с пятым информационным входом (1,4)-го вычислительного модуля, пятый выход (п, п-1)-го вычислительного модуля

соответственно с первым и вторым вы« ходами вычислительного модуля и с соединен с пятым информационным вхо- вым и вторым входами умножителя, вы- дом (п,п)-го вычислительного модуля, ход которого соединен с первым вхо- ,пятый выход которого соединен с пятым дом сумматора,второй вход которого (информационным входом (п-1,п)-го вы- соединен с выходом третьего регистра, числительного модуля, пятые информа- а выход - с третьим выходом вычисли- 25 ционные входы (l,s)-ro и (г,п)-го вычислительных модулей соединены с

тельного модуля, управляющие входы всех регистров соединены с первой группой управляющих входов вычислительного модуля, отличающееся тем, что, с целью упрощения контроля работоспособности устройства, в каждый вычислительный модуль введены схема сравнения,.сумматор по модулю два и элемент памяти, принятыми выходами соответственно , (s,l)-ro и (п,г)-го-вычислительных модулей (s,,n; s,rЈ 4), пятый ин- 30 формационный вход (k,l)-ro вычислительного модуля соединен с пятым выходом (k-1, 1+1)-го вычислительного модуля, регистры каждого вычислительного модуля соединены последовательется второй группой управляющих входов вычислительного модуля, первая и вторая группы управляющих входов (p,q)-го вычислительного модуля (p+q-4t 3;4; t 0,,..,) подключена к первой группе управляющих входов устройства, первая и вторая группы управляющих входов (v,u)-ro вычислительного модуля (v+u-4L 2;5) подключены к второй группе управляющих входов устройства, пятый выход (4,1)-го вычислительного модуля соединен с пятым информационным входом

5 ()го вычислительного модуля,пятый выход которого соединен с пятым информационным входом (1,4)-го вычислительного модуля, пятый выход (п, п-1)-го вычислительного модуля

о соединен с пятым информационным вхо- дом (п,п)-го вычислительного модуля, ,пятый выход которого соединен с пятым (информационным входом (п-1,п)-го вы- числительного модуля, пятые информа- 5 ционные входы (l,s)-ro и (г,п)-го вычислительных модулей соединены с

нятыми выходами соответственно , (s,l)-ro и (п,г)-го-вычислительных модулей (s,,n; s,rЈ 4), пятый ин- формационный вход (k,l)-ro вычислительного модуля соединен с пятым выходом (k-1, 1+1)-го вычислительного модуля, регистры каждого вычислительного модуля соединены последователь

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выполнения быстрого преобразования Уолша на скользящем интервале | 1990 |

|

SU1789990A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU999046A1 |

| Устройство для вычисления рекуррентных соотношений | 1989 |

|

SU1683032A1 |

| Вычислительное устройство | 1986 |

|

SU1355974A1 |

| Устройство для треугольного разложения ленточных матриц | 1988 |

|

SU1587540A1 |

| Устройство для ортогонального преобразования цифровых сигналов по функциям Хаара | 1983 |

|

SU1116435A1 |

| Устройство для деления | 1988 |

|

SU1621034A1 |

| Устройство для умножения матриц | 1990 |

|

SU1793446A1 |

| Устройство для контроля умножения по модулю три | 1986 |

|

SU1361556A1 |

| Устройство для перемножения матриц | 1990 |

|

SU1734104A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных машинах и устройствах цифровой обработки сигналов для перемножения матриц. Цель изобретения - упрощение контроля работоспособности. Вычислительные модули соединены в матрицу таким образом, что обеспечиваются два режима работы - основной (перемножение матриц) и тестирования. Достоинством устройства являются низкие дополнительные аппаратурные затраты, высокая достоверность тестирования. 4 ил.

чем первый и второй входы схемы срав- ос но по цепи сдвига с сумматором по нения подключены соответственно к модулю два, образуя сдвиговый регистр-генератор последовательности псевдослучайных кодов, а элементы

памяти всех вычислительных модулей

четвертому и пятому информационным входам вычислительного модуля, четвертый выход вычислительного модуля соединен с выходом третьего регистра, 40 соединены последовательно в сквозной а пятый выход - с выходом сумматора, регистр сдвига, вход и выход которо- выход схемы сравнения соединен с го являются соответственно информаци- входом записи элемента памяти, труп- онными входом и выходом устройства, па управляющих входов которого являпамяти всех вычислительных модулей

соединены последовательно в сквозно регистр сдвига, вход и выход которо го являются соответственно информац онными входом и выходом устройства,

п

/ .

Фиг. 2

Фие.З

0с /08н0и режим

Режим тестирования

| Гун Суньюань | |||

| Систолические волновые и матричные процессоры для высокопроизводительных вычислений,- ТИИЭР, т | |||

| Термосно-паровая кухня | 1921 |

|

SU72A1 |

| Воеводин В.В.Математические модели и методы в параллельных процессах,- М.: Наука, 1986, с.221.рис.23.2 | |||

Авторы

Даты

1990-01-15—Публикация

1988-02-04—Подача