вычислительных блоков, каждый i-й вычислительный блок содержит сумматоры коэффициентов делимого и делителя, первый сумматор частного, регистры сумм делимого, делителя, част- него, регистры переносов делимого8 делителя, частного, сумматоры делимого, делителя, второй, третий и четвертый сумматоры частного, дешифраторы делимого, делителя, частного, узлы формирования делимого, делителя, частного, регистры промежуточных результатов делимого, делителя, коммутаторы первого коэффициента делимо1

Изобретение относится к вычислительной технике и может быть применено в специализированных вычислителях .

Целью изобретения является расши- рёние класса решаемых задач за счет возможности вычисления выражения Y; (A.Y,.,+ Bi)/(C,.Y,,, +D.) (i 1, i N; N - размерность массивов аргументов и результатов),

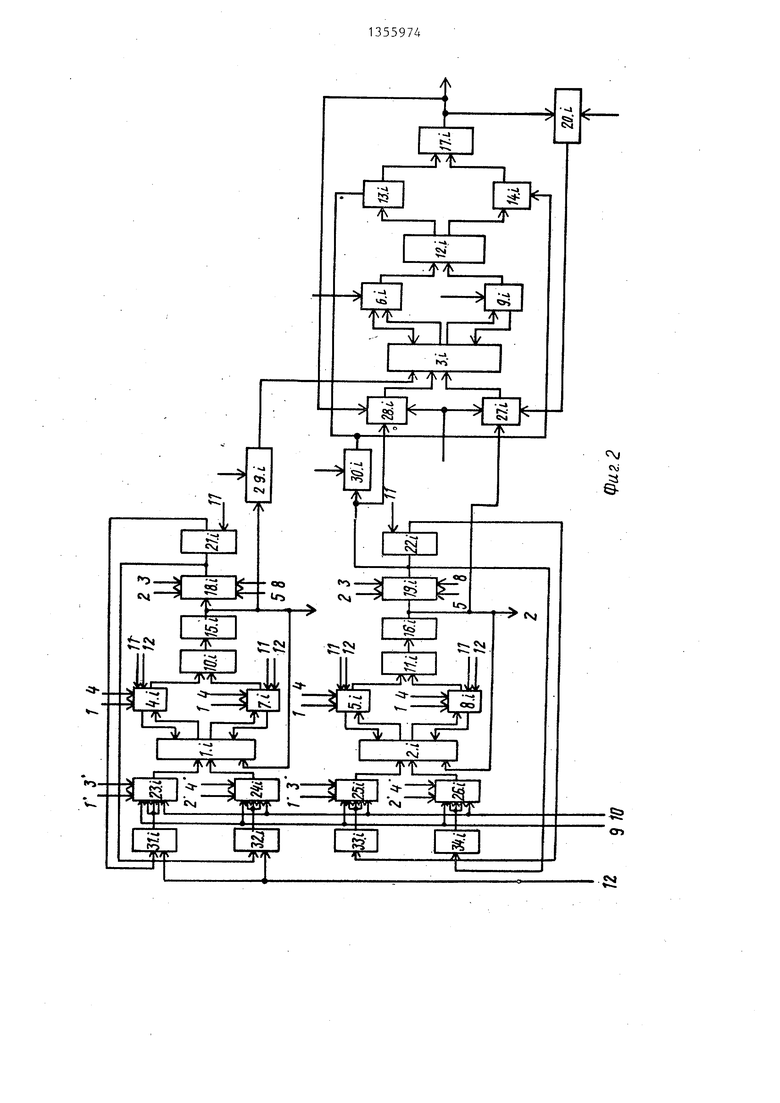

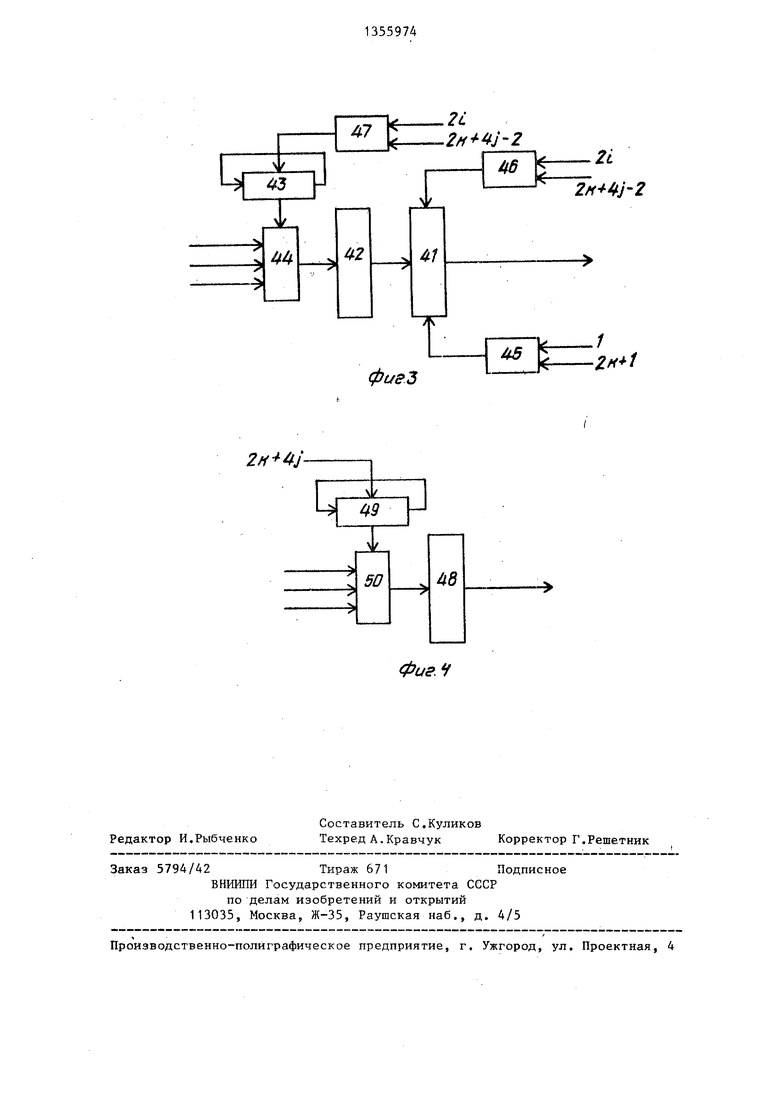

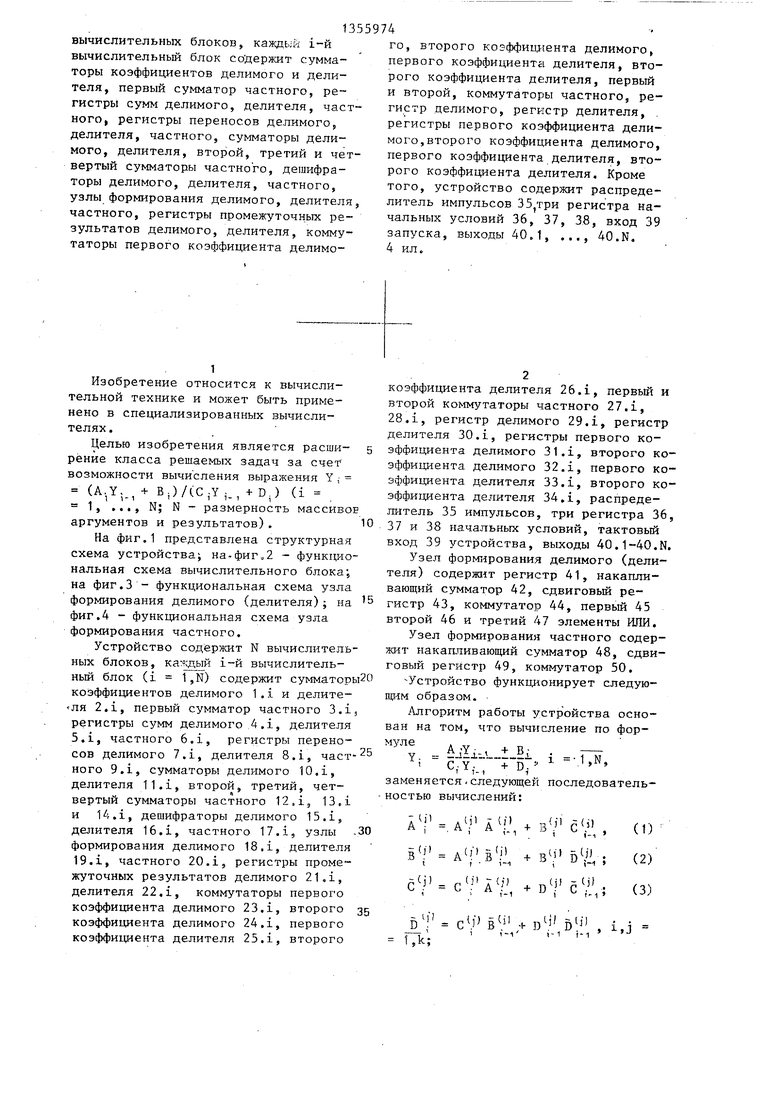

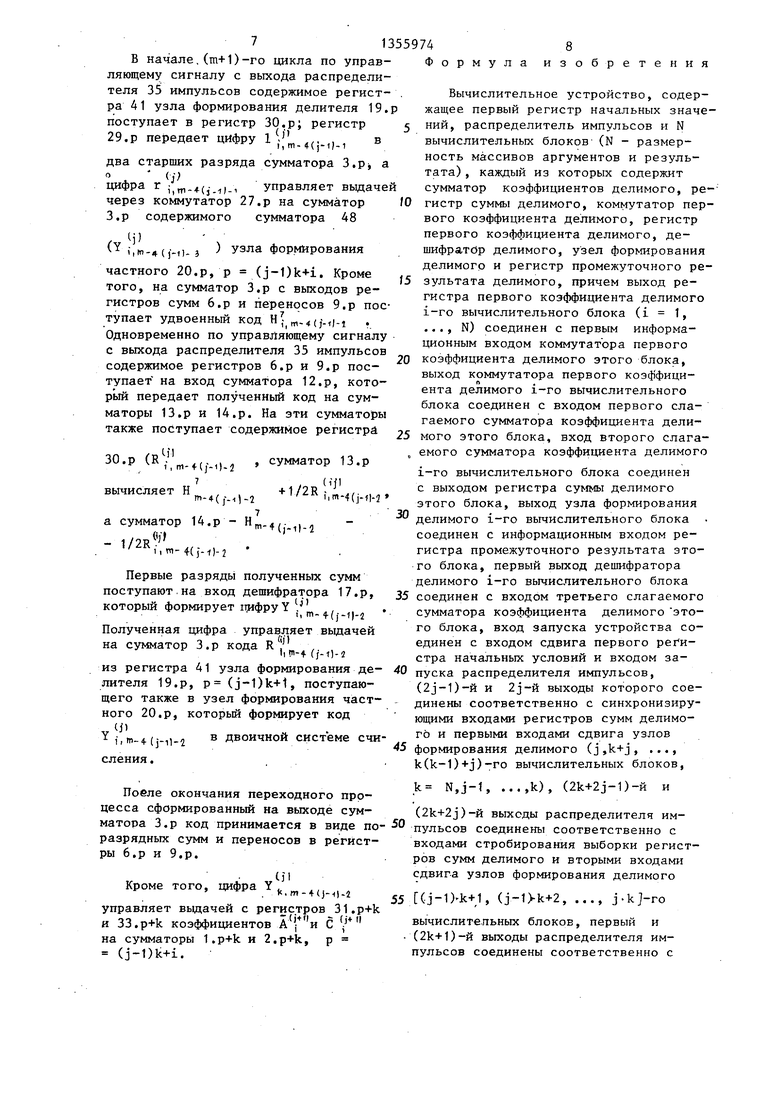

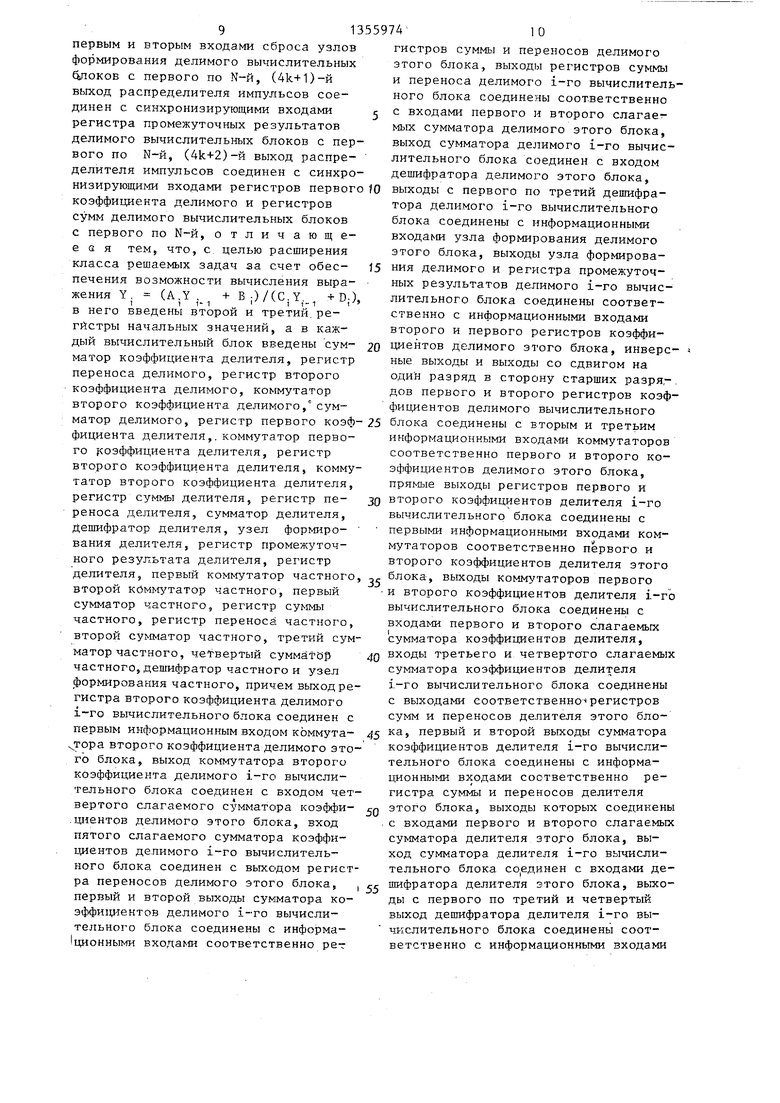

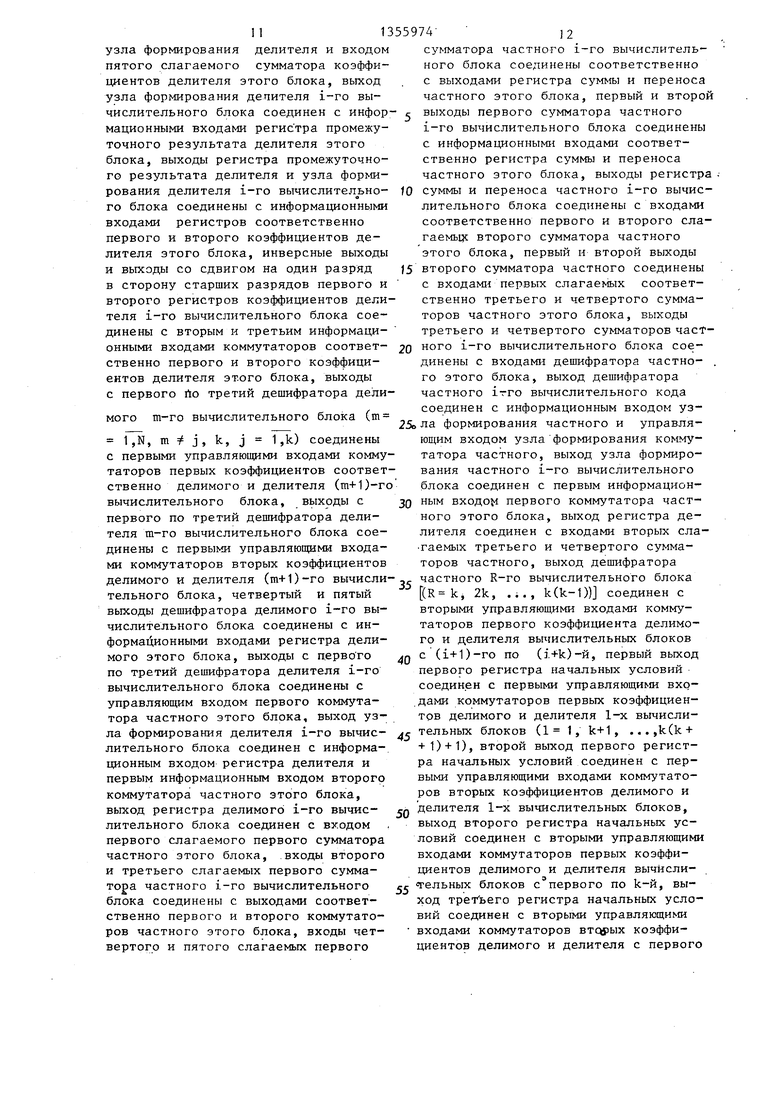

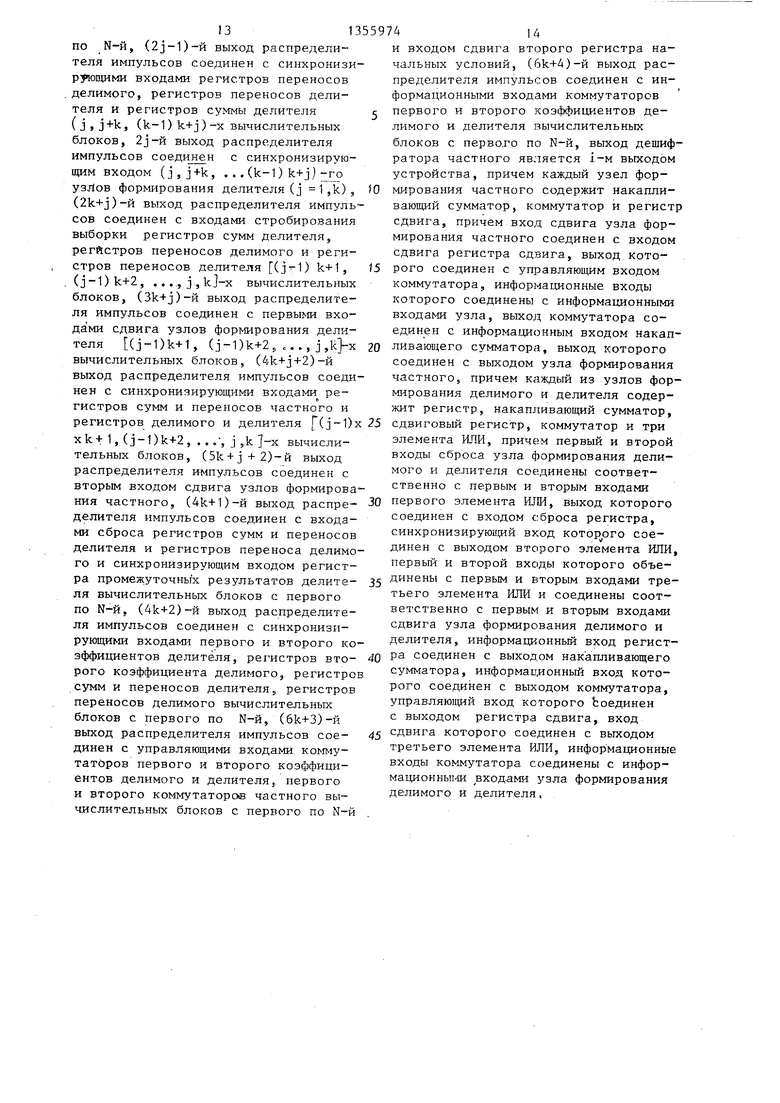

На фиг.1 представлена структурная схема устройства; на-фиг.2 - функциональная схема вычислительного блока; на фиг.3 - функциональная схема узла формирования делимого (делителя); на фиг.4 - функциональная схема узла формирования частного.

Устройство содержит N вычислительных блоков, ка.сдый i-й вычислительный блок (i 1,N) содержит сумматоры коэффициентов делимого 1.1 и делите- ля 2.1, первый сумматор частного 3.i регистры сумм делимого .4.1, делителя 5.1, частного 6.1, регистры перено

сов делимого 7.1, делителя 8.1, частного 9.1, сумматоры делимого 10.1, делителя 11.1, второй, третий, четвертый сумматоры частного 12.1, 13,1 и 14.1, дешифраторы делимого 15.1, делителя 16.1, частного 17.1, узлы формирования делимого 18,1, делителя 19.1, частного 20.1, регистры промежуточных результатов делимого 21,1, делителя 22,1, коммутаторы первого коэффициента делимого 23.1, второго коэффициента делимого 24.1, первого коэффициента делителя 25.1, второго

го, второго козффищ1ента делимого, первого коэффициенте делителя, второго коэффициента делителя, первый и второй, коммутаторы частного, регистр делимого, регистр делителя, . регистры первого коэффициента делимого, второго коэффициента делимого, первого коэффициента делителя, второго коэффициента делителя. Кроме того, устройство содержит распределитель импульсов 35,три регистра начальных условий 36, 37, 38, вход 39 запуска, выходы 40,1, ..., 40.N, 4 ил.

коэффициента делителя 26.1, первый и второй коммутаторы частного 27.1, 28,1, регистр делимого 29,1, регистр делителя 30.1, регистры первого коэффициента делимого 31.1, второго коэффициента делимого 32.1, первого коэффициента делителя 33.1, второго коэффициента делителя 34,1, распределитель 35 импульсов, три регистра 36, 37 и 38 начальных условий, тактовый вход 39 устройства, выходы 40.1-40,N.

Узел формирования делимого (делителя) содержит регистр 41, накапливающий сумматор 42, сдвиговый регистр 43, коммутатор 44, первый 45 второй 46 и третий 47 элементы ИЛИ,

Узел формирования частного содержит накапливающий сумматор 48, сдвиговый регистр 49, коммутатор 50.

Устройство функпдонирует следующим образом.

Алгоритм работы устройства основан на том, что вычисление по формуле д ,,.

Y - ..l-Ei 4 -.Г i - С,У,.., D, - bN,

заменяется.следующей последовательностью вычислений:

А . А +в с

л , , л J а ;. -hJi5 ,

в / A l B i+В D /, ;

г

- ;- Ь ; A .,+и i ;.i

,, i,j

i,k;

0; (4)

13

Выражения (1), (3), (2), (4) вычисляются соответственно по алгоритмам :

+ D

(1)

+

+ D

С) ;

HO Н Нз н: О, т 1,q, выражение (5) вычисляется по алгоритму:

г;, ,L - цифры

R fi i А i , вВ i , (. i (

m-x разрядов

. Е , . к Я

(j)

ft И) Y ьт 1,1

Y J соответственно;

- числа, представленные 50

своими рядами,

°,

ZI

П- 1

m старшими разх -2

где

При этом X X e{A,B,C,D,A,}i,C,D,E, х„е{1,0,

Q

1, Y -i y.,2,yetb0.1.

ег

(5)

1355974 . 4

Кроме того , , , D - 2- .

В исходном состоянии в соответствии с выражениями (6)-(12) в регистре 36 начальных условий записаны

в , D , в регистре 37 - Y

о

АО С

регистре 38 - единица. В регистрах коэффициентов 31.i, 32.i, 33.i, 34.i записаны соответственно А;, В, С., D. , в регистрах промежуточных резуль

татов 21,1, 22.1, в регистре 29.1, в регистрах 41 узлов формирования делимого и делителя 18.i, 19.i записаны нули, а в регистрах 43 и 49 узf5 лов формирования - единица в младшем

разряде.

Процесс вычисления Y,, i 1,N осуществляется в три этапа: на первом этапе - параллельно по алгоритмам

20 (6) и (7), на втором - параллельно по алгор 1тмам (8) и (9), на третьем- параллельно по-алгоритмам (10), (11), (12).

25

30

35

40

45

На первом этапе параллельно вычисляются коэффициенты А; и С , на втором - и D : , на третьем - Y . Первый и второй этапы осуществляются за 2k+ q циклов каждый, а

третий - за 4k+ q циклов.

В каждом т-м цикле (т 1,2q) вычислений первого (второго) этапа в соответствии с управляющим сигналом с входа 39 устройства происходит сдвиг регистра 36 начальных условий. На коммутаторы 23.р., 24 р., 25,р., 26.р., (j-1) k+i, поступают цифры

f m-2(i-1)j-ос разрядов А

CV

.R / p(f) ::(J-| . А ;., , С 1-, (В ,--, , D (., , Б (., , D ,-,, ;

соответственно, которые управляют вьщачей в младщие разряды сумматоров 1.Р, 2,р содержимого регистров З1.р, 32.р, 33,р, 34,р, р (j-1)k+i, таким образом, что в соответствии с алгоритмами (6) и (7), (8) и (9) на сумматоры 1.р, 2,р, р (j-1)k+i, выдается дополнительный код, если

m-2(i-1)-H цифра , , С 1,(Ё ,

D/., ) равна 1, прямой код, если цифра равна 1, удвоенный код, если цифра равна 2, и код не выдается, если соответствующая цифра равна О, Одно- временно cyMMaTqpbi Ю.р, 11.р, р (j-l)k+1, j i,k, осуществляют суммирование содержимого четырех стар- тих разрядов регистров сумм 4.р, 5.р и регистров переносов 7.р, В.р, р

(j-1)k+i, соответственно. Дешифраторы 15.Р, 16.Р анализируют три старших разряда полученных сумм и формируют m-2(i-1)-X разрядов

выходов узлов формирования 18.1 и 19.1 принимают коэ4)фициенты В., D. вычисленные на втором этапе. Сброс регистров 41 узлов 18.1 и. 19.1 происходит в соответствии с управляющим

А . ( , ), которые ана- сигналом (2k.+ 1)-ro выхода распределителя 35 импульсов, т.е. в начале логичным образом управляют выдачей

1кода с регистров коэффициентов 31.Р+1, 32.Р+1, ЗЗ.р+1, 34.Р+1

на

сумматоры 1.Р+1, 2.Р+1. Кроме того, дешифраторы 15.р и 16.р вьщают коды полученных цифр соответственно в узлы формирования делимого и делителя

третьего этапа.

Б т-м цикле вычислений третьего to этапа происходит сдвиг регистров 37 и 38 начальных условий, и на выходы коммутаторов 23.р, 25.р поступает цифра m-4(j-1)J-го разряда Y , а

Ап лг. ,на коммутаторы 24.р и 26.р - цифра 1

18.р, 19.р, которые формируют резуль- :,„ г чт 15 с выхода регистра 38, которые управляют выдачей в младшие разряды сумматоров 1.р и 2.р содержимого регистров 31.р, 32.р и 33.р, 34.р в соответствии с алгоритмами (10) и (11). Одновременно с этим на сумматоры Ю.р и 11.Р поступает содержимое регистров 4.р, 5.Р и 7.р, 8.Р, соответственно

тат в системе счисления 0;1j. Сдвиг регистра 43 этих узлов происходит по управляющему сигналу с выхода распределителя 35 импульсов. На сумматоры 1.Р и 2.р, р (j-1)k+i, поступают в соответствии с (6) и (7) следующие величины: коды содержимого регистров 4.Р, 5.Р, 7.р, 8.р, р (j-1)k+i, удвоенные цифры т-2 х

20

Р , (j-1)k+:L. Полученные коды

Н

И Н

поступают

П1-4 (J-1)-1

2 j ., . iYi-4 ()--l)-1

соответственно на дешифраторы 15

1, №- 4 ( - 1|-

поступает в Двухра

X (1-1)1-го разряда А , (В

(выдаются в два старших разряда Р которые формируют цифры сумматоров 1.Р и. 2.Р соответственно). 1 , (--o-i Vm-4( -i)-i -После окончания переходного процесса | ,м сформированные на выходах сумматоров 30 1 1.Р и 2.Р коды принимаются в виде поразрядных сумм и переносов в регистры сумм 4.Р, З.р и переносов 7.р, 8.р.

По окончании первого этапа, т.е. после выполнения 2k- - q циклов, в соответствии с управляющим сигналом с выхода распределителя 35 импульсов происходит сброс регистров 4.1, 5.1, 7.1, 8.1 и прием А ;, С; в регистры промежуточных результатов 21.1 и 22.1, с выходов узлов формирования делимого и делителя 18.1, 19.1, 1

ный регистр 29.р. Кроме того, на маторы 1.Р и 2.р в соответствии (10) и (11) поступают коды Н, ,

35 и (j-i)-i с выходов регистро

сумм и переносов 4.р, 7.р и З.р Р (j-1)k+i, и удвоенные цифры m-4(j-.1) разряда Е j и Е (вьщаются в два старших разряда) ле окончания переходного процесс сформированные на выходах суммат 1.р и 2.р коды принимаются в вид разрядных сумм и переносов в рег

40

сумм и переносов 4.р, 7.р и З.р, 8.р, Р (j-1)k+i, и удвоенные цифры m-4(j-.1) разряда Е j и (вьщаются в два старших разряда). После окончания переходного процесса сформированные на выходах сумматоров 1.р и 2.р коды принимаются в виде поразрядных сумм и переносов в регистКроме того, цифры

()Ч

(П - 1, W- i( j--()-i

1 N

регистра 41 узлов формирова-45 (j-1)k+i. ния 18.1 и 19.1 происходит в соответствии с управляюш51М сигналом с первого выхода распределителя 35 импульсов, т.е. в начале первого цикла второго этапа.J5Q мирования 18.р и 19.р соответственно.

По окончании второго этапа, т.е. которые формируют после выполнения 4k+ 2q+ 1 циклов с

.m- I (j-D-i

поступают в узлы .4(м-,

и R

b,w- 4 ()-()-

По управляющему сигначала работы устройства, в соответствии с управляющим сигналом с выхода

распределителя 35 импульсов происхо- „ ° распределителя 35 имдит прием в регистры 31 Л и 33.1 с пульсов происходит сдвиг регистра 43

выходов регистров 21.1 и 22.1 коэф- Р регистр 41 узлов формировафициентов Л., С;, вычисленных на пер- Р 19.Р вычисленных в преды1nvffiGM такте F

вом этапе, а регистры 32«i и 34,1 с ( iim-4(pii-a

выходов узлов формирования 18.1 и 19.1 принимают коэ4)фициенты В., D. вычисленные на втором этапе. Сброс регистров 41 узлов 18.1 и. 19.1 происходит в соответствии с управляющим

сигналом (2k.+ 1)-ro выхода распределителя 35 импульсов, т.е. в начале

ляют выдачей в младшие разряды с торов 1.р и 2.р содержимого реги 31.р, 32.р и 33.р, 34.р в соотве ствии с алгоритмами (10) и (11). новременно с этим на сумматоры Ю и 11.Р поступает содержимое реги 4.р, 5.Р и 7.р, 8.Р, соответстве

Р , (j-1)k+:L. Полученные коды

Н

П1-4 (J-1)-1

И Н

поступают

j ., . iYi-4 ()--l)-1

соответственно на дешифраторы 15.р и

Цифра

поступает в Двухразрядформируют цифры Vm-4( -i)-i

Р которые формируют цифры 1 , (--o-i Vm-4( -i)-i | ,м 1

ный регистр 29.р. Кроме того, на сумматоры 1.Р и 2.р в соответствии с (10) и (11) поступают коды Н, ,.

и (j-i)-i с выходов регистров

сумм и переносов 4.р, 7.р и З.р, 8.р, Р (j-1)k+i, и удвоенные цифры m-4(j-.1) разряда Е j и (вьщаются в два старших разряда). После окончания переходного процесса сформированные на выходах сумматоров 1.р и 2.р коды принимаются в виде поразрядных сумм и переносов в регист

Кроме того, цифры

()Ч

(П - 1, W- i( j--()-i

(j-1)k+i. мирования 18.р и 19.р соответственно

.m- I (j-D-i

поступают в узлы фор (j-1)k+i. .р соответственно

.4(м-,

и R

b,w- 4 ()-()-

По управляющему сигВ начале,(m+1)-го цикла по управляющему сигналу с выхода распределителя 35 импульсов содержимое регистра 41 узла формирования делителя 19.р поступает в регистр 30.р; регистр 29.р передает цифру ,,. ,, , в

I, т- it(j-i)-i

два старших разряда сумматора 3.pj а

. j

цифра г i,- + (j.,,..

управляет вьщачей

через коммутатор 27.р на сумматор З.р содержимого сумматора 48

(Y

Ып-4 ()-1)- 3

) узла формирования

частного 20.Р, р (j-1). Кроме того, на сумматор З.р с выходов регистров сумм 6.Р и переносов 9.р поступает удвоенный код Н „.4(j-f|-i Одновременно по управляющему сигналу с выхода распределителя 35 импульсов содержимое регистров б.р и 9.р поступает на вход сумматора 12.р, который передает полученный код на сумматоры 13.Р и 14.р. На эти сумматоры также поступает содержимое регистра

зо.р/к /,,.,(..„.,

вычисляет Н

n-4(f-i)-2

а сумматор 14.р - H.j.,,,j

-

,п,-4(,-м)-2

Первые разряды полученных поступают.на вход дешифратора 17.р,

который формирует цифру Y .

1, т- f (j-i)-2

Полученная цифра управл яет вьщачей на сумматор З.р кода R

«J)

(j-l)-2

ИЗ регистра 41 узла формирования делителя 19.р, p(j-1)k+1, поступающего также в узел формирования частного 20.р, которьй формирует код

ь т-4- (j-il-2

сления.

в двоичной системе счиПоеле окончания переходного процесса сформированный на выходе сумk N,j-1k), ()-й и

(2k+2j)-й выходы распределителя им

матора З.р код принимается в виде по- 50 пульсов соединены соответственно с

разрядных сумм и переносов в регистры б.р и 9.р.

Кроме того, цифра Y

tjl

входами стробирования выборки реги ров сумм делимого и вторыми входам сдвига узлов формирования делимого

управляет выдачей с регистров 31.p+k и ЗЗ.р+k коэффициентов A f и С / на сумматоры 1.p+k и 2.p+k, р (j-1)k+i.

k.m- + (j-,-2 55 (j-1)-k+1, (, ..., j.kj-го

вычислительных блоков, первый и C2k+1)-й выходы распределителя импульсов соединены соответственно с

Формула изобретения

Вычислительное устройство, содержащее первый регистр начальных значений, распределитель импульсов и N вычислительных блоков (N - размерность массивов аргументов и результата) , каждый из которых содержит сумматор коэффициентов делимого, регистр суммы делимого, коммутатор первого коэффициента делимого, регистр первого коэффициента делимого, дешифратор делимого, узел формирования делимого и регистр промежуточного результата делимого, причем выход регистра первого коэффициента делимого i-ro вычислительного блока (, ..., N) соединен с первым информационным входом коммутатора первого

коэффициента делимого этого блока,

выход коммутатора первого коэффициft . ента делимого г-го вычислительного

блока соединен с входом первого слагаемого сумматора коэффициента дели- мого этого блока, вход второго слагаемого сумматора коэффициента делимого

i-ro вычислительного блока соединен с выходом регистра суммы делимого этого блока, выход узла формирования

делимого i-ro вычислительного блока соединен с информационным входом регистра промежуточного результата этого блока, первый выход дешифратора делимого i-ro вычислительного блока

соединен с входом третьего слагаемого сумматора коэффициента делимого этого блока, вход запуска устройства соединен с входом сдвига первого регистра начальных условий и входом запуска распределителя импульсов,

(2j-1)-й и 2з-й выходы которого соединены соответственно с синхронизирующими входами регистров сумм делимого и первыми входами сдвига узлов

формирования делимого (j,k+j, ..., k(k-1)+j)-ro вычислительных блоков,

k N,j-1k), ()-й и

(2k+2j)-й выходы распределителя импульсов соединены соответственно с

входами стробирования выборки регистров сумм делимого и вторыми входами сдвига узлов формирования делимого

вычислительных блоков, первый и C2k+1)-й выходы распределителя импульсов соединены соответственно с

91

первым и вторым входами сброса узлов формирования делимого вычислительных блоков с первого по N-й, (4k+1)-ft выход распределителя импульсов соединен с синхронизирующими входами регистра промежуточных результатов делимого вычислительных блоков с первого по N-й, (4k+2)-u выход распределителя импульсов соединен с синхронизирующими входами регистров первог коэффициента делимого и регистров сумм делимого вычислительных блоков с первого по N-й, отличают; е- е а я тем, что, с. целью расширения класса решаемых задач за счет обес- печения возможности вычисления выра- жения Y, (АЛ, . + B;)/(C,Y, + D.

+ В .)/(C,Y.

1 1 1-1 I 1 1-1 в него введены второй и третий.регистры начальных значений, а в каждый вычислительный блок введены сумматор коэффициента делителя, регистр переноса делимого, регистр второго коэффициента делимого, коммутатор второго коэффициента делимого,°сум

матор делимого, регистр первого коэф-25 блока соединены с вторым и третьим фициента делителя,, коммутатор перво- информационными входами коммутаторов

и

го {коэффициента делителя, регистр второго коэффициента делителя, коммутатор второго коэффициента делителя, регистр суммы делителя, регистр переноса делителя, сумматор делителя. Дешифратор делителя, узел формиро- вания делителя, регистр промежуточного результата делителя, регистр

соответственно первого и второго коэффициентов делимого этого блока, прямые выходы регистров первого и 30 второго коэффициентов делителя 1-го

вычр слительного блока соединены с первыми информационными входами коммутаторов соответственно первого и второго коэффициентов делителя этого

делителя, первый коммутатор частного, , блока, выходы коммутаторов первого второй кбм ryтaтop частного, первый и второго коэффициентов делителя 1-го

суммы

сумматор частного, регистр частного, регистр переноса частного, второй сумматор частного, третий сумматор частного, четвертый сумматор 40 частного, дешифратор частного и узел формирования частного, причем выход регистра второго коэффициента делимого i-ro вычислительного блока соединен с первым информационным входом коммута- 45 тора второго коэффициента делимого этого блока, выход коммутатора второго коэффициента делимого i-ro вычислительного блока соединен с входом четвертого слагаемого сумматора коэффи- Q -циентов делимого этого блока, вход пятого слагаемого сумматора коэффициентов делимого i-ro вычислительного блока соединен с выходом регистра переносов делимого этого блока, первый и второй выходы сумматора ко- эффи1щентов делимого i-ro вычислительного блока соединены с информа- 1ционными входами соответственно рет

55

вычислительного блока соединены с входами первого и второго слагаемьк сумматора коэффициентов делителя, входы третьего и четвертого слагаемых сумматора коэффициентов делителя i-ro вычислительного блока соединены с выходами соответственно1 регистров сумм и переносов делителя этого блока, первый и второй выходы сумматора коэффициентов делителя i-ro вычислительного блока соединены с информационными входами соответственно регистра суммы и переносов делителя этого блока, выходы которых соединены с входами первого и второго слагаемых сумматора делителя этого блока, выход сумматора делителя i-ro вычислительного блока соединен с входами дешифратора делителя этого блока, выходы с первого по третий и четвертый выход дешифратора делителя i-ro вычислительного блока соединены соответственно с информационными входами

10

5

0

гистров суммы и переносов делимого этого блока, выходы регистров суммы и переноса делимого i-ro вычислительного блока соединены соответственно с входами первого и второго слагаемых сумматора делимого этого блока, выход сумматора делимого i-ro вычислительного блока соединен с входом дешифратора делимого этого блока, выходы с первого по третий дешифратора делимого i-ro вычислительного блока соединены с информационными входаьи узла формирования делимого этого блока, выходы узла формирования делимого и регистра промежуточных результатов делимого i-ro вычислительного блока соединены соответственно с информационными входами второго и первого регистров коэффициентов делимого этого блока, инверс- ные выходы и выходы со сдвигом на один разряд в сторону старших разря,-. дов первого и второго регистров коэффициентов делимого вычислительного

и

соответственно первого и второго коэффициентов делимого этого блока, прямые выходы регистров первого и 30 второго коэффициентов делителя 1-го

вычр слительного блока соединены с первыми информационными входами коммутаторов соответственно первого и второго коэффициентов делителя этого

5 Q

5

вычислительного блока соединены с входами первого и второго слагаемьк сумматора коэффициентов делителя, входы третьего и четвертого слагаемых сумматора коэффициентов делителя i-ro вычислительного блока соединены с выходами соответственно1 регистров сумм и переносов делителя этого блока, первый и второй выходы сумматора коэффициентов делителя i-ro вычислительного блока соединены с информационными входами соответственно регистра суммы и переносов делителя этого блока, выходы которых соединены с входами первого и второго слагаемых сумматора делителя этого блока, выход сумматора делителя i-ro вычислительного блока соединен с входами дешифратора делителя этого блока, выходы с первого по третий и четвертый выход дешифратора делителя i-ro вычислительного блока соединены соответственно с информационными входами

II1

узла формирования делителя и входом пятого слагаемого сумматора коэффициентов делителя этого блока, выход узла формирования делителя i-ro вычислительного блока соединен с информационными входами регис тра промежуточного результата делителя этого блока, выходы регистра промежуточного результата делителя и узла формирования делителя i-ro вычислител ьно- го блока соединены с информационными входами регистров соответственно первого и второго коэффициентов делителя этого блока, инверсные выходы и выходы со сдвигом на один разряд в сторону старших разрядов первого и второго регистров коэффициентов делителя i-ro вычислительного блока соединены с вторым и третьим информационными входами коммутаторов соответственно первого и второго коэффициентов делителя этого блока, выходы с первого rto третий дешифратора дели

мого т-го вычислительного блока (т

1,N, m т j, k, j 1 ,k) соединены с первыми управляющими входами коммутаторов первых коэффициентов соответственно делимого и делителя (т+1)-го вычислительного блока, выходы с зо первого по третий дешифратора делителя т-го вычислительного блока соединены с первыми управляющими входами коммутаторов вторых коэффициентов

cyNfMaTopa частного i-ro вычислител ного блока соединены соответственн с выходами регистра суммы и перено частного этого блока, первый и втор выходы первого сумматора частного iro вычислительного блока соединен с информационными входами соответственно регистра суммы и переноса частного этого блока, выходы регист суммы и переноса частного i-ro вычи лительного блока соединены с входам соответственно первого и второго сл гаемы с второго сумматора частного этого блока, первый и второй выходы второго сумматора частного соединен с входами первых слагаемых соответ ственно третьего и четвертого сумма торов частного этого блока, выходы третьего и четвертого сумматоров час ного i-ro вычислительного блока сое динены с входами дешифратора частно го этого блока, выход дешифратора частного i-rro вычислительного кода соединен с информационным входом уз 25ола формирования частного и управля ющим входом узла формирования комму татора частного, выход узла формиро вания частного i-ro вычислительного блока соединен с первым информацион ным вxoдo l первого коммутатора част ного этого блока, выход регистра де лителя соединен с входами вторых сл гаемых третьего и четвертого сумматоров частного, выход дешифратора

делимого и делителя (т+1)-го вычисли-, частного R-ro вычислительного блока тельного блока, четвертый и пятый ( 2k, .;., k{k-1))J соединен с выходы дешифратора делимого i-ro вы- вторыми управляющими входами комму- числительного блока соединены с информационными входами регистра дели40

мого этого блока, выходы с п.ерво го по третий дешифратора делителя i-ro вычислительного блока соединены с управляющим входом первого коммутатора частного этого блока, выход узла формирования делителя i-ro вычислительного блока соединен с информационным входом регистра делителя и первым информационным входом второго коммутатора частного этого блока, выход регистра делимого i-ro вычислительного блока соединен с входом первого слагаемого первого сумматора частного этого блока, входы второго и третьего слагаемых первого сумматора частного i-ro вычислительного блока соединены с выходами соответственно первого и второго коммутаторов частного этого блока, входы четвертого и пятого слагаемых первого

45

таторов первого коэффициента делимого и делителя вычислительных блоков с (i+1)-ro по (i+k)-й, первый выход первого регистра начальных условий соединен с первыми yпpaвляющи ш входами коммутаторов первых коэффициентов делимого и делителя 1-х вычислительных блоков (1 1, k+1, ...,k(k + +1)+1), второй выход первого регистра начальных условий соединен с первыми управляющими входами коммутаторов вторых коэффициентов делимого и CQ делителя 1-х вычислительных блоков, выход второго регистра начальных условий соединен с вторыми управляющим входами коммутаторов первых коэффиделителя вычйсли55

циентов делимого и

отельных блоков с первого по k-й, выход трет ьего регистра начальных усло вий соединен с вторыми управляющими входами коммутаторов втсазых коэффициентов делимого и делителя с первог

5974

5

о

12

cyNfMaTopa частного i-ro вычислительного блока соединены соответственно с выходами регистра суммы и переноса частного этого блока, первый и второй выходы первого сумматора частного iro вычислительного блока соединены с информационными входами соответственно регистра суммы и переноса частного этого блока, выходы регистра- суммы и переноса частного i-ro вычислительного блока соединены с входами соответственно первого и второго сла- гаемы с второго сумматора частного этого блока, первый и второй выходы второго сумматора частного соединены с входами первых слагаемых соответственно третьего и четвертого сумматоров частного этого блока, выходы третьего и четвертого сумматоров частного i-ro вычислительного блока соединены с входами дешифратора частного этого блока, выход дешифратора частного i-rro вычислительного кода соединен с информационным входом уз- 5ола формирования частного и управляющим входом узла формирования коммутатора частного, выход узла формирования частного i-ro вычислительного блока соединен с первым информационным вxoдo l первого коммутатора частного этого блока, выход регистра делителя соединен с входами вторых слагаемых третьего и четвертого сумматоров частного, выход дешифратора

0

, частного R-ro вычислительного блока ( 2k, .;., k{k-1))J соединен с вторыми управляющими входами комму-

40

45

таторов первого коэффициента делимого и делителя вычислительных блоков с (i+1)-ro по (i+k)-й, первый выход первого регистра начальных условий соединен с первыми yпpaвляющи ш входами коммутаторов первых коэффициентов делимого и делителя 1-х вычислительных блоков (1 1, k+1, ...,k(k + +1)+1), второй выход первого регистра начальных условий соединен с первыми управляющими входами коммутаторов вторых коэффициентов делимого и CQ делителя 1-х вычислительных блоков, выход второго регистра начальных условий соединен с вторыми управляющим входами коммутаторов первых коэффиделителя вычйсли55

циентов делимого и

отельных блоков с первого по k-й, выход трет ьего регистра начальных условий соединен с вторыми управляющими входами коммутаторов втсазых коэффициентов делимого и делителя с первог

по N-й, (2j-1)-ft выход распределителя импульсов соединен с синхронизирующими входами регистров переносов . делимого, регистров переносов делителя и регистров суммы делителя ( j (k-D k+j)-X вычислительных блоков, 2j-u выход распределителя импульсов соеди нен с синхронизирующим входом (j,j+k, , .. (k-1) k+j) узЛов формирования делителя (j 1,k), (2k+j)-ft выход распределителя импульсов соединен с входами стробирования выборки регистров сумм делителя, регистров переносов делимого и регистров переносов делителя (j-1) k+1, (j-1)k+2, ,..., j,kj-x вычислительных блоков, (3k+j)-ft выход распределителя импульсов соединен с первыми входами сдвига узлов формирования делителя (j-1)k+1, (j-1)k+2 ,,..., j, вычислительных блоков, (4k+j+2)-ft выход распределителя импульсов соединен с синхронизирующими входами регистров сумм и переносов частного и

и входом сдвига второго регистра начальных условий, (6k+4)-ft выход распределителя импульсов соединен с информационными входами коммутаторов

с первого и второго коэффициентов делимого и делителя вычислительных блоков с перво.го по N-й, выход дешиф ратора частного является 1-м выходом устройства, причем каждый узел мирования частного содержит накапливающий сумматор, коммутатор и регист сдвига, причем вход сдвига узла формирования частного соединен с входом сдвига регистра сдвига, выход,кото15 рого соединен с управляющим входом коммутатора, информационные входы которого соединены с информационными входами узла, выход коммутатора соединен с информационным входом накап

20 ливающего сумматора, выход которого соединен с выходом узла формирования частного, причем каждый из узлов фор мирования делимого и делителя содержит регистр, накапливающий сумматор.

регистров делимого и делителя (j-1)x25 сдвиговый регистр, коммутатор и три

элемента ИЛИ, причем первый и второй входы сброса узла формирования делимого и делителя соединены соответственно с первым и вторым входами (41с+1)-й выход распре- 0 первого элемента ШМ, выход которого

Kk+ 1, (j-1)k+2, . .,, j ,k -x вычислительных блоков, (5k + j+2)-й выход распределителя импульсов соединен с вторым входом сдвига узлов формирования частного, делителя импульсов соединен с входами сброса регистров сумм и переносов делителя и регистров переноса делимого и синхронизирующим входом регистра промежуточных результатов делите- 35 ля вычислительных блоков с первого по N-й, (4k+2)-E выход распределителя импульсов соединен с синхронизирующими входами первого и второго коэффициентов делителя, регистров вто- 40 рого коэффициента делимого, регистров сумм и переносов делителя, регистров переносов делимого вычислительных блоков с первого по N-й, (6k+3)-E выход распределителя импульсов сое- 45 дивен с управляющими входами коммутаторов первого и второго коэффициентов делимого и делителя, первого и второго коммутаторов частного вычислительных блоков с первого по N-й ,

соединен с входом сброса регистра, синхронизирующий вход которого соединен с выходом второго элемента ИЛИ, первый и второй входы которого объединены с первым и вторым входами третьего элемента ИЛИ и соединены соответственно с первым и вторым входами сдвига узла формирования делимого и делителя, информационный вход регистра соединен с выходом накапливающего сумматора, информаЕ,ионный вход которого соединен с выходом коммутатора, управляющий вход которого Соединен с выходом регистра сдвига, вход сдвига которого соединен с выходом третьего элемента ИЛИ, информационные входы коммутатора соединены с инфор- мационны1 1и входами узла формирования делимого и делителя,

и входом сдвига второго регистра начальных условий, (6k+4)-ft выход распределителя импульсов соединен с информационными входами коммутаторов

первого и второго коэффициентов делимого и делителя вычислительных блоков с перво.го по N-й, выход дешифратора частного является 1-м выходом устройства, причем каждый узел формирования частного содержит накапливающий сумматор, коммутатор и регистр сдвига, причем вход сдвига узла формирования частного соединен с входом сдвига регистра сдвига, выход,которого соединен с управляющим входом коммутатора, информационные входы которого соединены с информационными входами узла, выход коммутатора соединен с информационным входом накапливающего сумматора, выход которого соединен с выходом узла формирования частного, причем каждый из узлов формирования делимого и делителя содержит регистр, накапливающий сумматор.

элемента ИЛИ, причем первый и второй входы сброса узла формирования делимого и делителя соединены соответственно с первым и вторым входами первого элемента ШМ, выход которого

соединен с входом сброса регистра, синхронизирующий вход которого соединен с выходом второго элемента ИЛИ первый и второй входы которого объединены с первым и вторым входами третьего элемента ИЛИ и соединены соответственно с первым и вторым входами сдвига узла формирования делимого и делителя, информационный вход регистра соединен с выходом накапливающего сумматора, информаЕ,ионный вход которого соединен с выходом коммутатора, управляющий вход которого Соединен с выходом регистра сдвига, вход сдвига которого соединен с выходом третьего элемента ИЛИ, информационные входы коммутатора соединены с инфор- мационны1 1и входами узла формирования делимого и делителя,

с

л

Редактор И.Рыбченко

Составитель С.Куликов

Техред А.Кравчук Корректор Г.Решетник

Заказ 5794/42Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

50

45

Фиг. /

| название | год | авторы | номер документа |

|---|---|---|---|

| Конвейерное устройство для деления | 1985 |

|

SU1297037A1 |

| Устройство для деления чисел | 1981 |

|

SU1056183A1 |

| Устройство для деления | 1985 |

|

SU1322264A1 |

| Делительное устройство | 1986 |

|

SU1335980A1 |

| Устройство для деления | 1988 |

|

SU1541598A1 |

| Устройство для деления | 1990 |

|

SU1709352A1 |

| Устройство для деления | 1990 |

|

SU1783522A1 |

| Устройство для деления чисел | 1981 |

|

SU1119006A1 |

| Вычислительное устройство | 1988 |

|

SU1532917A1 |

| Устройство для деления чисел | 1980 |

|

SU907544A1 |

Изобретение относится к области вычислительной техники и может быть использовано в специализированных вычислителях в системах многомерной обработки информации. Целью изобретения является расширение класса ре- „шаемых задач за счет возможности вычисления выражения Yj, ( , + + B;)(CjY,+ D.) (i 1, ... N, N - размерность массивов аргументов и результатов). Устройство содержит N со ел ел со 4;;

| Устройство для сложения в избыточной двоичной системе счисления | 1978 |

|

SU686030A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1154667, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-11-30—Публикация

1986-07-23—Подача