V.

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

| Конвейерное устройство для деления | 1985 |

|

SU1297037A1 |

| Устройство для деления чисел с фиксированной запятой | 1986 |

|

SU1417009A1 |

| Устройство для деления двоичных чисел | 1988 |

|

SU1617437A1 |

| Устройство для деления | 1984 |

|

SU1259251A1 |

| Устройство для деления | 1984 |

|

SU1242935A1 |

| Устройство для деления последовательных чисел | 1987 |

|

SU1462298A1 |

| Устройство для деления | 1990 |

|

SU1809438A1 |

| Устройство для деления | 1985 |

|

SU1265763A1 |

| Устройство для деления | 1990 |

|

SU1709352A1 |

Изобретение относится к вычислительной технике и может использоваться в системах тестового и функционального диагностирования ЭВМ. Цель изобретения - расширение функциональных возможностей. Устройство содержит п вычислительных блоков 1, каждый из которых имеет в своем составе регистры делимого 2, делителя 3 и частного 7, блок 4 сложения, два мультиплексора 6.1 и 6.2, группу эле1- метов 211-ИЛИ 8, а также группу эле

Cfc

to

оо

Ј

16

фиг.1

ментоо ИСКЛЮЧАЮЩЕЕ ИЛИ 9 и мультиплексор 10. Переключение устройства для деления в режим сигнатурного анализатора позволяет улучшить диагно- стические возможности вычислительных систем, в составе которых используется устройство для деления, и сократить время тестирования самого устройства. Сокращение времени тести- рования достигается за счет возможности формирования в устройстве сигнаИзобретение относится к вычислительной технике и может быть использовано в качестве блока деления в конвейерных цифровых вычислительных машинах, а также в цифровых системах контроля и управления.

Цель изобретения - расширение функциональных возможностей за счет работы в режиме конвейерного сигнатурного анализатора.

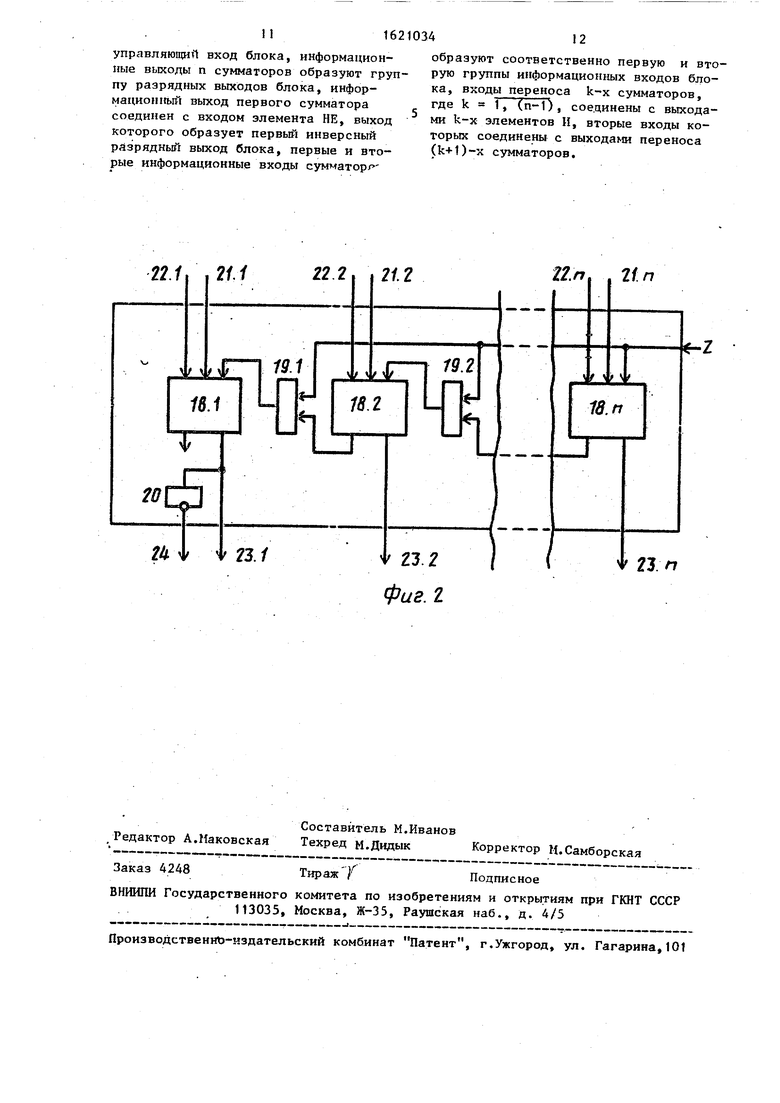

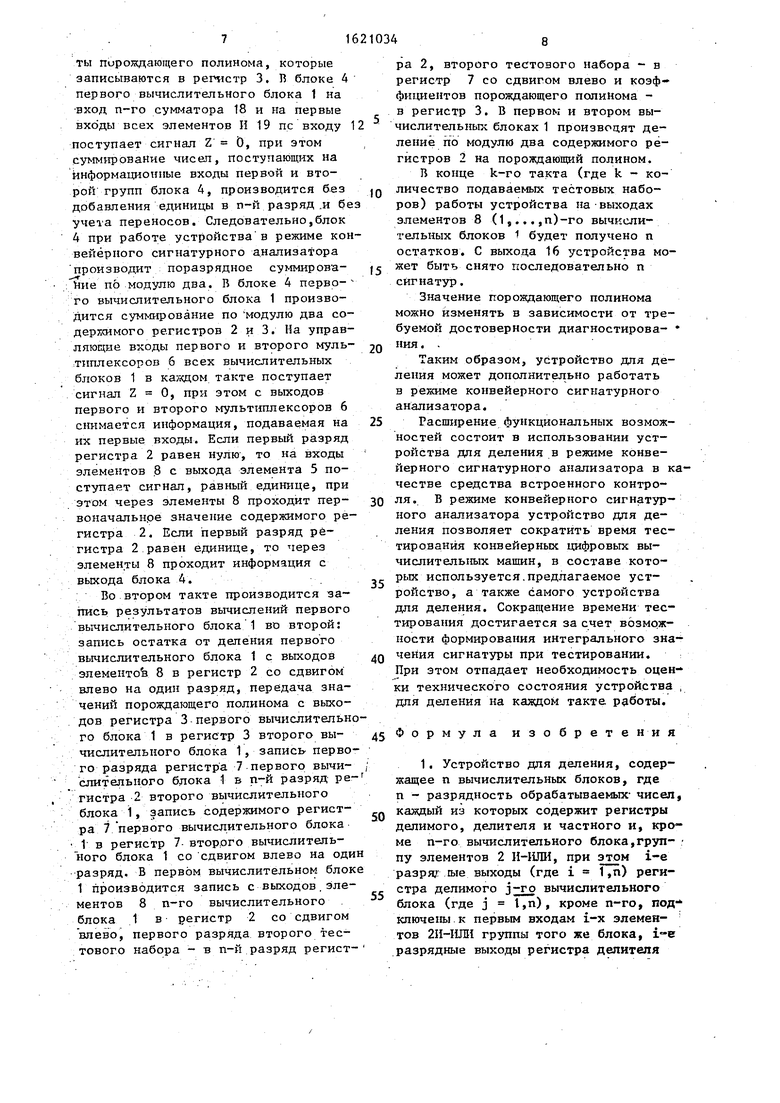

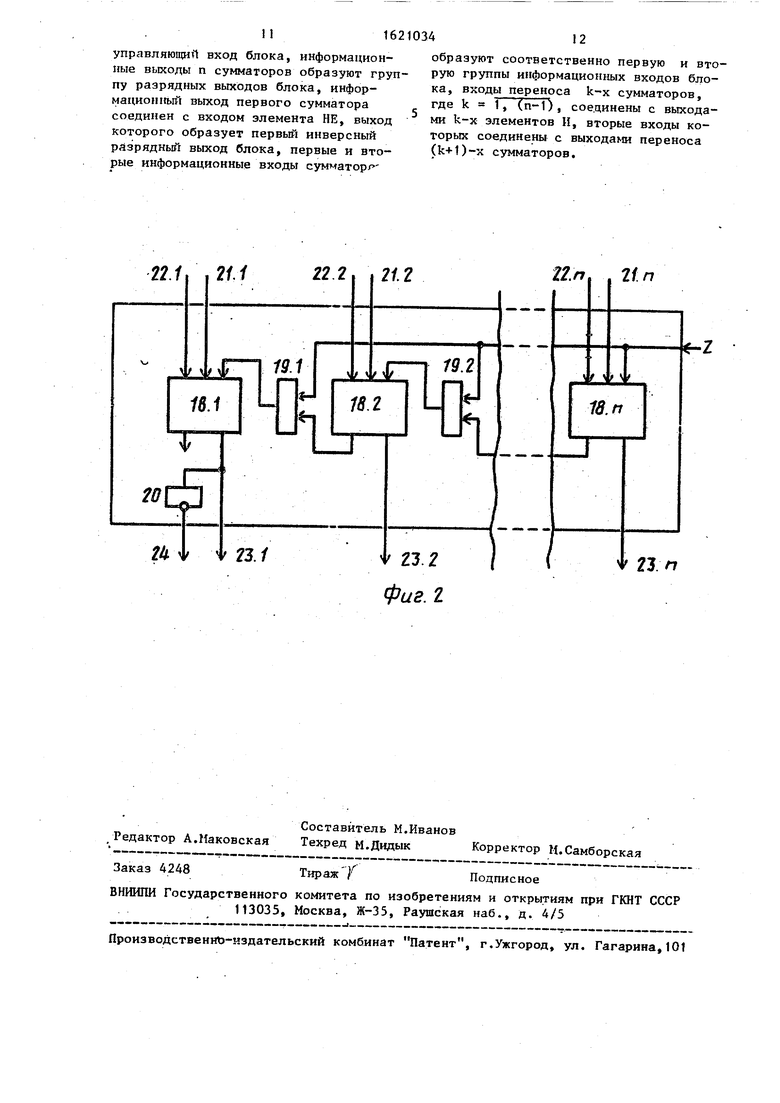

На фиг.1 представлена структурная схема устройства для деления; на фиг.2 -г функциональная схема блока сложения.

Устройство содержит п вычислительных блоков 1.1...1.п, каждый из которых содержит регистр 2 делимого, регистр 3 делителя, блок 4 сложения, элемент .НЕ 5, два мультиплексора 6.1 и 6.2, регистр 7 частного, группу элементов 2И-1ШИ 8. Кроме того, устройство содержит группу элементов ИШСЛЮЧАЩЕЕ ИЛИ 9, мультиплексор 10, вход 11 сброса, вход 12 режима работы устройства, группы информационных входов 13-15, группу выходов 16,17.

Блок 4 сложения содержит п одноразрядных комбинационных сумматоров 18.1...18.п,(п-1) элементов И 19,эле- . мент НЕ 20, первую группу информационных входов 21.1...21.П, вторую группу информационных входов 22.1...22.П, группу разрядных выходов 23.1...23.П, первый инверсный разрядный выход 24. Устройство работает следующим образом.

При работе в режиме делителя на вход 12 устройства подается сигнал .2, равный логической единице. При поступлении сигнала Z 1 на вход мультиплексора 10 он пропускает на свои

туры, являющейся интегральной оценкой исправности вычислительной системы, в составе которой используется устройство для деления,а также самого устройства. Введение режима сигнатурного анализатора в устройство дает возможность использовать последнее в качестве средства встроенного контроля в вычислительной системе. 1 з.п. ф-лы, 2 ил.

выходы код с входов 13. Перед началом деления чисел производится начальная установка регистров устройства путем подачи на вход 11 сигнала сброса. Деление выполняется с восстановлением остатка за k тактов.1

в первом такте в регистр 2 делимого первого вычислительного блока 1.1 через вход 13 устройства записывают первое делимое со сдвигом влево на один разряд. На первые входы группы элементов по входу 12 поступает сигнал Z 1} на вторые входы элементов 9 по входу 15 устройства поступают сигналы, cooTBeTcfвующие разрядам первого делителя, при этом на

выходах элементов 9 формируется инверсный код первого делителя, соот- ветствюуший обратному коду делителя. В блоке 4 производится вычитание из делителя, который преобразован в дополнительный код, при этом сигнал Z 1 по входу 12 поступает на вход n-го сумматора 18.1 блока 4, обеспечивая преобразование обратного кода делителя в дополнительный путем добавления 1 в n-й разряд блока 4, На выходе 1-го сумматора 18 блока 4 формируется сигнал переноса, который передается на второй вход (i-l)-ro элемента-И 19, на первый вход которо-

го подается сигнал , при этом на выходе (i-l)-ro элемента И 19 получают сигнал, соответствующий сигналу переноса с выхода 1-го сумматора - Я, который передается на

вход (i-l)-ro сумматора 18. На первые входы 1-х сумматоров 18 блока 4 по входам 21 поступают сигналы разрядов делимого с 1-го выхода регистра 2 делимого вычислительного блока

1, а на вторые входы тех же сумматоров 18 по входам 22 - сигналы разрядов обратного кода делителя с выхода 1-го разряда регистра 3 делителя вычислительного блока 1; сигнал с выхода первого сумматора 18 поступает на вход элемента НЕ 20, на выходе которого формируете сигнал,инверсный знаковому разряду. На управляющие входы первого и второго мультиплексоров 6 всех вычислительных блоков 1 в каждом такте по входу 12 поступает сигнал Z 1, при этом с выходов первого и второго мультиплексоров б снимается информация, подаваемая на вторые входы соответствующих мультиплексоров 6. Если остаток от вычитания из делимого делителя в блоке 4 полупился положительным, то разряд частного на выходе 24 блока 4 равен единице и через второй вход второго мультиплексора 6 на входы группы элементов 8 поступает сигнал, равный единице, при этом информация с выходов 23 блока 4 проходит на выходы элементов 8. Если остаток отрицательный, то разряд частного на выходе 24 блока 4 равен нулю и через второй вход первого мультиплексора 6 на входы группы элементов 8 с выхода 23.1 блока 4 поступает сигнал, равный единице, при этом через элементы 8 проходит первоначальное значение делимого из регистра 2 делимого, т.е. происходит восстановление остатка. Во втором такте производится запись результатов вычислений первого вычислительного блока 1 во второй, запись кода с выходов элементов 8 в регистр делимого со сдвигом влево, передача значения первого делителя в регистр 3 делителя, запись первого разряда частного с инверсного выхода 24 знакового разряда блока 4 в n-й разряд регистра 7 частного первого вычислительного блока 1. Одновременно в регистр 2 делимого и регистр 3 делителя поступают значения второй пары чисел. В первом вычислительном блоке 1 осуществляется деление второй пары чисел, а во втором получают результат деления первой пары чисел. В третьем такте результаты вычислений, полученные во втором вычислительном блоке 1, записывают в третий вычислительный блок 1, а результаты первого вычислительного блока 1 - во второй. П освободившиеся регистр 2 делимого и регистр 3 делителя первого вычислительного блока 1 поступает третья пара чисел. Первый разряд частного от деления второй пары чисел записывается в регистр 7 частного первого вычислительного блока 1, в регистр 7 частного второго вычислительQ ного блока 1 со сдвигом влево в (п-1)-й разряд.

Результат деления каждой пары чисел образуется за k тактов, при этом результат деления первой пары чисел

5 получен на выходах регистра 7 частного п-го пычислительного блока 1 через k тактов, а каждый последующий результат - через один такт. Знак частного определяется путем сложения

0 по модулю два знаковых разрядов делимого и делителя (на фиг.1 не показаны) .

При работе устройства в режиме . конвейерного сигнатурного анализато5 ра на вход 12 режима работы устройства подается сигнал Z 0, При поступлении сигнала Z Э на вход мультиплексора 10 на его выходы проходит код с выходов 16. Конвейерный сигна0 турный анализатор работает на основе деления полиномов по модулю два. Перед подачей тестовых наборов в устройство производится начальная установка регистров устройства путем подачи на вход 11 сигнала сброса .Очередной тестовый набор подается по входу 14 устройства в регистр 7 первого вычислительного блока 1 со сдвигом влево на один разряд, на вход

д n-го разряда регистра 2 первого вычислительного блока 1 подается первый разряд очередного тестового набор а, коэффициенты порождающего полинома по входу 15 устройства постуС пают на вторые входы элементов 9.

В первом такте работы устройства информация с выходов элементов 8 п-го вычислительного блока 1 через мультиплексор 10 записывается в регистр 2

о первого вычислительного блока 1 со сдвигом влево на один разряд, в п-й разряд регистра 2 первого вычислительного блока 1 записывается перпый разряд первого тестового набора, в per гистр 7 - первый тестовый набор со сдвигом влево на один разряд.На первые входы элементов 9 устройства поступает сигнал Z 0, на вторые входы элементов 9 поступают коэффициен5

ты пирождающего полинома, которые записываются в регистр 3. В блоке 4 первого вычислительного блока 1 на вход n-го сумматора 18 и на первые входы всех элементов И 19 пс входу 1 поступает сигнал Z О, при этом суммирование чисел, поступающих на информационные входы первой и второй групп блока 4, производится без добавления единицы в n-й разряд и бе учеча переносов. Следовательно,блок 4 при работе устройства в режиме конвейерного сигнатурного анализатора производит поразрядное суммирова- йие по модулю два. В блоке 4 перво-х го вычислительного блока 1 производится суммирование по модулю два содержимого регистров 2 и 3. На управляющие входы первого и второго нуль- тнплексоров б всех вычислительных блоков 1 в каждом такте поступает сигнал , при этом с выходов первого и второго мультиплексоров 6 снимается информация, подаваемая на их первые входы. Если первый разряд регистра 2 равен нулю, то на входы элементов 8 с выхода элемента 5 поступает сигнал, равный единице, при этом через элементы 8 проходит пер- воначальное значение содержимого регистра 2. Если первый разряд регистра 2 равен единице, то через элементы 8 проходит информация с выхода блока 4.

Во втором такте производится запись результатов вычислений первого вычислительного блока 1 во второй: запись остатка от деления первого вычислительного блока 1 с выходов элементов 8 в регистр 2 со сдвигом влево на один разряд, передача значений порождающего полинома с выходов регистра 3 первого вычислительного блока 1 в регистр 3 второго вы- числительного блока 1, запись первого разряда регистра 7 первого вычи- слителыюго блока 1 в n-й разряд регистра 2 второго вычислительного блока 1, запись содержимого регист- ра 7 первого вычислительного блока 1 в регистр 7 второго вычислитель- ного блока 1 со сдвигом влево на оди разряд. В первом вычислительном блок 1 производится запись с выходов элементов 8 n-го вычислительного блока 1 в регистр 2 со сдвигом влево, первого разряда второго тестового набора - в n-й разряд регист-

Q 5 0 5 0 5

о 5

5

ра 2, второго тестового набора - в регистр 7 со сдвигом влево и коэффициентов порождающего полинома - в регистр 3. В первом и втором вычислительных блоках 1 производят деление по модулю два содержимого регистров 2 на порождающий полином.

R конце k-ro такта (где k - количество подаваемых тестовых наборов) работы устройства на выходах элементов 8 (1,...,п)-го вычислительных блоков 1 будет получено п остатков. С выхода 16 устройства может быть снято последовательно п сигнатур.

Значение порождающего полинома можно изменять в зависимости от требуемой достоверности диагностирова- иия. .

Таким образом, устройство для деления может дополнительно работать в режиме конвейерного сигнатурного анализатора.

Расширение функциональных возможностей состоит в использовании устройства для деления в режиме конвейерного сигнатурного анализатора в качестве средства встроенного контроля, В режиме конвейерного сигнатурного анализатора устройство для деления позволяет сократить время тестирования конвейерных цифровых вычислительных машин, в составе которых используется предлагаемое устройство, а также самого устройства для деления. Сокращение времени тестирования достигается за счет возможности формирования интегрального значения сигнатуры при тестировании. При этом отпадает необходимость оценки технического состояния устройства , для деления на каждом такте работы.

Формула изобретения

каждого вычислительного блока подклю- чны к i-м информационным входам регистра делителя последующего вычислительного блока, 1-е разрядные выходы регистра частного каждого вычислительного блока подключены к (г-1)-м информационным входам регистра частного последующего вычислительного блока, выходы 1-х элементов 2И-ШШ группы j-ro вычислительного блока, кроме n-го, соединены с (1-1)-ми информационными входами регистра делимого (j+1)-ro вычислительного блоотличающееся тем,

ка.

что, с целью расширения функциональных возможностей за счет работы в репиме конвейерного сигнатурного анализатора, в каждый вычислительный блок введены блок сложения, элемент НЕ, два мультиплексора, в n-й вычислительный блок введена группа элементов 2И-11ЛИ, в устройство введены группа элементов ИСКЛПЧАКЩЕЕ ИЛИ и мультиплексор, причем первый разрядный выход регистра делимого каждого вычислительного блока соединен с входом элемента НЕ и с первым информационным входом первого мультиплексора того же блока, группа разрядных иыхо- дов регистра делимого каждого вычислительного блока соединена с пертюй группой информационных входов блока сложения того же блока,.группа разрядных выходов регистра делителя каждого вычислительного блока соединена с второй группой информационных входов блока сложения того же блока, выход элемента НЕ каждого вычислительного блока соединен с первым информационным входом первого мультиплексора того же блока, первый прямой разрядный выход блока сложения каждого вычислительного блока соединен с вторым информационным входом второго мультиплексора того же блока, первый инверсный разрядный выход блока сложения каждого вычислительного блока соединен с вторым информационным входом первого мультиплексора и с п-м информационным входом регистра частного того же блока, первый разрядный выход регистра частного j-ro вычислительного блока, кроме n-го вычислительного блока,соединен с n-м ин-г формационным входом регистра делимого (j+1)-rb вычислительного блока, 1-е разрядные выходы регистра делимо1- го n-го вычислительного блока соеди0

5

0

5

0

5

0

5

0

5

пени с первыми входами 1-х элементов 2И-1ШИ группы того же блока, группа прямых разрядных выходов блока сложения каждого вычислительного блока соединена с третьими входами элементов 2И-ИЛИ того же блока, выход первого мультиплексора каждого вычислительного блока соединен с четвертыми входами элементов 2И-ИЛИ группы того блока,выход первого мультилпексо- ра каждого вычислительного блока соединен с четвертыми входами элементов 2Н-ИЛИ группы того же блока, выход 1-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ группы соединен с i-м информационным входом регистра делителя первого вычислительного блока, группа выходов элементов 2И-НЛИ п-го вычислительного блока соединена с первой группой информационных входов мультиплексора, i-й выход которого соединен с (1-1)-м информационным входом регистра делимого первого вычислительного блока, вход сброса регистров дштимого, делителя и частного каждого вычислительного блока объединены и образуют одноименный вход устройства, управляющий вход мультиплексора, первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, а также управляющие входы блока сложения первого и второго мультиплексоров каждого вычислительного блока объединены и образуют вход режима устройства,вторая группа информационных входов мультиплексора образует группу входов кода делимого устройства, п-й информационный вход регистра делимо- мого и (п-1) первых информационных входов регистра частного первого вычислительного блока образуют группу входов контролируемых последовательностей уст- ройстиа, вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ образуют группу входов кода делителя устройства, группа выходов элемента 2И-ИЛИ n-го вычислительного блока образует группу выходов сигнатуры устройства, группа разрядных выходов регистра частного п-го вычислительного блока образует группу выходов кода частного устройства.

управляющий вход блока, информационные выходы п сумматоров образуют группу разрядных выходов блока, информационный выход первого сумматора соединен с входом элемента НЕ, выход которого образует первый инверсный разрядный выход блока, первые и вторые информационные входы сумматор

22 2 21.1

tk Ф 23.1

образуют соответственно первую и вторую группы информационных входов блока, входы переноса k-x сумматоров, где k 1,(п-1), соединены с выходами k-x элементов И, вторые входы которых соединены с выходами переноса (k+1)-x сумматоров.

-Z

f f f

Z3.2 фиг. г

f

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-01-15—Публикация

1988-05-23—Подача