Изобретение относится к вычисли- тельной технике и может быть использовано в устройствах памяти на цилиндрических магнитных доменах (ЦМД). Цель изобретения - упрощение и повышение надежности синхрогенератора

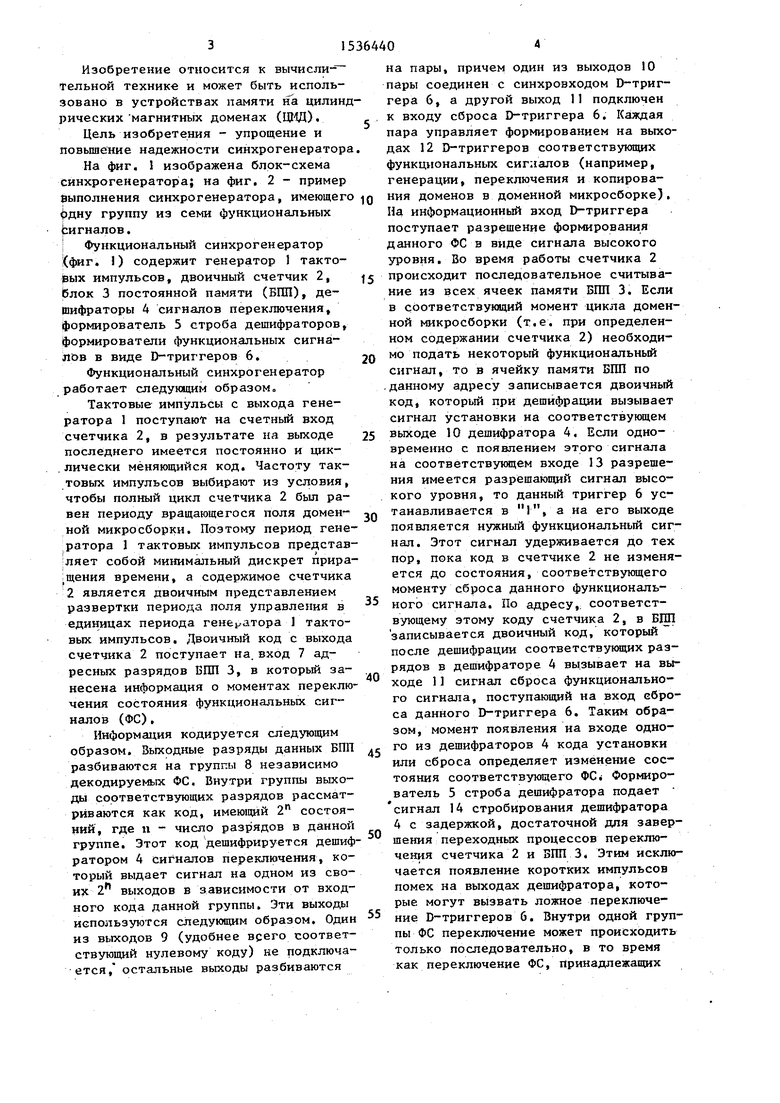

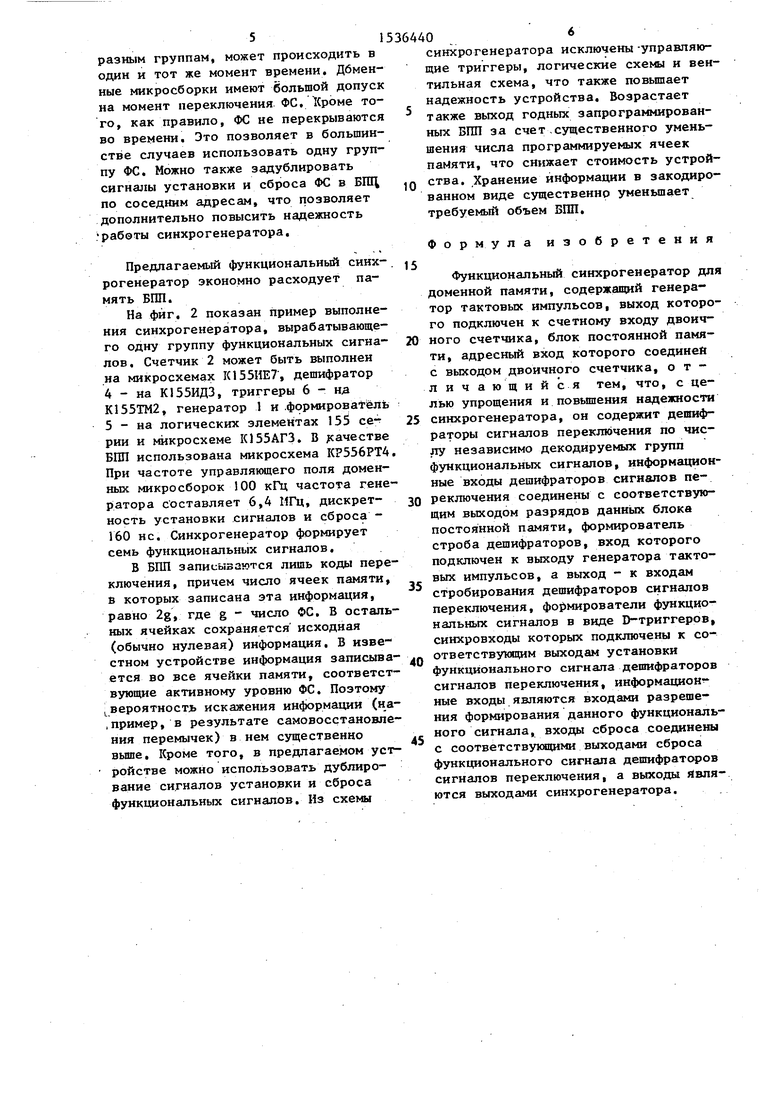

На фиг. 1 изображена блок-схема синхрогенератора; на фиг. 2 - пример выполнения синхрогенератора, имеющего одну группу из семи функциональных сигналов.

Функциональный синхрогенератор (фиг. 1) содержит генератор 1 тактовых импульсов, двоичный счетчик 2, блок 3 постоянной памяти (БПП), дешифраторы 4 сигналов переключения, формирователь 5 строба дешифраторов, формирователи функциональных сигналов в виде D-триггеров 6.

Функциональный синхрогенератор работает следующим образом.

Тактовые импульсы с выхода генератора 1 поступают на счетный вход счетчика 2, в результате на выходе последнего имеется постоянно и циклически меняющийся код. Частоту тактовых импульсов выбирают из условия, чтобы полный цикл счетчика 2 был равен периоду вращающегося поля доменной микросборки. Поэтому период генератора 1 тактовых импульсов представляет собой минимальный дискрет приращения времени, а содержимое счетчика 2 является двоичным представлением развертки периода поля управления в единицах периода генератора 1 тактовых импульсов. Двоичный код с выхода счетчика 2 поступает на. вход 7 адресных разрядов БПП 3, в который занесена информация о моментах переключения состояния функциональных сигналов (ФС) ,

Информация кодируется следующим образом. Выходные разряды данных БПП разбиваются на группы 8 независимо декодируемых ФС. Внутри группы выходы соответствующих разрядов рассматриваются как код, имеющий 2м состояний, где и - число разрядов в данной группе. Этот код дешифрируется дешифратором 4 сигналов переключения, который выдает сигнал на одном из своих выходов в зависимости от входного кода данной группы. Эти выходы используются следующим образом. Один из выходов 9 (удобнее всего соответствующий нулевому коду) не подключается, остальные выходы разбиваются

5

0

5

0

5

0

5

0

5

на пары, причем один из выходов 10 пары соединен с синхровходом D-триг- гера 6, а другой выход 11 подключен к входу сброса D-триггера 6. Каждая пара управляет формированием на выходах 12 D-триггеров соответствующих функциональных сигналов (например, генерации, переключения и копирования доменов в доменной микросборке), На информационный вход D-триггера поступает разрешение формирования данного ФС в виде сигнала высокого уровня. Во время работы счетчика 2 происходит последовательное считывание из всех ячеек памяти БПП 3. Если в соответствующий момент цикла доменной микросборки (т.е. при определенном содержании счетчика 2) необходимо подать некоторый функциональный сигнал, то в ячейку памяти БПП по данному адресу записывается двоичный код, который при дешифрации вызывает сигнал установки на соответствующем выходе 10 дешифратора 4. Если одновременно с появлением этого сигнала на соответствующем входе 13 разрешения имеется разрешающий сигнал высокого уровня, то данный триггер 6 устанавливается в 1, а на его выходе появляется нужный функциональный сигнал. Этот сигнал удерживается до тех пор, пока код в счетчике 2 не изменяется до состояния, соответствующего моменту сброса данного функционального сигнала. По адресу, соответствующему этому коду счетчика 2, в БПП записывается двоичный код, который после дешифрации соответствующих разрядов в дешифраторе 4 вызывает на выходе 11 сигнал сброса функционального сигнала, поступающий на вход сброса данного D-триггера 6. Таким образом, момент появления на входе одного из дешифраторов 4 кода установки или сброса определяет изменение состояния соответствующего ФС. Формирователь 5 строба дешифратора подает сигнал 14 стробирования дешифратора 4 с задержкой, достаточной для завершения переходных процессов переключения счетчика 2 и БПП 3. Этим исключается появление коротких импульсов помех на выходах дешифратора, которые могут вызвать ложное переключение D-триггеров 6. Внутри одной группы ФС переключение может происходить только последовательно, в то время как переключение ФС, принадлежащих

разным группам, может происходить в один и тот же момент времени. Дбмен- ные микросборки имеют большой допуск на момент переключения ФС. Кроме того, как правило, ФС не перекрываются во времени. Это позволяет в большинстве случаев использовать одну группу ФС. Можно также задублировать сигналы установки и сброса ФС в БПЦ по соседним адресам, что позволяет дополнительно повысить надежность работы синхрогенератора.

Предлагаемый функциональный синх- рогенератор экономно расходует память БПП.

На фиг. 2 показан пример выполнения синхрогенератора, вырабатывающего одну группу функциональных сигналов. Счетчик 2 может быть выполнен на микросхемах К155ИЕ7, дешифратор

4- на К155ИДЗ, триггеры 6 - нд К155ТМ2, генератор I и формирователь

5- на логических элементах 155 серии и микросхеме К155АГЗ. В качестве БПП использована микросхема КР556РТ4. При частоте управляющего поля доменных микросборок 100 кГц частота генератора составляет 6,4 НГц, дискретность установки сигналов и сброса - 160 не. Синхрогенератор формирует семь функциональных сигналов.

В БПП записываются лишь коды переключения, причем число ячеек памяти, которых записана эта информация, авно 2g, где g - число ФС. В остальных ячейках сохраняется исходная (обычно нулевая) информация. В известном устройстве информация записыватся во все ячейки памяти, соответствующие активному уровню ФС. Поэтому ероятность искажения информации (на- пример, в результате самовосстановлеия перемычек) в нем существенно выше. Кроме того, в предлагаемом устройстве можно использовать дублироание сигналов установки и сброса ункциональных сигналов. Из схемы

0

5

0

5

0

5

0

5

синхрогенератора исключены -управляющие триггеры, логические схемы и вентильная схема, что также повышает надежность устройства. Возрастает также выход годных запрограммированных БПП за счет существенного уменьшения числа программируемых ячеек памяти, что снижает стоимость устройства. Хранение информации в закодированном виде существенно уменьшает требуемый объем БПП.

Формула изобретения

Функциональный синхрогенератор для доменной памяти, содержащий генератор тактовых импульсов, выход которого подключен к счетному входу двоичного счетчика, блок постоянной памяти, адресный вход которого соединен с выходом двоичного счетчика, отличающийся тем, что, с целью упрощения и повышения надежности синхрогенератора, он содержит дешифраторы сигналов переключения по числу независимо декодируемых групп функциональных сигналов, информационные входы дешифраторов сигналов переключения соединены с соответствующим выходом разрядов данных блока постоянной памяти, формирователь строба дешифраторов, вход которого подключен к выходу генератора тактовых импульсов, а выход - к входам стробирования дешифраторов сигналов переключения, формирователи функциональных сигналов в виде D-триггеров, синхровходы которых подключены к соответствующим выходам установки функционального сигнала дешифраторов сигналов переключения, информационные входы являются входами разрешения формирования данного функционального сигнала, входы сброса соединены с соответствующими выходами сброса функционального сигнала дешифраторов сигналов переключения, а выходы являются выходами синхрогенератора.

ФС

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный синхрогенератор для доменной памяти | 1989 |

|

SU1619341A2 |

| Устройство управления для доменной памяти | 1982 |

|

SU1152035A1 |

| Видеоконтрольное устройство для дефектоскопии сварных соединений | 1985 |

|

SU1506476A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1984 |

|

SU1292029A1 |

| ЦИФРОВОЙ ГЕНЕРАТОР СИНУСОИДАЛЬНЫХ СИГНАЛОВ | 1991 |

|

RU2050688C1 |

| Оптическое устройство для вычисления корреляционной функции | 1988 |

|

SU1520541A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Устройство для формирования сигналов алфавитно-цифровых и графических изображений | 1982 |

|

SU1083406A1 |

| Устройство для контроля знаний обучаемых | 1987 |

|

SU1524082A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах памяти на цилиндрических магнитных доменах (ЦМД). Целью изобретения является упрощение и повышение надежности синхрогенератора. Синхрогенератор содержит генератор 1 тактовых импульсов, двоичный счетчик 2, блок 3 постоянной памяти, дешифраторы 4 сигналов переключения, формирователь 5 строба дешифраторов, формирователи функциональных сигналов в виде Д-триггеров 6. Функциональный синхрогенератор экономно расходует память блока постоянной памяти. 2 ил.

Фм.1

| Electronic Engineering, 1979, № 625, p | |||

| Машина для изготовления проволочных гвоздей | 1922 |

|

SU39A1 |

| Electronic Design, v | |||

| Прибор с двумя призмами | 1917 |

|

SU27A1 |

| Способ получения молочной кислоты | 1922 |

|

SU60A1 |

Авторы

Даты

1990-01-15—Публикация

1988-03-16—Подача