Изобретение относится к вычислительной технике и может быть использовано для параллельного суммирования многоразрядных двоичных чисел.

Цель изобретения - расширение функциональных возможностей за счет накопления результата.

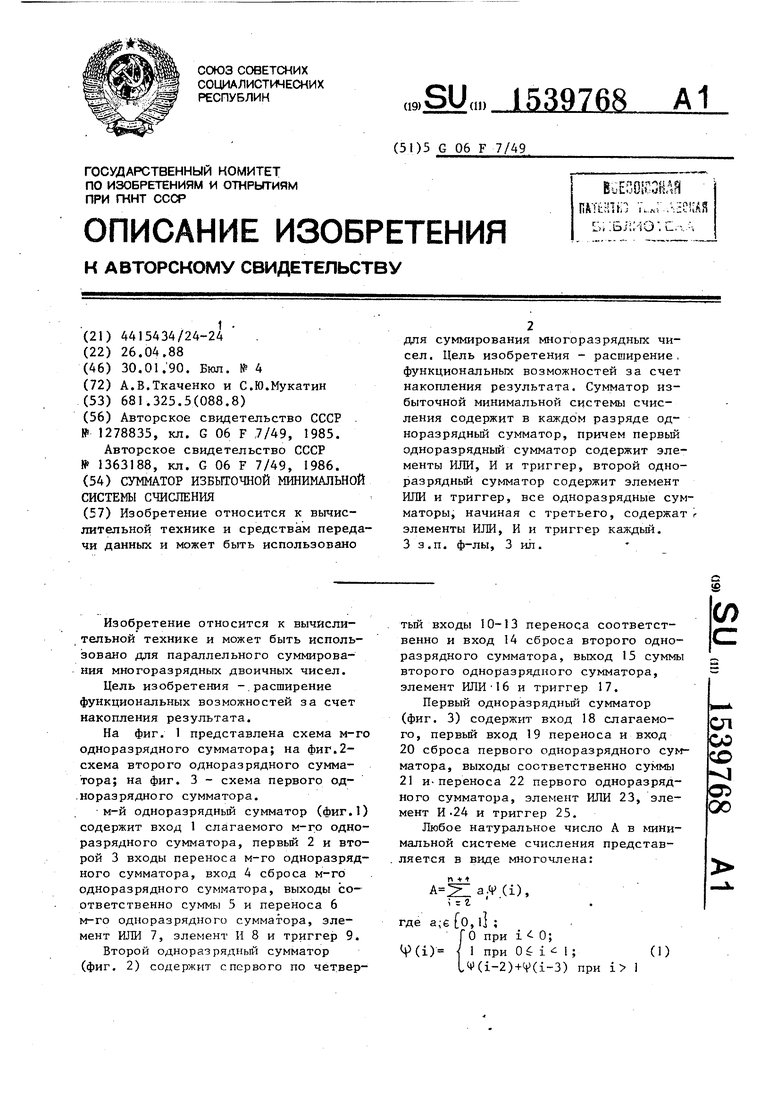

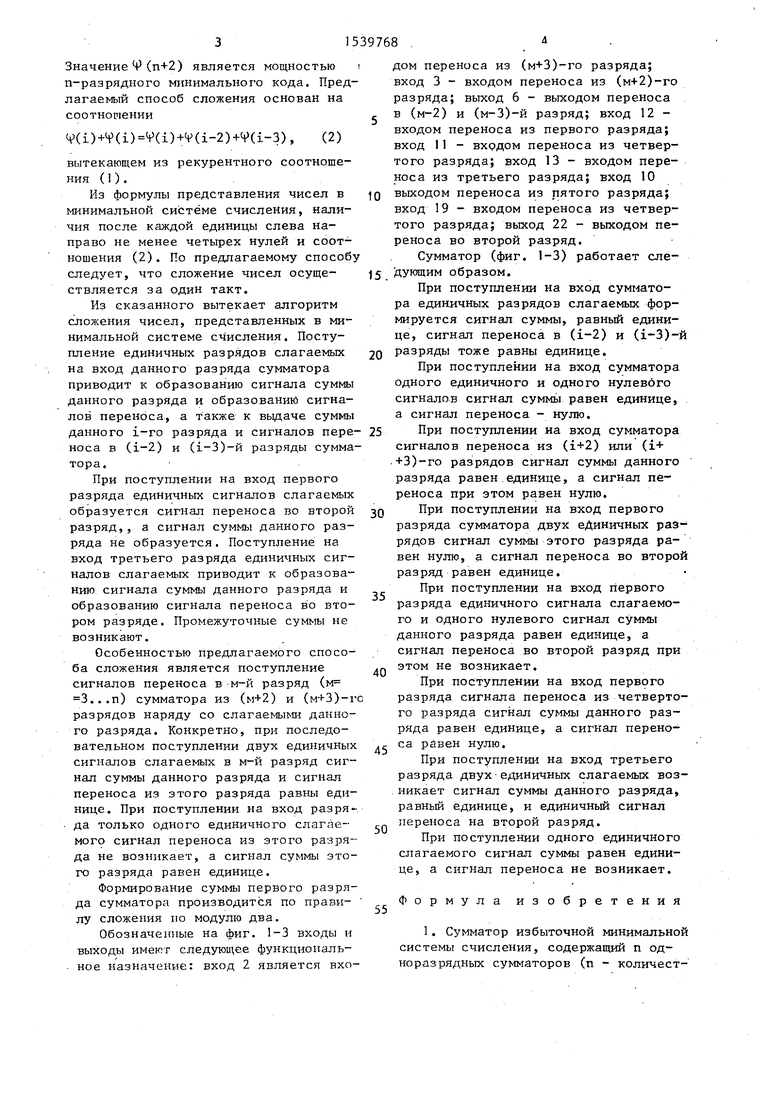

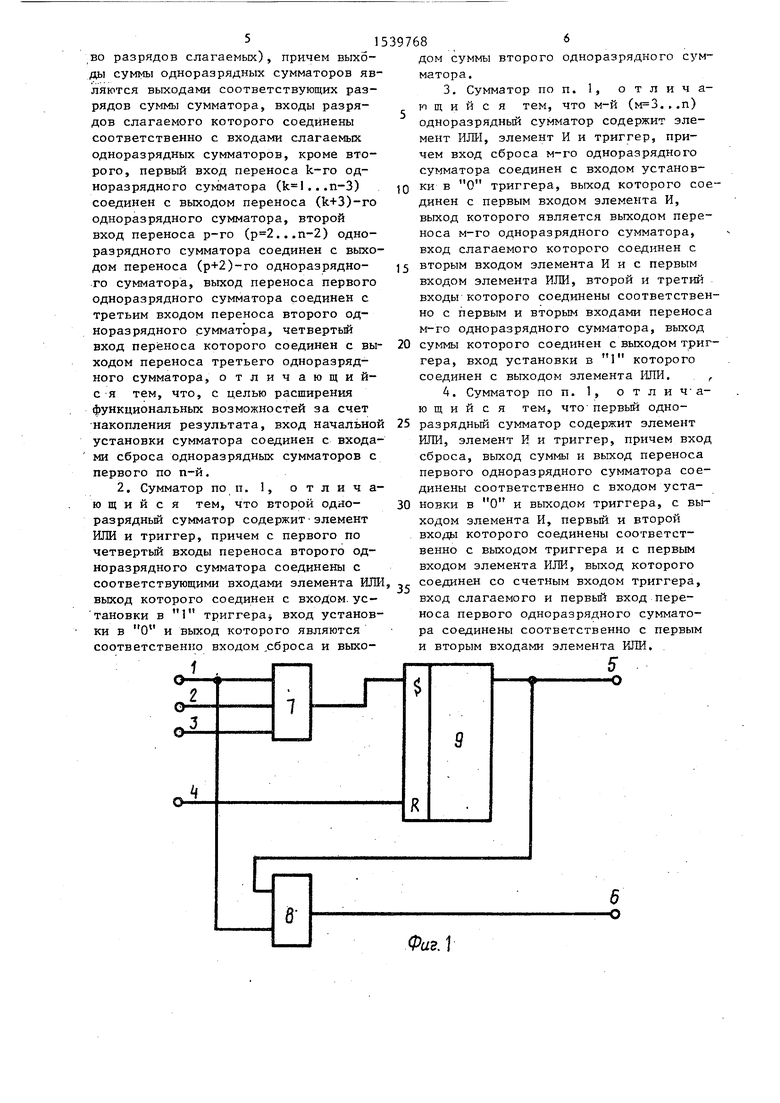

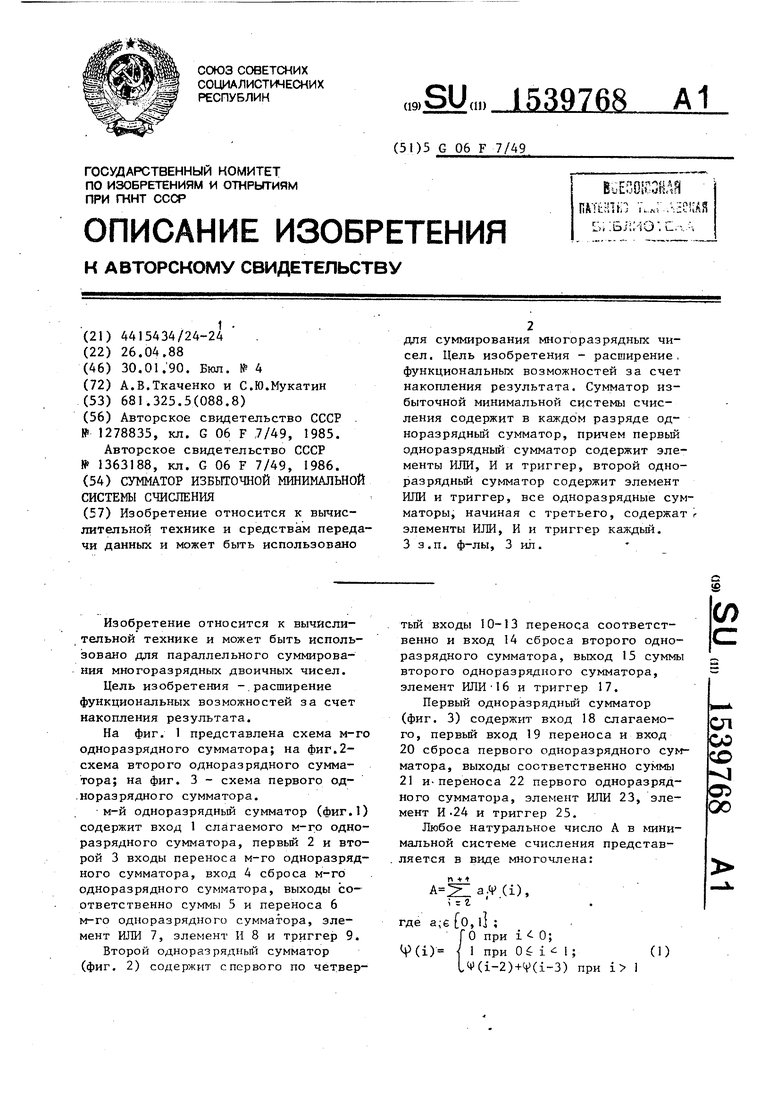

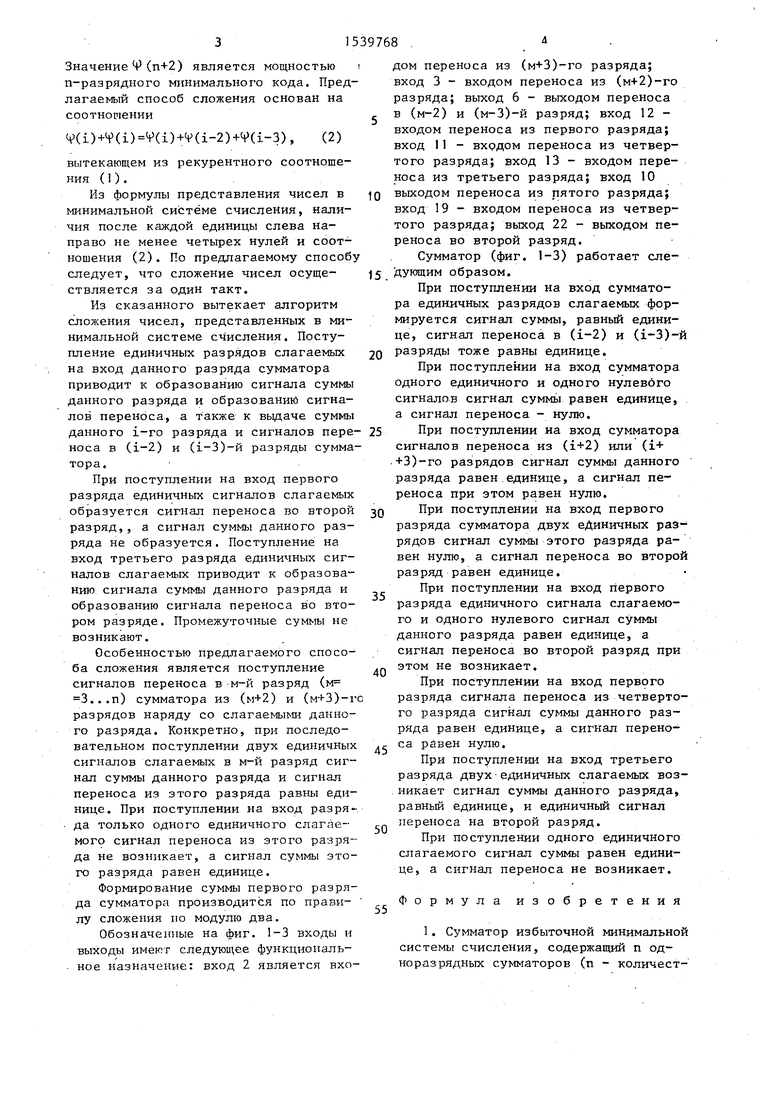

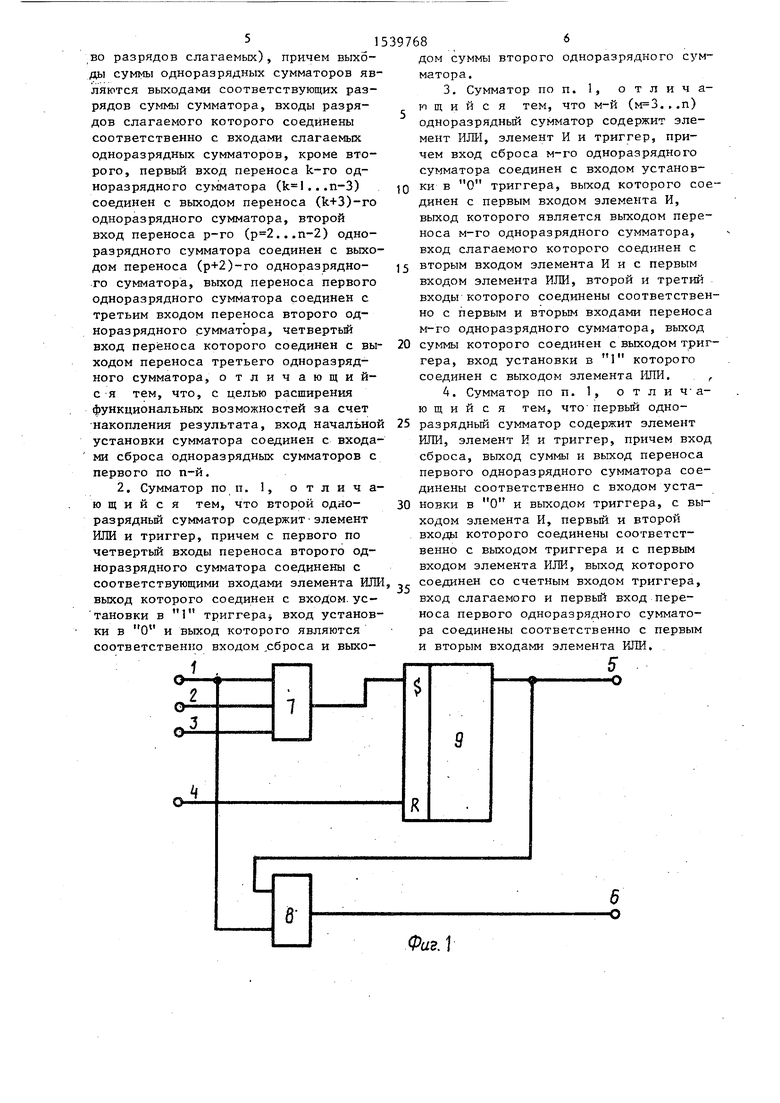

На фиг. 1 представлена схема м-го одноразрядного сумматора; на фиг.2- схема второго одноразрядного сумматора; на фиг. 3 - схема первого одноразрядного сумматора.

м-й одноразрядный сумматор (фиг.1) содержит вход 1 слагаемого м-го одноразрядного сумматора, первьй 2 и второй 3 входы переноса м-го одноразрядного сумматора, вход 4 сброса м-го одноразрядного сумматора, выходы соответственно суммы 5 и переноса 6 м-го одноразрядного сумматора, элемент ИЛИ 7, элемент И 8 и триггер 9.

Второй одноразрядный сумматор (фиг. 2) содержит с первого по четвертый входы 10-13 переноса соответственно и вход 14 сброса второго одноразрядного сумматора, выход 15 суммы второго одноразрядного сумматора, элемент ИЛИ 16 и триггер 17.

Первый одноразрядный сумматор (фиг. 3) содержит вход 18 слагаемого, первьй вход 19 переноса и вход

20сброса первого одноразрядного сумматора, выходы соответственно суммы

21и-переноса 22 первого одноразрядного сумматора, элемент ИЛИ 23, элемент И-24 и триггер 25.

Любое натуральное число А в минимальной системе счисления представляется в виде многочлена:

п А а.УЩ.

; г

где а,6 о, 1 ;

ГО при i 0; Ф(1) | 1 при 0& If- I;(1)

(,Ф(1-2)+Ч(г-3) при i 1

(Л

СП

СО СО

-vj

сэ

00

ЗначениеФ(п+2) является мощностью n-разрядного минимального кода. Предлагаемый способ сложения основан на соотношении

4(i)+4(i)V(i)+Y(i-2)+V(i-3), (2)

вытекающем из рекурентиого соотношения (1 ) .

Из формулы представления чисел в минимальной системе счисления, наличия после каждой единицы слева направо не менее четырех нулей и соотношения (2). По предлагаемому способу следует, что сложение чисел осуще- ствляется за один такт.

Из сказанного вытекает алгоритм сложения чисел, представленных в минимальной системе счисления. Поступление единичных разрядов слагаемых на вход данного разряда сумматора приводит к образованию сигнала суммы данного разряда и образованию сигналов переноса, а также к выдаче суммы данного 1-го разряда и сигналов пере- носа в (i-2) и (1-3)-й разряды сумматора.

При поступлении на вход первого разряда единичных сигналов слагаемых образуется сигнал переноса во второй разряд,, а сигнал суммы данного разряда не образуется. Поступление на вход третьего разряда единичных сигналов слагаемых приводит к образованию сигнала суммы данного разряда и образованию сигнала переноса во втором разряде. Промежуточные суммы не возникают.

Особенностью предлагаемого способа сложения является поступление сигналов переноса в м-й разряд (м 3...п) сумматора из (м+2) и (м+3)-г разрядов наряду со слагаемыми данного разряда. Конкретно, при последовательном поступлении двух единичных сигналов слагаемых в м-й разряд сигнал суммы данного разряда и сигнал переноса из этого разряда равны единице. При поступлении на вход разряда только одного единичного слагае- мого сигнал переноса из этого разряда не возникает, а сигнал суммы этого разряда равен единице.

Формирование суммы первого разряда сумматора производится по правилу сложения по модулю два.

Обозначенные на фиг. 1-3 входы и выходы имеют следующее функциональное назначение: вход 2 является вхо

.

0 5

0

Q Q

5

5

дом переноса из (м+3)-го разряда; вход 3 - входом переноса из (м+2)-го разряда; выход 6 - выходом переноса в (м-2) и (м-З)-й разряд; вход 12 - входом переноса из первого разряда; вход I1 - вхрдом переноса из четвертого разряда; вход 13 - входом переноса из третьего разряда; вход 10 выходом переноса из пятого разряда; вход 19 - входом переноса из четвертого разряда; выход 22 - выходом переноса во второй разряд.

Сумматор (фиг. 1-3) работает следующим образом.

При поступлении на вход сумматора единичных разрядов слагаемых формируется сигнал суммы, равный единице, сигнал переноса в (i-2) и (1-3)-й разряды тоже равны единице.

При поступлении на вход сумматора одного единичного и одного нулевого сигналов сигнал суммы равен единице, а сигнал переноса - нулю.

При поступлении на вход сумматора сигналов переноса из (i+2) или (i+ +3)-го разрядов сигнал суммы данного разряда равен единице, а сигнал переноса при этом равен нулю.

При поступлении на вход первого разряда сумматора двух единичных разрядов сигнал суммы этого разряда равен нулю, а сигнал переноса во второй разряд равен единице.

При поступлении на вход первого разряда единичного сигнала слагаемого и одного нулевого сигнал суммы данного разряда равен единице, а сигнал переноса во второй разряд при этом не возникает.

При поступлении на вход первого разряда сигнала переноса из четвертого разряда сигнал суммы данного разряда равен единице, а сигнал переноса равен нулю.

При поступлении на вход третьего разряда двух единичных слагаемых возникает сигнал суммы данного разряда, равный единице, и единичный сигнал переноса на второй разряд.

При поступлении одного единичного слагаемого сигнал суммы равен единице, а сигнал переноса не возникает.

Формула изобретения

1. Сумматор избыточной минимальной системы счисления, содержащий п одноразрядных сумматоров (п - количест51539768

во разрядов слагаемых), причем выходы суммы одноразрядных сумматоров являются выходами соответствующих разрядов суммы сумматора, входы разрядов слагаемого которого соединены соответственно с входами слагаемых одноразрядных сумматоров, кроме второго, первый вход переноса k-ro одноразрядного сумматора (...n-3) соединен с выходом переноса (k+3)-ro одноразрядного сумматора, второй вход переноса р-го (...п-2) одноразрядного сумматора соединен с выходом переноса (р+2)-го одноразрядного сумматора, выход переноса первого одноразрядного сумматора соединен с третьим входом переноса второго одноразрядного сумматора, четвертый

6

дом суммы второго одноразрядного сумматора.

3. Сумматор по п. 1, отличающийся тем, что м-й (...п) одноразрядный сумматор содержит элемент ИЛИ, элемент И и триггер, причем вход сброса м-го одноразрядного сумматора соединен с входом установки в О триггера, выход которого соединен с первым входом элемента И, выход которого является выходом переноса м-го одноразрядного сумматора, вход слагаемого которого соединен с j 5 вторым входом элемента И и с первым входом элемента ИЛИ, второй и третий входы которого соединены соответственно с первым и вторым входами переноса м-го одноразрядного сумматора, выход

10

вход переноса которого соединен с вы- 20 суммы которого соединен с выходом триггера, вход установки в 1 которого соединен с выходом элемента ИЛИ. , 4. Сумматор по п. 1, отличающийся тем, что первый одноходом переноса третьего одноразрядного сумматора, отличающи й- с я тем, что, с целью расширения функциональных возможностей за счет

гера, вход установки в 1 которого соединен с выходом элемента ИЛИ. , 4. Сумматор по п. 1, отличающийся тем, что первый однонакопления результата, вход начальной 25 разрядный сумматор содержит элемент установки сумматора соединен с входа- ИЛИ, элемент И и триггер, причем вход ми сброса одноразрядных сумматоров с сброса, выход суммы и выход переноса

первого одноразрядного сумматора соединены соответственно с входом уста- 30 новки в О

первого по п-и.

2. Сумматор по п. 1, отличающийся тем, что второй одноразрядный сумматор содержит элемент ИЛИ и триггер, причем с первого по четвертьй входы переноса второго одноразрядного сумматора соединены с

и выходом триггера, с выходом элемента И, первый и второй входы которого соединены соответственно с выходом триггера и с первым входом элемента ИЛИ, выход которого соответствующими входами элемента ИЛИ, ,- соединен со счетным входом триггера, выход которого соединен с входом ус- вход слагаемого и первый вход переноса первого одноразрядного сумматора соединены соответственно с первым и вторым входами элемента ИЛИ.

тановки в 1 триггера, вход установки в О и выход которого являются соответственно входом сброса и выхо

6

дом суммы второго одноразрядного сумматора.

3. Сумматор по п. 1, отличающийся тем, что м-й (...п) одноразрядный сумматор содержит элемент ИЛИ, элемент И и триггер, причем вход сброса м-го одноразрядного сумматора соединен с входом установки в О триггера, выход которого соединен с первым входом элемента И, выход которого является выходом переноса м-го одноразрядного сумматора, вход слагаемого которого соединен с 5 вторым входом элемента И и с первым входом элемента ИЛИ, второй и третий входы которого соединены соответственно с первым и вторым входами переноса м-го одноразрядного сумматора, выход

суммы которого соединен с выходом триггера, вход установки в 1 которого соединен с выходом элемента ИЛИ. , 4. Сумматор по п. 1, отличающийся тем, что первый одноФаг. I

| название | год | авторы | номер документа |

|---|---|---|---|

| НАКАПЛИВАЮЩИЙ СУММАТОР | 1993 |

|

RU2043650C1 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| Сумматор кодов фибоначчи | 1976 |

|

SU732864A1 |

| Накапливающий сумматор | 1976 |

|

SU577528A1 |

| Накапливающий сумматор | 1988 |

|

SU1532916A1 |

| Накапливающий сумматор | 1985 |

|

SU1319023A1 |

| Накапливающий сумматор | 1985 |

|

SU1278835A1 |

| Последовательный сумматор | 1983 |

|

SU1149248A1 |

| Накапливающий сумматор | 1991 |

|

SU1800454A1 |

| Параллельный сумматор | 1986 |

|

SU1363188A1 |

Изобретение относится к вычислительной технике и средствам передачи данных и может быть использовано для суммирования многоразрядных чисел. Цель изобретения - расширение функциональных возможностей за счет накопления результата. Сумматор избыточной минимальной системы счисления содержит в каждом разряде одноразрядный сумматор, причем первый одноразрядный сумматор содержит элементы ИЛИ, И и триггер, второй одноразрядный сумматор содержит элемент ИЛИ и триггер, все одноразрядные сумматоры, начиная с третьего, содержат элементы ИЛИ, И и триггер каждый. 3 з.п.ф-лы, 3 ил.

18 о-i

19

23

24

г

-о

&

25

22

ю

Фае.З

| Накапливающий сумматор | 1985 |

|

SU1278835A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Параллельный сумматор | 1986 |

|

SU1363188A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-01-30—Публикация

1988-04-26—Подача