состоит из элементов ИЛИ и И. Основной алгоритм сложения значащих цифр в однотактном сумматоре задан соотношением (j;(S) + ((S). V(S) +(f(S-2) + Ct(S-3), гдеу(5) - -веса двоичных разрядов минимальной системы счис1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в специализированных вычислительных машинах для параллельного суммирования многоразрядных двоичных чисел.

Цель изобретения - упрощение устройства и увеличение быстродействия.

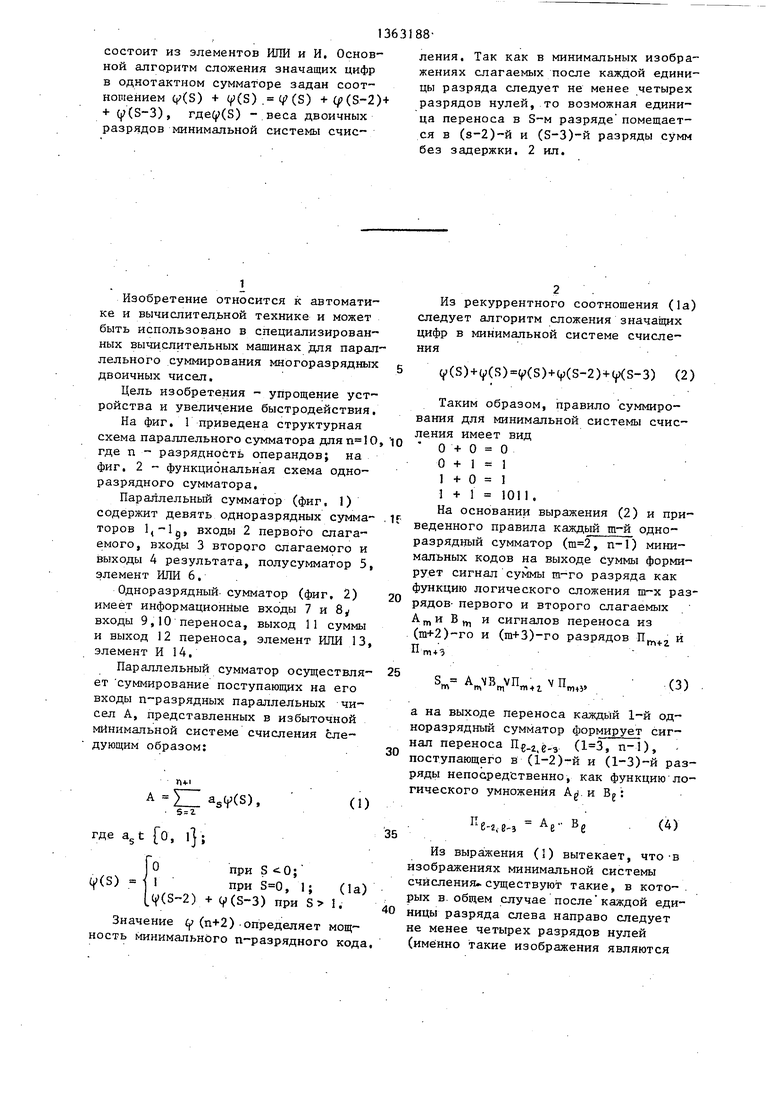

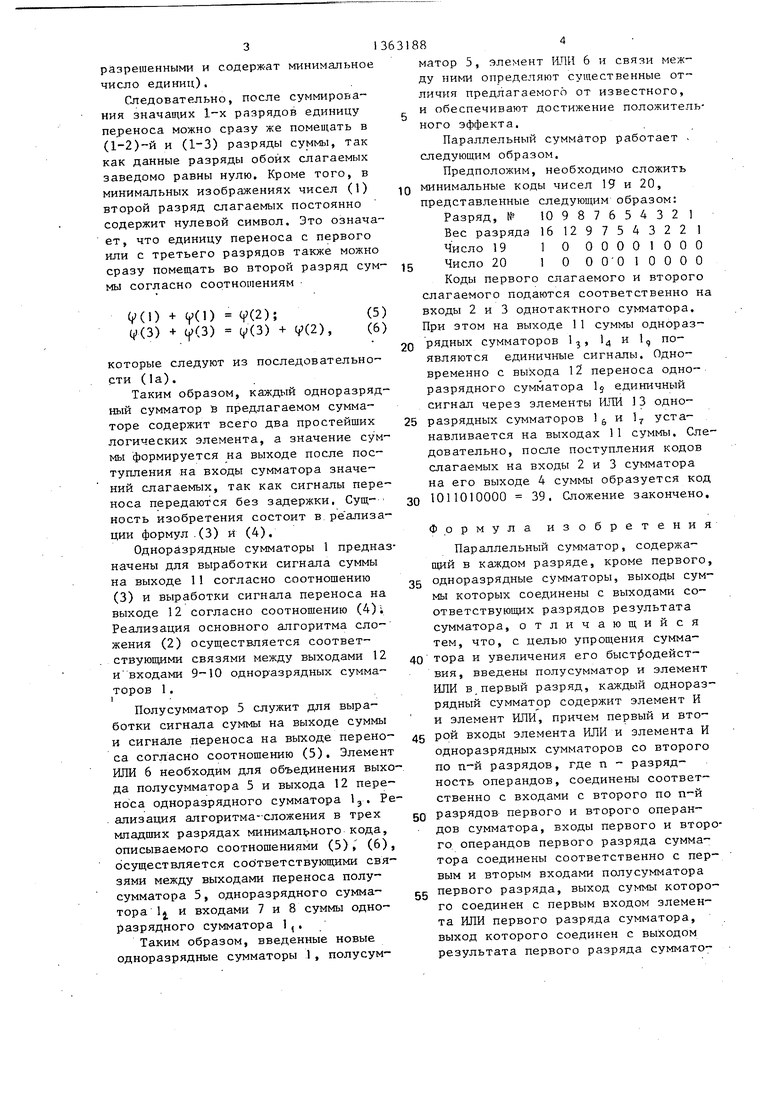

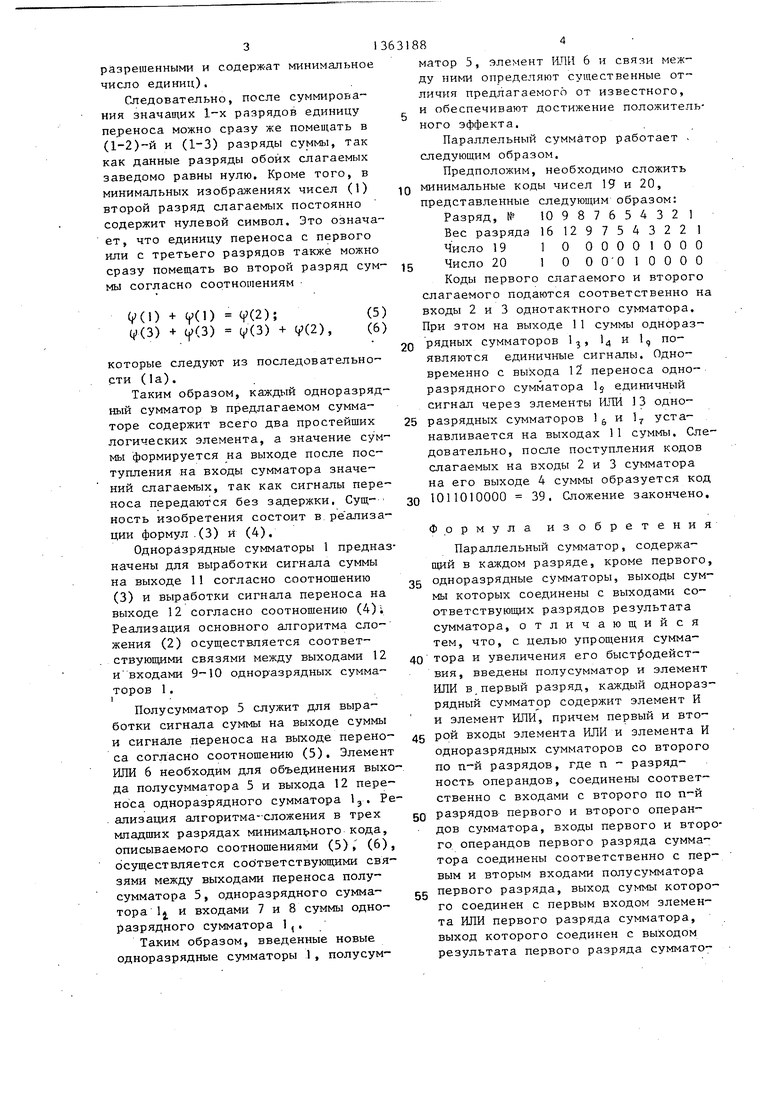

На фиг. Г приведена структурная схема параллельного сумматора где п - разрядность операндов; на фиг. 2 - функциональная схема одноразрядного сумматора.

Параллельный сумматор (фиг. 1) содержит девять одноразрядных сумматоров 1(-1й, входы 2 первого слагаемого, входы 3 второго слагаемрго и выходы 4 результата, полусумматор 5, элемент ИЛИ 6.

Одноразрядный- сумматор (фиг. 2) имеет информационные входы 7 и 8у входы 9,10 переноса, выход 11 суммы и выход 12 переноса, элемент 1ШИ 13, элемент И 14.

Параллельный сумматор осуществляет суммирование поступающих на его входы п-разрядных параллельных чисел А, представленных в избыточной минимальной системе счисления следующим образом:

А

). (1)

где о, ij;

(+ (S)

при S О;

при , 1; (1а)

((S-2) + V(S-3) при S 1.

Значение (п+2).определяет мощность минимального п-разрядного кода.

ления. Так как в минимальных изображениях слагаемых после каждой единицы разряда следует не менее четырех разрядов нулей, то возможная единица переноса в S-м разряде помещается в (з-2)-й и (5-3)-й разряды сумм без задержки. 2 ил.

f

0

Из рекуррентного соотнощения (1а) следует алгоритм сложения значащих цифр в минимальной системе счисления.

y(S) + ((S)9(S)+v(S-2)+V(S-3) (2)

Таким образом, правило суммирования для минимальной системы счисления имеет вид

О О О

0+1 1 1 + 1 1011.

На основании выражения (2) и приведенного правила каждый ш-й одноразрядный сумматор (, п-1) минимальных кодов на выходе суммы формирует сигнал суммы т-го разряда как функцию логического сложения т-х разрядов- первого и второго слагаемых В и сигналов переноса из (т+2)-го и (т+3)-го разрядов П Пт+э

т 2

25

V .

(3)

а на выходе переноса казвдый 1-й одноразрядный сумматор формирует сигнал переноса Il.g,,. (, п-1), поступающего в (1-2)-й и (1-3)-й разряды непосредственно, как функцию логического умножения А. и

б-г.В З

В

е

(4)

Из выражения (1) вытекает, что-в изображениях минимальной системы счисления существуют такие, в которых в. общем случае после каждой единицы разряда слева направо следует не менее четырех разрядов нулей (именно такие изображения являются

разрешенными и содержат минимальное число единиц).

Следовательно, после суммирования значащих 1-х разрядов единицу переноса можно сразу же помещать в (1-2)-и и (1-3) разряды суммы, так как данные разряды обоих слагаемых заведомо равны нулю. Кроме того, в минимальных изображениях чисел (1) второй разряд слагаемых постоянно содержит нулевой символ. Это означает, что единицу переноса с первого или с третьего разрядов также можно сразу помещать во второй разряд суммы согласно соотношениям

V(o «- yd) (,

Q)(3) + t,(3) с,;(3) +

V(2),

которые следуют из последовательности (1а).

Таким образом, каждый одноразрядный сумматор в предлагаемом сумматоре содержит всего два простейших логических элемента, а значение суммы формируется на выходе после поступления на входы сумматора значений слагаемых, так как сигналы переноса передаются без задержки. Сущ- ность изобретения состоит в реализации формул.(3) и (4),

Одноразрядные сумматоры 1 предназначены для выработки сигнала суммы на выходе 11 согласно соотношению (3) и выработки сигнала переноса на выходе 12 согласно соотношению (4); Реализация основного алгоритма сложения (2) осуществляется соответствующими связями между выходами 12 и входами 9-10 однор азрядных сумматоров 1.

Полусумматор 5 служит для выработки сигнала суммы на выходе суммы сигнале переноса на выходе переноса согласно соотношению (5). Элемент ИЛИ 6 необходим для объединения выхоа полусумматора 5 и выхода 12 переноса одноразрядного сумматора Ц. Ре- ализация алгоритма-сложения в трех младших разрядах минимал ного кода, описываемого соотношениями (5), (6), осуществляется соответствующими связями между выходами переноса полусумматора 5, одноразрядного сумматора и входами 7 и 8 суммы одноразрядного сумматора 1,.

Таким образом, введенные новые одноразрядные сумматоры 1, полусум63188

матор 5, элемент ИЛИ 6 и связи между ними определяют существенные отличия предлагаемого от известного, и обеспечивают достиже ше положительного эффекта.

Параллельный сумматор работает - следующим образом.

Предположим, необходимо сложить 10 минимальные коды чисел 19 и 20, представленные следующим образом:

Разряд, № Вес разряда Число 19 Число 20

1098765432 1

1612 97543221

1О 00001000

1О О О О 10000

20

25

Коды первого слагаемого и второго слагаемого подаются соответственно на входы 2 и 3 однотактного сумматора. При этом на выходе 1 суммы одноразрядных сумматоров Ц, 1 и 1, появляются единичные сигналы. Одновременно с выхода 12 переноса одноразрядного сумматора Ij единичный сигнал через элементы ИЛИ 13 одноразрядных сумматоров 15 и 1 устанавливается на выходах 11 суммы. Следовательно, после поступления кодов слагаемых на входы 2 и 3 сумматора на его выходе 4 суммы образуется код 1011010000 39. Сложение закончено.

30

Формула изобретения

Параллельный сумматор, содержащий в каждом разряде, кроме первого,

одноразрядные сумматоры, выходы суммы которых соединены с выходами соответствующих разрядов результата сумматора, отличающийся тем, что, с целью упрощения сумматора и увеличения его быстродействия, введены полусумматор и элемент ИЛИ в первый разряд, каждый одноразрядный сумматор содержит элемент И и элемент ИЛИ, причем первый и второй входы элемента ИЛИ и элемента И одноразрядных сумматоров со второго по п-й разрядов, где п - разрядность операндов, соединены соответственно с входами с второго по п-й

разрядов первого и второго операндов сумматора, входы первого и второго операндов первого разряда сумматора соединены соответственно с первым и вторым входами полусумматора

первого разряда, выход суммы которого соединен с первым входом элемента ИЛИ первого разряда сумматора, выход которого соединен с выходом результата первого разряда суммато 13631

pa, выход элемента ШШ одноразрядно го сумматора данного разряда соединен с выходом суммы данного одноразрядного сумматора, выход элемента И одноразрядного сумматора данного разряда соединен с выходом переноса одноразрядного сумматора данного разряда, выход переноса полусумматора первого, разряда соединен с первыми IQ входами элемента И и элемента ИЛИ одноразрядного сумматора первого раз- ряда, вторые входы элемента И и элеРедактор А, Долинич

Составитель М, Есенина

Техред Л.Олейник Корректор М. Пожо

Заказ 6362/39 Тираж 671Подписное

ВНИИИИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

88б

мента ИЛИ одноразрядного сумматора первого разряда соединены с выходом переноса одноразрядного сумматора второго разряда, выход переноса 1-г одноразрядного сумматора .(, п-.1) соединен с третьим и четвертым входами элемента ИЛИ соответственно (1-2)-го и (1-3)-го одноразрядных сумматоров, выход переноса однораз рядного сумматора третьего разряда соединен с вторым входом элемента МИ первого разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор избыточного кода | 1987 |

|

SU1476460A1 |

| Устройство для параллельного алгебраического сложения в знакоразрядной системе счисления | 1981 |

|

SU1003074A1 |

| Комбинационный сумматор | 1985 |

|

SU1310808A1 |

| Сумматор последовательного действия | 1989 |

|

SU1689945A2 |

| КОМБИНАЦИОННЫЙ СУММАТОР СТРУКТУРНЫХ КОДОВ | 1991 |

|

RU2023288C1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Сумматор кодов фибоначчи | 1976 |

|

SU732864A1 |

| Комбинационный сумматор | 1987 |

|

SU1442988A1 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| СУММАТОР ПО МОДУЛЮ СЕМЬ | 1992 |

|

RU2018924C1 |

Изобретение предназначено для построения высоконадежных сверхбыстродействующих специализированных микропродессов. Цель изобретения - упрощение устройства и увеличение быстродействия. Однотактный сумматор содержит одноразрядные сумматоры 1, полусумматор 5,элемент ИЛИ 6, а каждый одноразрядный сумматор 1 П IH (Л со а СлЭ 00 00

| Папернов А | |||

| А | |||

| Логические основы ЦВТ, М.; Советское радио, 1972, с | |||

| Канатное устройство для подъема и перемещения сыпучих и раздробленных тел | 1923 |

|

SU155A1 |

| П | |||

| Комбинационный сумматор | 1975 |

|

SU570896A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1987-12-30—Публикация

1986-05-21—Подача