Изобретение относится к вычислительной технике.

Цель изобретения - повышение достоверности фиксации неустойчивых сбоев,

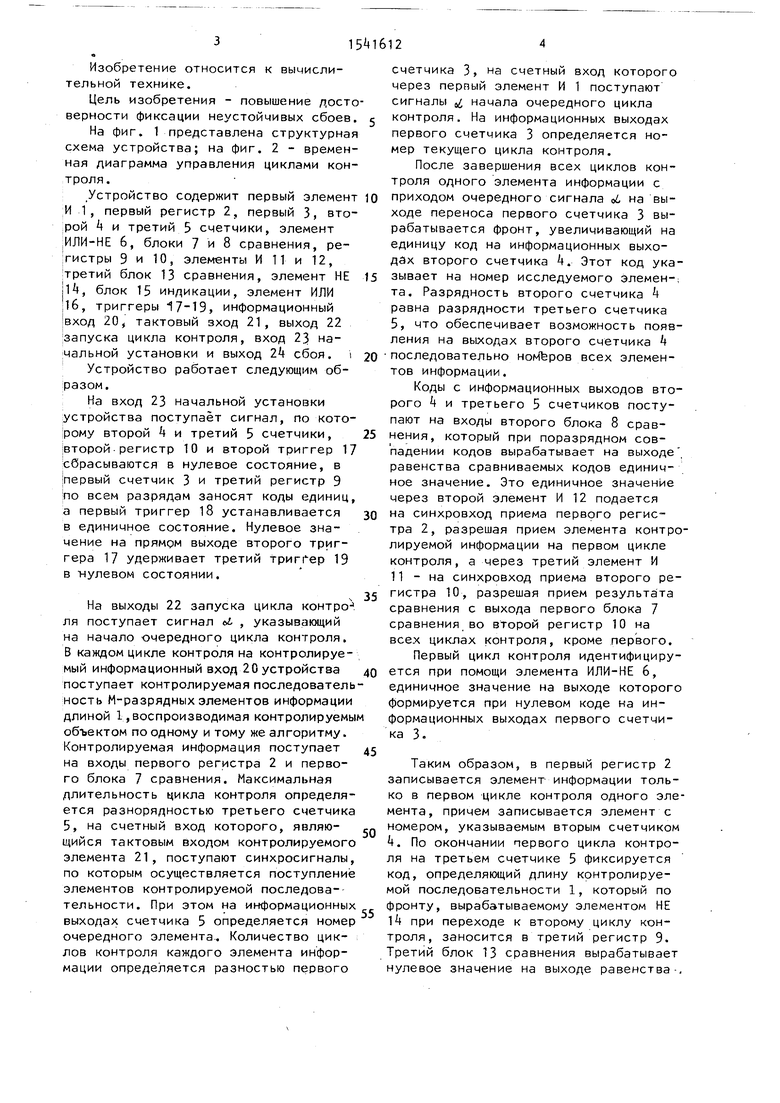

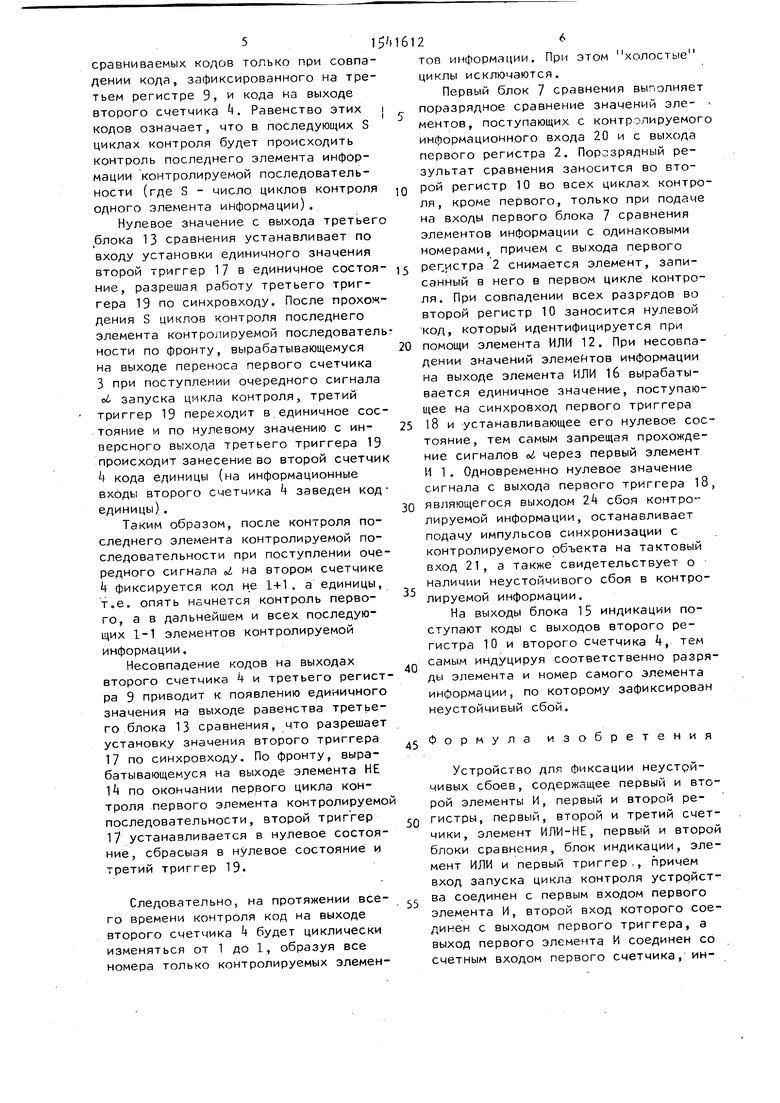

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - временная диаграмма управления циклами контроля.

.Устройство содержит первый элемент И 1, первый регистр 2, первый 3, второй 4 и третий 5 счетчики, элемент ИЛИ-НЕ 6, блоки 7 и 8 сравнения, регистры 9 и 10, элементы И 11 и 12, третий блок 13 сравнения, элемент НЕ ЛЬ, блок 15 индикации, элемент ИЛИ 16, триггеры 17-19, информационный вход 20, тактовый вход 21, выход 22 запуска цикла контроля, вход 23 начальной установки и выход 24 сбоя, i

Устройство работает следующим образом.

На вход 23 начальной установки устройства поступает сигнал, по которому второй 4 и третий 5 счетчики, второй регистр 10 и второй триггер 17 сбрасываются в нулевое состояние, в первый счетчик 3 и третий регистр 9 по всем разрядам заносят коды единиц, а первый триггер 18 устанавливается в единичное состояние. Нулевое значение на прямом выходе второго триггера 17 удерживает третий триггер 19 в нулевом состоянии.

На выходы 22 запуска цикла контро-1 ля поступает сигнал oi , указывающий на начало очередного цикла контроля. В каждом цикле контроля на контролируемый информационный вход 20 устройства поступает контролируемая последовательность М-разрядных элементов информации длиной воспроизводимая контролируемы объектом по одному и тому же алгоритму. Контролируемая информация поступает на входы первого регистра 2 и первого блока 7 сравнения. Максимальная длительность цикла контроля определяется разнорядностью третьего счетчика 5, на счетный вход которого, являю- щийся тактовым входом контролируемого элемента 21, поступают синхросигналы, по которым осуществляется поступление элементов контролируемой последовательности. При этом на информационных выходах счетчика 5 определяется номер очередного элемента. Количество циклов контроля каждого элемента информации определяется разностью первого

счетчика 3, на счетный вход которого через перпый элемент И 1 поступают сигналы начала очередного цикла контроля. На информационных выходах первого счетчика 3 определяется номер текущего цикла контроля.

После завершения всех циклов контроля одного элемента информации с приходом очередного сигнала об на выходе переноса первого счетчика 3 вырабатывается фронт, увеличивающий на единицу код на информационных выходах второго счетчика 4. Этот код указывает на номер исследуемого элемента. Разрядность второго счетчика 4 равна разрядности третьего счетчика 5, что обеспечивает возможность появления на выходах второго счетчика 4 последовательно номеров всех элементов информации.

Коды с информационных выходов второго 4 и третьего 5 счетчиков поступают на входы второго блока 8 сравнения, который при поразрядном совпадении кодов вырабатывает на выходе равенства сравниваемых кодов единичное значение. Это единичное значение через второй элемент И 12 подается на синхровход приема первого регистра 2, разрешая прием элемента контролируемой информации на первом цикле контроля, а через третий элемент И 11 - на синхровход приема второго регистра 10, разрешая прием результата сравнения с выхода первого блока 7 сравнения во второй регистр 10 на всех циклах контроля, кроме первого.

Первый цикл контроля идентифицируется при помощи элемента ИЛИ-НЕ 6, единичное значение на выходе которого формируется при нулевом коде на информационных выходах первого счетчика 3.

Таким образом, в первый регистр 2 записывается элемент информации только в первом цикле контроля одного элемента, причем записывается элемент с номером, указываемым вторым счетчиком 4. По окончании первого цикла контроля на третьем счетчике 5 фиксируется код, определяющий длину контролируемой последовательности I, который по фронту, вырабатываемому элементом НЕ 14 при переходе к второму циклу контроля, заносится в третий регистр 9. Третий блок 13 сравнения вырабатывает нулевое значение на выходе равенства

5 15

сравниваемых кодов только при совпадении кода, зафиксированного на третьем регистре 9, и кода на выходе второго счетчика А. Равенство этих кодов означает, что в последующих S циклах контроля будет происходить контроль последнего элемента информации контролируемой последовательности (где S - ЧИСЛО ЦИКЛОВ КОНТРОЛЯ

одного элемента информации).

Нулевое значение с выхода третьего блока 13 сравнения устанавливает по входу установки единичного значения второй триггер 17 в единичное состоя- ние, разрешая работу третьего триггера 19 по синхровходу. После прохождения S циклов контроля последнего элемента контролируемой последовательности по фронту, вырабатывающемуся на выходе переноса первого счетчика 3 при поступлении очередного сигнала оЈ запуска цикла контроля, третий триггер 19 переходит в единичное состояние и по нулевому значению с ин- версного выхода третьего триггера 19 происходит занесение во второй счетчик кода единицы (на информационные входы второго счетчика t заведен код- единицы).

Таким образом, после контроля последнего элемента контролируемой последовательности при поступлении очередного сигнала i на втором счетчике k фиксируется код не 1+1, а единицы, т„е. опять начнется контроль первого, а в дальнейшем и всех последующих 1-1 элементов контролируемой информации.

Несовпадение кодов на выходах второго счетчика 4 и третьего регистра 9 приводит к появлению единичного значения на выходе равенства третьего блока 13 сравнения, что разрешает установку значения второго триггера 17 по синхровходу. По фронту, вырабатывающемуся на выходе элемента НЕ 14 по окончании первого цикла контроля первого элемента контролируемой последовательности, второй триггер 1 устанавливается в нулевое состояние, сбрасыая в нулевое состояние и третий триггер 19.

Следовательно, на протяжении всего времени контроля код на выходе второго счетчика k будет циклически изменяться от 1 до 1, образуя все номера только контролируемых элемен

J JQ

20 25 30

35

40

5

5

126

тов информации. При этом холостые циклы исключаются.

Первый блок 7 сравнения выполняет поразрядное сравнение значений зле- ментов, поступающих с контролируемого информационного входа 20 и с выхода первого регистра 2. Поразрядный результат сравнения заносится во второй регистр 10 во всех циклах контроля, кроме первого, только при подаче на входы первого блока 7 сравнения элементов информации с одинаковыми номерами, причем с выхода первого регистра 2 снимается элемент, записанный в него в первом цикле контроля. При совпадении всех разрядов во второй регистр 10 заносится нулевой код, который идентифицируется при помощи элемента ИЛИ 12. При несовпадении значений элементов информации на выходе элемента ИЛИ 16 вырабатывается единичное значение, поступающее на синхровход первого триггера 18 и устанавливающее его нулевое состояние, тем самым запрещая прохождение сигналов oi через первый элемент И 1. Одновременно нулевое значение сигнала с выхода первого триггера 18, являющегося выходом 2А сбоя контролируемой информации, останавливает подачу импульсов синхронизации с контролируемого объекта на тактовый вход 21, а также свидетельствует о наличии неустойчивого сбоя в контролируемой информации.

На выходы блока 15 индикации поступают коды с выходов второго регистра 10 и второго счетчика k, тем самым индуцируя соответственно разряды элемента и номер самого элемента информации, по которому зафиксирован неустойчивый сбой.

Формула изобретения

Устройство для1 фиксации неустойчивых сбоев, содержащее первый и второй элементы И, первый и второй регистры, первый, второй и третий счетчики, элемент ИЛИ-НЕ, первый и второй блоки сравнения, блок индикации, элемент ИЛИ и первый триггер,, причем вход запуска цикла контроля устройства соединен с первым входом первого элемента И, второй вход которого соединен с выходом первого триггера, а выход первого элемента И соединен со счетным входом первого счетчика, информационные выходы и выход переполнения которого соединены соответственно с входами элемента ИЛИ-НЕ и счетным входом второго счетчика, ин- формационный выход второго счетчика соединен с первым информационным входом первого блока сравнения и первым входом блока индикации, информационный выход третьего счетчика соединен с вторым информационным входом первого блока сравнения, выход равенства которого соединен с первым входом второго элемента И, второй вход и выход второго элемента И соединены со- ответственно с выходом элемента ИЛИ-НЕ и синхровходом первого регистра, выход которого соединен с первым входом второго блока сравнения, второй вход второго блока сравнения и информацион ный вход первого регистра подключены к информационному входу устройства, выход второго блока сравнения соединен с информационным входом второго регистра, выход которого соединен с вторым входом блока индикации, выход элемента ИЛИ соединен с синхровходом первого триггера, выход которого является выходом сбоя устройства, тактовый вход устройства соединен со счетным входом третьего счетчика, вход начальной установки устройства соединен с входами сброса второго регистра, второго и третьего счетчиков, входом установки первого счетчика и входом установки в единичное состояние третьего триггера, отличающееся тем, что, с целью повышения достоверности фиксации неустойчи- ых сбоев, в устройство введены эле-

мент НЕ, третий элемент И, третий регистр, третий блок сравнения, второй и третий триггеры, причем вход элемента НЕ соединен с выходом элемента ИЛИ-НЕ, а выход элемента НЕ - с синхровходом третьего регистра, с синхровходом третьего триггера и вторым входом третьего элемента И, первый вход и выход трет ьего элемента И соединены соответственно с выходом равенства первого блока сравнения и синхровходом второго регистра, информационный вход и выход третьего регистра соединены соответственно с выходом третьего счетчика и первым информационным входом третьего блока сравнения, второй информационный вход и вход разрешения которого соединены соответственно с выходом второго счетчика и входом запуска цикла контроля устройства, выход равенства третьего блока сравнения соединен с входом установки в единичное состояние третьего триггера, прямой выход которого соединен с информационным входом и входом установки в нулевое состояние второго триггера,синхровход и инверсный вход второго триггера соединены соответственно с выходом переполнения первого счетчика и входом установки второго счетчика, входы элемента ИЛИ соединены с выходом второго регистра, вход разрешения сравнения первого блока сравнения соединен с тактовым входом устройства, вход установки третьего регистра и вход установки в нулевое состояние первого триггера соединены с входом начальной установки устройства

а а-« . |

5: )

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регистрации неустойчивых сбоев | 1986 |

|

SU1397916A1 |

| Устройство для фиксации неустойчивых сбоев | 1983 |

|

SU1126965A1 |

| Устройство для фиксации неустойчивых сбоев | 1986 |

|

SU1388872A2 |

| Устройство для фиксации неустойчивых сбоев | 1985 |

|

SU1277117A1 |

| Устройство для фиксации неустойчивых сбоев | 1986 |

|

SU1314343A1 |

| Устройство для фиксации неустойчивых сбоев | 1985 |

|

SU1265777A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для фиксации неустойчивых сбоев | 1986 |

|

SU1392567A1 |

| Устройство для контроля аналогового сигнала | 1990 |

|

SU1797097A1 |

| Устройство для измерения параметра динамического процесса и управления им с самоконтролем | 1986 |

|

SU1423985A1 |

Изобретение относится к области вычислительной техники и может быть использовано для фиксации неустойчивых сбоев в процессе циклической работы цифровых объектов исследования. Цель изобретения - повышение достоверности фиксации неустойчивых сбоев. Указанная цель достигается тем, что в устройство, содержащее первый 1 и второй 12 элементы И, первый 2 и второй 10 регистры, первый 3, второй 4 и третий 5 счетчики, элемент ИЛИ-НЕ 6, первый 7 и второй 8 блоки сравнения, элемент ИЛИ 16, первый триггер 18 и блок 15 индикации, введены третий регистр 9, третий элемент И 11, третий блок 13 сравнения, элемент НЕ 14, второй 17 и третий 19 триггеры с соответствующими связями. Возврат к контролю первого элемента последовательности после контроля последнего элемента позволяет в отличие от прототипа исключить "холостые" циклы (т.е.циклы, при которых контроля не происходит) при контроле последовательностей, имеющих длину L меньше максимальной 2N-1, где N - разрядность второго счетчика 4, что ведет к увеличению частоты контроля каждого элемента. 2 ил.

| Устройство для поиска перемежающихся неисправностей | 1979 |

|

SU920732A1 |

| Устройство для фиксации неустойчивых сбоев | 1983 |

|

SU1126965A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-02-07—Публикация

1988-05-25—Подача