22

(Л

00

:о

со

35

дить предысторию его возникновения. Счетчик 3 определяет номер текущего байта информации многократно воспроизводимой на входе устройства контролируемой последовательности, счетчик 5 отсчитывает количество циклов контроля, счетчик А указывает на номер исследуемого байта, элемент 9 идентифицирует 1Ц1кл контроля, узел 8 и элемент 11 выделяют такт появления в последовательности исследуемого байта для сравнения его значения посредством узла 7 со значением, записанным в регистр 2 на первом цикле контроля. При несовпадении сравниваемых значений регистром 12, бло97916

ком 14 и триггерами 15 и 16 фиксируется неустойчивый сбой. До фиксации неустойчивого сбоя в блоке 10 через регистр 1 записываются байты последовательности. Обращение к блоку 10 осуществляется посредством регистра 6 и счетчика 3 по циклически повторяемой последовательности адресов, что обеспечивает поддержание в блоке 10 последних байтов последовательности. С момента фиксации неустойчивого сбоя блок 10 переходит в режим чтения и через регистр 13 передает на выход циклически повторяемую предысторию возникновения неустойчивого сбоя. 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для фиксации неустойчивых сбоев | 1985 |

|

SU1277117A1 |

| Устройство для фиксации неустойчивых сбоев | 1986 |

|

SU1388872A2 |

| Устройство для фиксации неустойчивых сбоев | 1983 |

|

SU1126965A1 |

| Устройство для фиксации неустойчивых сбоев | 1988 |

|

SU1541612A1 |

| Устройство для фиксации неустойчивых сбоев | 1985 |

|

SU1265777A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1990 |

|

SU1732380A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для фиксации неустойчивых сбоев | 1986 |

|

SU1314343A1 |

| Устройство для задержки цифровой информации | 1986 |

|

SU1383325A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

Изобретение относится к автоматике и вычислительной технике и м.б, использовано в системах контроля . Цель изобретения - повышение информативности о регистрируемой информации. Устройство содержит регистры 1,2,12,13, счетчики 3-5, узлы сравнения 7,8, элемент ИЛИ-НЕ 9, блок памяти 10, элемент И 11,17, блок индикации 14, триггеры 15,16. Устройство позволяет обнаруживать неустой- чивьЕЙ сбой и многократно воспроизво

Изобретение относится к вычислительной технике.

Цель изобретения - повышение информативности о регистрируемой информации.

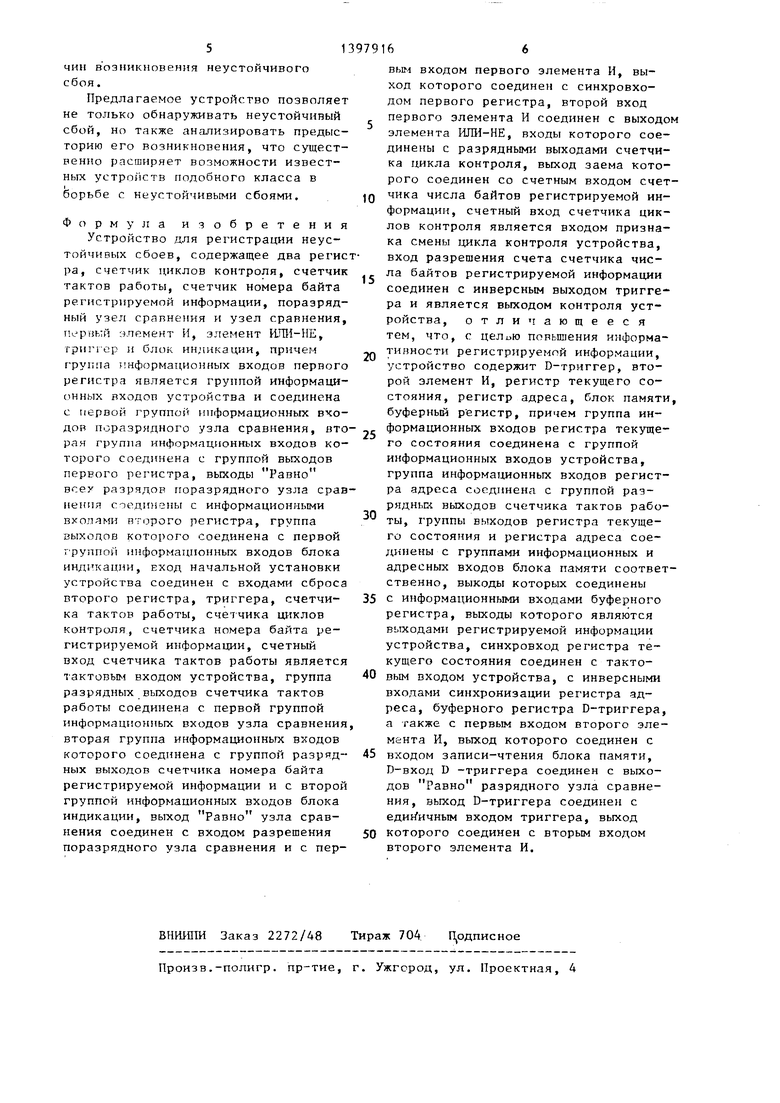

На чертеже показано предлагаемое устройство.

Устройх:тво содержит регистр 1 текущего состояния, регистр 2, счетчик 3 тактов работы, счетчик 4 номера бай та регистрируемой информации, счетчик 5 цикла контроля,- регистр 6 адреса, поразрядный узел 7 сравнения, узел 8 сравнения, элемент 11ЛИ-НЕ 9, блок 10 памяти, элемент И 11, регистр 12, буферный регистр 13, блок 1А индикации, D-триггер 15, триггер 16, элемент И 17, группу информационных входов 18 устройства, тактовый вход 19 устройства, вход 20 признака цик- ла контроля, вход 21 начальной установки устройства, выходы 22 регистрируемой информации и выход 23 контроля устройства.

Устройство работает следующим об- разом.

На вход 21 поступает сигнал, устанавливающий счетчики 3-5, регистр 12 и триггер 16 в нулевые состояния.

На вход 20 поступает сигнал А, указывающий на начало очередного цикла контроля. В каждом цикле контроля на входы 18 поступает контролируемая п-разрядная последовательность, воспроизводимая контролируемым объектом

(не показан) по одному и тому же алгоритму. Информация поступает на входы регистра 2 и узла 7. Длительность цикла контроля определяется разрядностью счетчика 3, на счетный вход которого через вход 19 поступают синхросигналы типа меандр, по которым осуществляется поступление контролируемой информации. При этом на выходе счетчика 3 определяется номер очередной последовательности. Количество циклов контроля каждого байта информации определяется разрядностью счетчика 5, на счетный вход которого поступают сигналы А начала очередного цикла контроля.

После завершения всех циклов контроля одной информации с приходом очередного сигнала А на выходе переноса счетчика 5 вырабатывается сигнал, увеличивающий на единицу код на информационных выходах счетчика 4 Этот код указывает на номер исследуемого байта информации. Разрядность счетчика 4 равна разрядности счетчика 3, что обеспечивает возможность появления на выходах счетчика 4 последовательно номеров всех байтов информации.

Коды выходов счетчика 3 и счетчика 4 поступают на узел 8 сравнения, который при поразрядном совпадении кодов (и только в этом случае) вырабатывает -на выходе равенства сравниваемых кодов единичный сигнал В, который поступает на вход разрешения узла 7, разрешая его работу. Кроме того, сигнал В через открытый элемен И 11 поступает на синхровход регистра 2, обеспечивая прием информации в регистр 2 на первом цикле контроля

Первый цикл контроля идентифицируется при помощи элемента ИЛИ-НЕ 9, который выдает на вход элемента И 11 единичное значение при нулевом коде на разрядных выходах счетчика 5.

Таким образом, в регистр 2 записывается информация только в первом цикле контроля, причем информация с номером, указываемым счетчиком 4. Узел 7 сравнения выполняет функцию сравнения только при подаче на его входы информации с одинаковыми номерами, причем с выхода регистра 2 снимаются данные, записанные в него в первом цикле контроля. Узел 7 сравнения осуществляют поразрядное сравнение и при полном совпадении (и только в этом случае) вырабатывает нулевой код сравнения, поступающий на информационный вход регистра 12, а также общий сигнал сравнения, являющийся объединением по ИЛИ разрядов кода сравнения и снимаемый с выхода равенства сравниваемых кодов.

Сигнал сравнения в случае несовпадения сравниваемых кодов принимает единичное значение. Этот сигнал и код сравнения по окончании первого полутакта каждого такта записываются соответственно в триггер 15 и регистр 12, причем запись осуществляется по синхросигналам, поступающим на их инверсные синхровходы через тактовый вход 19 устройства непосредственно и через элемент И 17. С выхода триггера 15 единичный сигнал поступает далее на единичный вход триггера 16, устанавливая его в единичное состояние. Это состояние соответствует регистрации неустойчивого сбоя. Сигнал с инверсного выхода триггера 16 поступает на сигнальный выход 23 контроля устройства и на вход элемента И 17. В случае регистрации неустойчивого сбоя, нулевой сигнал с инверсного выхода триггера 16 останавливает счет счетчика 5 и связанного с ним счетчика 4. Кроме того, устанавливается в ноль выход элемента И 17, что препятствует прохождению через этот -элемент синхросигналов с тактового входа 19 на

синхронход регистра 12 и выход запись-чтение блока 10 памяти. Код номера элемента с выхода счетчика 4 и код сравнения с выхода регистра 12 поступают на входы блока 14 индикации для указания номера и разряда сбойного байта информации.

Контролируемая информация поступает через вход 19 устройства также на вход регистра 1, в который принимается по синхросигналам, поступающим на его синхровход с входа 19. Эти же синхр.осигналы подаются также на синхровход регистра 13 и инверсный синхровход регистра 6 адреса. При этом в регистр 6 в конце полутакта каждого такта принимается код С м-чадших разрядов с выхода счетчика 3 тактоз.

Этот код принимает в цикле последовательно значения от 0-до 2-1, обеспечивая обращение к блоку Ю соответ- ственно по адресам от О до 2 -1. Синхросигналы, поступающие до регистрации неустойчивого сбоя на вход запись-чтение блока 10 с выхода элемента И 17, обеспечивают режим записи в первом полутакте и режим чтения во втором полутакте каждого такта

(режим чтения обеспечивается уровнем логического нуля). Считываемая из блока 10 информация принимается в каждом такте в регистр 13 и далее с его выхода поступает на выход 22.

Таким образом по каждому адресу, который держится вторую половину одного такта и первую половину следующего за ним такта, сначала происходит считывание информации по окончании

такта, а затем в течение первого полутакта следующего такта - запись новой информации с выхода регистра 1, Поскольку обращение к накопителю по одному и, тому же адресу происходит

раз в 2 тактов, то считывается из блока 10 и подается через регистр 13 на выход 22 информация, записанная в 2 тактов тому назад. (В случае регистрации неустойчивого сбоя

выход элемента И 1 устанавливается в ноль и обеспечивает для блока 10 работу только в режиме чтения). При этом на выход 22 поступает повторяемая в цикле последовательность 2

байтов информации, содержащая сбойный байт и 2 -1 предшествующих ему байтов. Указанная последовательность может быть исследована, например, с помощью осциллографа на предмет при513

чин возникновения неустойчивого сбоя.

Предлагаемое устройство позволяет не только обнаруживать неустойчивый сбой, но также анализировать предысторию его возникновения, что существенно расширяет возможности известных устройств подобного класса в борьбе с неустойчивыми сбоями.

Формула изобретения

Устройство /для регистрации неустойчивых сбоев, содержащее два регисра, счетчик циклов контроля, счетчик тактов работы, счетчик номера байта регистрируемой информации, поразрядный узел сравнения и узел сравнения, первый элемент И, элемент ИПН-НЕ, григг ср и блок ин,чикации, причем группа информационных входов первого регистра является группой информаци- с нных входоп устройства и соединена с первой группой ипформационных входов поразрядного узла сравнения, вторая группа информационных входов которого соединена с группой выходов первого регистра, выходы Равно всех разрядов поразрядного узла сравнения саеди} аны с информационными вхолами второго регистра, группа выходов которого соединена с первой г руппой информационных входов блока индг кацни, Еход начальной установки устройства соединен с входами сброса второго регистра, триггера, счетчика тактов работы, сче тчика циклов контроля, счетчика номера байта регистрируемой информации, счетный вход счетчика тактов работы является тактовьм входом устройства, группа разрядных выходов счетчика тактов работы соединена с первой группой информационных входов узла сравнения вторая группа информационных входов которого соединена с группой разрядных выходов счетчика номера байта регистрируемой информации и с второй группой информационных входов блока индикации, выход Равно узла сравнения соединен с входом разрешения поразрядного узла сравнения и с пер

5

0

5

0

вым входом первого элемента И, выход которого соединен с синхровхо- дом первого регистра, второй вход первого элемента И соединен с выходом элемента ИЛИ-НЕ, входы которого соединены с разрядными выходами счетчика цикла контроля, выход заема которого соединен со счетным входом счетчика числа байтов регистрируемой информации, счетный вход счетчика циклов контроля является входом признака смены и;икла контроля устройства, вход разрешения счета счетчика числа байтов регистрируемой информации соединен с инверсным выходом триггера и является выходом контроля устройства, отличающе еся тем, что, с целоЮ повышения информативности регистрируемой информации, устройство содержит D-триггер, второй элемент И, регистр текущего состояния, регистр адреса, блок памяти, буферный р егистр, причем группа информационных входов регистра текущего состояния соединена с группой информационных входов устройства, группа информаи1ионных входов регистра адреса соединена с группой раз- рядньк выходов счетчика тактов работы, группы выходов регистра текущего состояния и регистра адреса соединены с группами информационных и адресных входов блока памяти соответ

с информационными входами буферного регистра, выходы которого являются выходами регистрируемой информации устройства, синхровход регистра текущего состояния соединен с тактовым входом устройства, с инверсными входами синхронизации регистра адреса, буферного регистра D-триггера, а также с первым входом второго элемента И, выход которого соединен с входом записи-чтения блока памяти, D-вход D -триггера соединен с выходов Равно разрядного узла сравне

ния, выход D-триггера соединен с единичным входом триггера, выход которого соединен с вторым входом второго элемента И.

| Устройство для поиска перемежающихся неисправностей | 1979 |

|

SU920732A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для фиксации неустойчивых сбоев | 1983 |

|

SU1126965A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-05-23—Публикация

1986-07-07—Подача